# 法政大学学術機関リポジトリ

# HOSEI UNIVERSITY REPOSITORY

PDF issue: 2024-12-21

# 化合物半導体デバイスプロセスの研究

太田, 博 / Ohta, Hiroshi

```

(開始ページ / Start Page)

1

(終了ページ / End Page)

197

(発行年 / Year)

2018-03-24

(学位授与番号 / Degree Number)

32675乙第230号

(学位授与年月日 / Date of Granted)

2018-03-24

(学位名 / Degree Name)

博士(工学)

(学位授与機関 / Degree Grantor)

法政大学 (Hosei University)

(URL)

https://doi.org/10.15002/00014769

```

# 法政大学審査学位論文

化合物半導体デバイスプロセスの研究

太田 博

#### 要旨

本論文は、化合物半導体を用いた高速デバイスおよびパワーデバイスのデバイスプロセスの研究について述べたものである。

高速デバイスとしては、自動車衝突防止用車載レーダ向け GaAs 系のオフセットゲート P-HEMT のデバイスプロセス技術の開発を行い特性を評価した。その結果、ゲート・ドレイン間容量の低減により最大発信周波数 fmax=170GHz が得られた。また、シミュレーションにより求めた最大有能電力利得

(Maximum Available Gain: MAG) は、周波数  $77 \mathrm{GHz}$  において  $9.2 \mathrm{dB}$  となった。同デバイスを適用した 3 段パワーアンプでは周波数  $77 \mathrm{GHz}$  において小信号利得  $16.5 \mathrm{dB}$  が得られ、簡易寿命試験では、試料温度  $175 ^{\circ}$  で測定時間  $160 \mathrm{hr}$  においても小信号利得の減少は見られず、車載レーダ実用化への道を開いた。

パワーデバイスとしては、パワーコントロールユニットで使用されるコンバーターやインバーター向け GaN 系 p·n ダイオードに着目した。まずは、ダイオード作製プロセスの改善をおこない、低ダメージな GaN エッチング技術等を開発し特性向上を果たした。続いて、デバイス構造の開発として、ガードリング構造 p·n ダイオードや p·GaN 層薄層化 p·n ダイオードの提案を行い、約200V の逆方向耐圧向上に成功し、高耐圧仕様の p·n ダイオードでは逆方向耐圧 5kV を達成した。また、逆方向電圧印加時に p·GaN 層が全空乏化することで発生するパンチスルー現象を利用して、降伏後も破壊が生じない可逆性を有するダイオードを開発した。同じくデバイス構造の開発として、櫛形構造 p·n ダイオードにおいて順方向電流 20%の向上を達成した。

# 目次

| 第1章    | 序論                                              | 6  |

|--------|-------------------------------------------------|----|

| 1.1 研  | 究の背景                                            | 6  |

| 1.2 研  | 究の目的                                            | 9  |

| 1.2.1  | 超高速化合物半導体デバイスプロセス                               | 9  |

| 1.2.2  | パワー半導体デバイスプロセス                                  | 11 |

| 1.3 研  | 究の概要                                            | 16 |

| 第2章    | 超高速化合物半導体デバイスプロセス                               | 18 |

| 2.1 は  | じめに                                             | 18 |

| 2.2 高气 | 電子移動度トランジスタ(HEMT)                               | 19 |

| 2.2.1  | HEMT の動作原理                                      | 19 |

| 2.2.2  | AlGaAs/GaAs 系 HEMT                              | 21 |

| 2.2.3  | ダブルヘテロ構造 HEMT                                   | 24 |

| 2.2.4  | シュードモルフィック HEMT (P-HEMT)                        | 27 |

| 2.3 才  | フセットゲート構造 HEMT                                  | 29 |

| 2.3.1  | 寄生成分の HEMT 性能への影響                               | 29 |

| 2.3.2  | オフセットゲート HEMT の提案                               | 33 |

| 2.3.3  | オフセットゲート <b>P-HEMT</b> の構造                      | 35 |

| 2.4 才  | フセットゲート P-HEMT 作製プロセスフロー                        | 38 |

| 2.5 才  | フセットゲート <b>P-HEMT</b> 特性評価結果                    | 43 |

| 2.5.1  | DC 特性評価結果                                       | 43 |

| 2.5.2  | RF 特性評価結果                                       | 45 |

| 2.6 ₹  | リ波レーダー用 Monolithic Microwave Integrated Circuit | 48 |

| 2.6.1  | Monolithic Microwave Integrated Circuit の構造     | 48 |

| 2.6.2  | 3 段パワーアンプ特性評価結果                                 | 50 |

| 2.7 ま   | とめ                               | 52  |

|---------|----------------------------------|-----|

| 第3章     | パワー半導体デバイスプロセス                   | 53  |

| 3.1 は   | じめに                              | 53  |

| 3.2 p-1 | n ダイオード断面構造                      | 54  |

| 3.3 p-1 | n ダイオード作製プロセスフロー                 | 55  |

| 3.4 =   | ンタクトホール加工のドライエッチング化              | 57  |

| 3.5 メ   | サエッチング時のドライエッチングダメージ低減           | 62  |

| 3.5.1   | 3 層マスク構造によるドライエッチングダメージ低減        | 63  |

| 3.5.2   | ドライエッチングダメージのアニールによる回復           | 67  |

| 3.5.3   | 低パワードライエッチングによるダメージ低減            | 72  |

| 3.6 ま   | とめ                               | 74  |

| 第4章     | パワー半導体デバイスの高耐圧化                  | 75  |

| 4.1 は   | じめに                              | 75  |

| 4.2     | ルチドリフト層構造 p-n ダイオード              | 76  |

| 4.2.1   | p-n ダイオード空乏層中の電界分布               | 76  |

| 4.2.2   | マルチドリフト層構造 p-n ダイオードの電界分布        | 80  |

| 4.2.3   | マルチドリフト層構造 p-n ダイオード特性評価結果       | 83  |

| 4.3 ガ   | ードリング構造による p-n ダイオードの高耐圧化        | 89  |

| 4.3.1   | ガードリング構造 p-n ダイオード               | 90  |

| 4.3.2   | ガードリング構造 p-n ダイオードの作製プロセスフロー     | 96  |

| 4.3.3   | 抵抗素子の I-V 特性                     | 98  |

| 4.3.4   | ガードリング部分とメイン p-n ダイオード部分間の電圧降下   | 100 |

| 4.3.5   | ガードリング構造 p-n ダイオードの抵抗素子幅依存性評価結果  | 103 |

| 4.3.6   | 高耐圧仕様結晶を用いたガードリング構造 p-n ダイオードの評価 | 106 |

| 4.4 パ   | ンチスルー現象を利用した可逆性 p-n ダイオードの作製     | 110 |

| 4.4 | 1 p-n ダイオードのアバランシェ降伏                       | 110 |

|-----|--------------------------------------------|-----|

| 4.4 | 2 パンチスルー現象                                 | 113 |

| 4.4 | 3 逆方向 I-V 特性の温度依存性                         | 115 |

| 4.4 | 4 逆方向 I-V 特性の温度依存性評価結果                     | 115 |

| 4.4 | 5 髙耐圧仕様可逆性 p-n ダイオードの検討                    | 119 |

| 4.5 | 高抵抗 p-GaN 層を持つ高耐圧 p-n ダイオード                | 128 |

| 4.5 | 5.1 p-GaN 層の高抵抗化による高耐圧化                    | 128 |

| 4.5 | 5.2 p-GaN 層の薄層化による高抵抗化                     | 130 |

| 4.5 | .3 p-GaN 層薄層化 p-n ダイオードの作製プロセスフロー          | 132 |

| 4.5 | .4 空乏化した p-GaN 層の I-V 特性評価結果               | 133 |

| 4.5 | .5 p-GaN 層薄層化 p-n ダイオードの特性評価結果             | 135 |

| 4.5 | 6.6 p-GaN 層薄層化 p-n ダイオードと可逆性 p-n ダイオードの関係性 | 139 |

| 4.6 | まとめ                                        | 140 |

| 第5章 | パワー半導体デバイスの大電流化                            | 142 |

| 5.1 | はじめに                                       | 142 |

| 5.2 | 電流密度の p 形電極面積依存性                           | 143 |

| 5.3 | フォトンリサイクリング現象                              | 145 |

| 5.4 | p 形電極内電流分布                                 | 147 |

| 5.5 | 櫛形電極構造による大電流化                              | 155 |

| 5.6 | p 形電極横方向抵抗の影響による電極周辺部分の電圧降下                | 158 |

| 5.7 | まとめ                                        | 161 |

| 第6章 | 結論                                         | 162 |

| 6.1 | 結言                                         | 162 |

| 6.1 | 今後の課題                                      | 165 |

| 参考文 | 献                                          | 167 |

| 謝辞            | 180 |

|---------------|-----|

| 研究業績一覧        | 182 |

| 学術論文(査読有)     | 182 |

| 国際会議(論文有)     | 186 |

| 国際会議(論文無)     | 189 |

| 学術講演会論文等(査読無) | 190 |

| 解説記事等         | 194 |

| <b>特</b> 許    | 195 |

#### 第1章 序論

# 1.1 研究の背景

半導体デバイス(トランジスタ)の歴史は、1948年のW.ショックレー氏らにより発明された点接触型トランジスタやサンドイッチ型トランジスタによりその扉が大きく開かれた [1・2]。当初トランジスタは Ge により作製されていたが、Ge 自体の熱的不安定さから、その中心は Si に置き換わられた。Si はその熱的安定性のみならず、微量の不純物添加により容易に n 形化、p 形化が可能であること、安定かつ良質な酸化膜が容易に形成できる事など非常に優れた特徴を有し、さらに原料が地球上に豊富に存在するため入手が容易であることから、Si を用いたデバイスは様々な用途で爆発的に普及した [3・6]。しかし、半導体デバイス高性能化の要求は衰えることを知らず、やがて Si では物性的に達成困難なレベルまで高まってきている。そこで、より高い物性値を持つ半導体材料が求められ、化合物半導体に注目が集まった。表 1.1 に主な半導体の物性値を示す。

化合物半導体とは、Ⅱ族とⅥ族、またはⅢ族とⅤ族、あるいは異なるⅣ族の原子2種もしくは3種以上を結合して形成され、その組み合わせにより移動度やバンドギャップ等を比較的自由に変化することが可能であり、Si に比べ優れた物性を発現させることが出来る。また、半導体デバイスの用途は、高速デバイス、光デバイス、パワーデバイスに代表されるが、それぞれの用途毎に必要とされる物性値は異なり、化合物半導体の物性設計の自由度の高さを利用し、それぞれの用途に対応した特性を持たせることも可能であり、各用途に応じた最適な材料の適用が検討されている[7]。

高速デバイスの開発で当初最も注目を集めたのは GaAs である [8]。GaAs は高移動度、半絶縁性基板の作製が容易等の特徴を有し [9]、AlGaAs とのヘテロ接合を利用した高電子移動度トランジスタ (HEMT) [10-11]においては、その

2 次元電子ガス層における電子移動度は、低温領域では  $50000 \text{cm}^2/\text{Vs}$  や  $10^7 \text{cm}^2/\text{Vs}$  という高い値を示すという報告もある [12-13]。その後、より高周波特性に優れた InGaAs/InP を用いたデバイスの検討も盛んに行われた [14-17]。

表 1.1 主な半導体の物性値

|          | バンドギャップ<br>(eV) | 遷移型 | 電子移動度<br>300K (cm²/Vs) | 飽和電子速度<br>10 <sup>7</sup> (cm/s) | 絶縁破壊電界<br>(MV/cm) |

|----------|-----------------|-----|------------------------|----------------------------------|-------------------|

| Si       | 1.11            | 間接  | 1500                   | 1.0                              | 0.3               |

| GaP      | 2.26            | 間接  | 250                    |                                  |                   |

| GaAs     | 1.43            | 直接  | 8500                   | 2.0                              | 0.4               |

| AlAs     | 2.12            | 間接  | 1000                   |                                  |                   |

| InAs     | 0.36            | 直接  | 22600                  |                                  |                   |

| InP      | 1.34            | 直接  | 5400                   | 2.5                              | 0.5               |

| GaN      | 3.39            | 直接  | 1200                   | 2.5                              | 3.3               |

| SiC (4H) | 3.26            | 間接  | 1000                   | 2.0                              | 3.0               |

光デバイスとしては、それぞれバンドギャップが異なる GaN、AlN、InN 等が検討されている [18-22]。2014年 GaN 系の青色発光ダイオードの研究で名古屋大学天野教授らがノーベル物理学賞を受賞している。表 1.2 に主な半導体材料と発光色を示す。

パワーデバイスでは、SiC や GaN が注目されている。これらの半導体は、絶縁破壊耐圧が Si の 10 倍以上と高く、高耐圧化、低オン抵抗化が可能であり、

またバンドギャップも大きいため、高温下での動作が可能であるという特徴を有する。特に GaN は究極のパワーデバイスと呼ばれており、今後増々需要は高まると考えられる。

以上述べたように、化合物半導体を用いたデバイスは高い性能を示し、その 構成組み合わせを工夫すること等で、今後もより高い性能を達成できる潜在能 力を有していると考えられる。しかし、Si に比べ原料の入手が困難なことか ら、低価格化が困難であることが普及の妨げとなっている。いかに低価格化を 行うかが普及に向けた最大の課題と言える。

表 1.2 半導体材料と発光色

| 半導体材料     | 発光色   |

|-----------|-------|

| AlGaN/GaN | 紫外    |

| InGaN/GaN | 紫・青・緑 |

| GaP       | 緑     |

| AlInGaP   | 黄     |

| GaAlAs    | 赤     |

| GaAlAs    | 赤外    |

| InGaAs    | 近赤外   |

#### 1.2 研究の目的

本研究は、半導体デバイスの用途として高速デバイスおよびパワーデバイス の開発を目的とした。以下それぞれについてより詳細に説明する。

## 1.2.1 超高速化合物半導体デバイスプロセス

ドライバーや歩行者等の安全確保を目的とし、自動車の衝突防止システムの開発が盛んにおこなわれている。衝突防止システムに用いられるセンサーは様々な種類が検討、開発されているが、その一つとしてミリ波レーダーが挙げられる。ミリ波とは、波長が1~10mm程度で、周波数が30G~300GHzの電波であり、ミリ波レーダーには60GHz帯、76GHz帯、79GHz帯が割り当てられている[23]。ミリ波は、直進性が強く測定可能距離が大きい、昼夜の性能差が小さい、雨や霧・逆光等天候の影響も受けにくいといった長所を有する反面、歩行者や自転車等小さな対象物の検知能力が弱いといった短所を有している。しかし、近年そのような短所が克服されつつあり、2眼式のカメラと並用したミリ波レーダーが衝突防止システムのセンサーとして主流となりつつある。

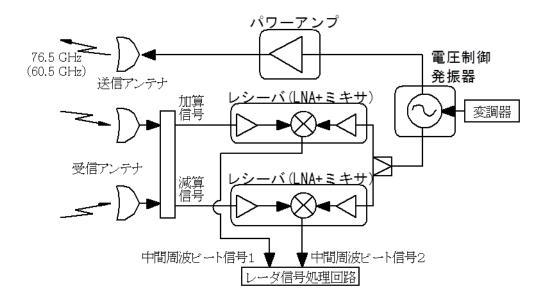

図 1.1 にミリ波車載レーダーの構成概略図を示す。ミリ波車載レーダーは、パワーアンプ、レシーバー(ローノイズアンプ+ミキサ)、発振器等で構成されている。これらは主に、同一半導体基板上に回路素子を配置した Monolithic Microwave Integrated Circuit (MMIC)として開発が進められている [24-26]。 MMIC の主要素子としては半導体デバイスが用いられている。 MMIC の高性能化には半導体デバイスの高性能化が必須であり、本研究は、半導体デバイスとしてダブルヘテロ構造 AlGaAs/InGaAs/GaAs High Electron Mobility Transistor (HEMT) を用い、その高性能化のためのオフセットゲート構造形成プロセス技術の開発および特性評価を目的とした。また、ミリ波車載レーダーの構成部品

としてパワーアンプに着目し、同 HEMT を適用したパワーアンプの特性評価の 実施も目的とした。

図1.1 車載レーダ構成概略図

# 1.2.2 パワー半導体デバイスプロセス

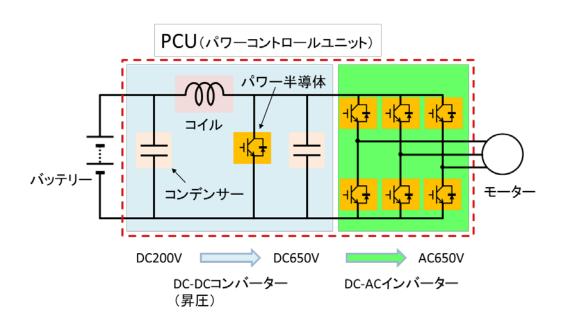

我々の身近には様々な電化製品が存在している。それらの電化製品の定格電圧は、100~200Vの比較的低電圧なものから数 kV の高電圧なものまで存在する。また、定格電流も 1A 程度の低電流なものから 1kA を超える大電流なものまで様々である。これらの電化製品には DC-AC、あるいは AC-AC 変換用のコンバーターやインバーターが搭載されており、そのコンバーターやインバーターには半導体デバイスが使用されている。このように主に電源部分で用いられる半導体デバイスは特にパワー半導体デバイスと呼ばれており、使用される電圧、電流共に大きくなることが想定されるため、高耐圧化、大電流化が強く要求されている。また、コンバーターやインバーターが搭載されたパワーコントロールユニット (PCU) は小型化が重要である。PCU を構成するコイルやコンデンサーはPCU 全体の約 4 割程度の体積を占めることから、PCU 小型化のためにはコイルやコンデンサーの小型化が必須である。PCU の制御を高周波化することでコイルやコンデンサーの小型化が可能であることから、パワー半導体デバイスは高周波動作特性も同時に求められている。

当初パワー半導体デバイスは Si デバイスが適用されていたが、より高性能な デバイス特性の要求に対し、Si デバイスでは物性的に困難な状況になりつつある。そこで化合物半導体を用いたデバイスへの注目が大きくなっている。化合物 半導体は Si に比べ優れた物性を有し、その組成次第で様々な用途に合った特徴 を持たせることも可能である。パワー半導体デバイス用途としては、SiC や GaN が注目されている。これらの半導体はバンドギャップが大きく、絶縁破壊電界は Si の 10 倍以上に及ぶためより高耐圧が期待できる。デバイスの耐圧はドリフト 層の長さと絶縁破壊電界の積で表されるため、仮に耐圧を同一値に設定した場合、絶縁破壊電界が Si の 10 倍以上である SiC や GaN はドリフト層の長さを 1/10 以下にすることができ、それによりオン抵抗を計算上 1/1000 にすることが 可能となる。また、高速性を表す指標である遮断周波数 (fr) はドリフト層の長

さの逆数に比例するため、上述の通りドリフト層の長さを 1/10 以下にすることが出来る SiC や GaN では、Si の 10 倍程度の周波数で使用することが可能である。加えて、SiC や GaN は電子の飽和速度も大きいため、デバイスの高速化も期待できる。

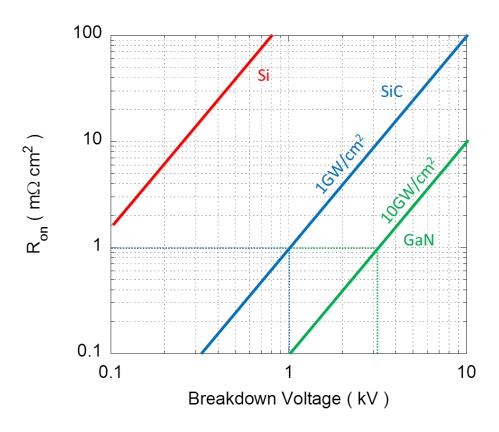

表 1.3 に、各半導体について式(1.1)で表されるパワーデバイスの性能を示すバリガの性能指数(Baliga's Figure of Merit: BFOM) [27-28]を、図 1.2 に各半導体の降伏電圧とオン抵抗の関係からみた一般的な理論限界値を示す。降伏電圧とオン抵抗の関係に関する理論限界値は式(1.2)から求めた。

$$BFOM = \varepsilon \mu E_c^{\ 3} \tag{1.1}$$

ここで、εは誘電率、μは電子移動度、Ecは絶縁破壊電界である。

$$R_{on} = \frac{4V_B^2}{\varepsilon \mu E_c^3} \tag{1.2}$$

ここで、 $R_{on}$ はオン抵抗、 $V_{B}$ は降伏電圧である。

図 1.2 の見方として例えば GaN の場合、降伏電圧が 3kV の時、オン抵抗は理論上  $1m\Omega cm^2$  まで低くすることが可能であるということを示している。SiC の場合は降伏電圧が 1kV の時オン抵抗は理論上  $1m\Omega cm^2$  まで低くすることが可能となる。

GaN は BFOM が SiC に比べても大きく、パワーデバイスとして非常に高いポテンシャルを有していることが分かる。また、SiC と比べて GaN は、AlGaN 等との間にバンド不連続を有する良好なヘテロ構造を形成できるため、

AlGaN/GaN HEMT 等低オン抵抗、高速、高耐圧デバイスの実現が可能である [29-32]。このような特徴から、GaN は究極のパワーデバイスと呼ばれており、SiC の次世代パワーデバイスとして期待されている。

表 1.3 各半導体のバリガの性能指数比較

|                       | Si | SiC (4H) | GaN |

|-----------------------|----|----------|-----|

| バリガの性能指数(Si を 1 とした時) | 1  | 565      | 857 |

図 1.3 にコンバーターおよびインバーターを用いた PCU の回路図を示す。受動素子であるコイルやコンデンサーの他、能動素子であるパワー半導体デバイス (トランジスターおよびダイオード) から構成されている。前述の通り、PCU の高性能化および小型化のためには、パワー半導体デバイスの高性能化および高周波化が必須である。本研究は、パワー半導体デバイスの中で、特にダイオードに着目し、ダイオードとして自立 GaN 基板上 p-n ダイオードを採用した。前述の通り、GaN は高耐圧化、大電流化、高速化、高周波化が期待できる材料であり、本研究ではその高耐圧化および大電流化のためのデバイス構造およびプロセス技術を開発することを目的とした。

図1.2 半導体の降伏電圧と オン抵抗の関係に関する理論限界値

図1.3 パワーコントロールユニット回路図

#### 1.3 研究の概要

本論文は6章で構成される。

第2章は超高速化合物半導体デバイスプロセスと題し、高速デバイスのデバイスプロセス検討結果について述べた。高速デバイスとして HEMT に着目し、最初にその動作原理、応用デバイス等について説明した。また、本研究の最重要テーマであるオフセットゲート構造による高性能化について、その高性能化メカニズムの説明を行った。続いて本研究で開発したオフセットゲード構造実現のためのプロセス技術について述べ、その DC および RF 特性評価結果を述べた。さらに、同 HEMT を適用した 3 段パワーアンプを作製し、その小信号利得の周波数依存性評価および簡易寿命試験を行った結果を述べた。

第3章はパワー半導体デバイスプロセスと題し、p-n ダイオードのデバイスプロセスの検討結果について述べた。まず従来のp-n ダイオードの構造および作製プロセスについて説明し、その問題点の指摘を行った。そして、その解決方法としてコンタクトホール加工のドライエッチング化、GaN エッチング時の低ダメージ化、回復アニール技術について検討を行った結果について述べた。

第4章はパワー半導体デバイスの高耐圧化と題し、p·n ダイオードの高耐圧化について述べた。この章では大きく分けてダイオード層構造の検討とデバイス構造の検討を行った。ダイオード層構造の検討については、オン抵抗の増大を最小限に抑制しつつ高耐圧化を実現できるマルチドリフトレイヤー構造の適用について述べた。加えて、パンチスルー現象を利用しアバランシェ耐量を向上した可逆性 p·n ダイオードの提案を行い、その特性評価結果について述べた。デバイス構造の検討としては、ガードリング構造ダイオードの提案を行い、同ダイオードによる耐圧向上効果について述べた。また、ガードリング構造ダイオードと同様の効果を有し面積効率の向上が期待できる p·GaN 層薄層化 p·n ダイオードの提案を行いその特性評価結果について述べた。

第5章はパワー半導体デバイスの大電流化と題し、p-n ダイオードの大電流化 について述べた。この章では円形電極構造 p-n ダイオードが有する順方向 I-V 特性における電流密度の電極面積依存性について、4つの異なる電流密度領域からなるモデルで実測値とのフィッティングを行い、フォトンリサイクリング現象による電流密度の電極面積依存性の説明の妥当性について述べた。また、フォトンリサイクリング現象を利用した大電流化のための櫛形電極構造 p-n ダイオードの提案を行い、その特性評価結果について述べた。

第6章は結論と題し、結言および今後の課題について述べた。

# 第2章 超高速化合物半導体デバイスプロセス

#### 2.1 はじめに

ミリ波車載レーダ用 MMIC に組み込まれるトランジスターはより高速動作が 求められているのは前述の通りである。これまで様々な企業、研究機関等で AlGaAs/GaAs HEMT のデバイス構造、作製プロセスの検討が行われ、高速動 作が実現されてきた [33-42]。本研究はダブルヘテロ構造を有する AlGaAs/InGaAs/GaAs HEMT において、オフセットゲート構造を適用すること で、トランジスタの有する寄生成分を改善し、さらなる高性能化を実現すること を主要な目的とし、その作製プロセス検討および特性評価を行った結果につい て述べた。

また、超高速化合物半導体デバイスに関する本研究のもう一つのテーマとして 実際にミリ波車載レーダ用 3 段パワーアンプの試作を行い、その特性評価およ び簡易寿命試験を行った結果について述べた。

### 2.2 高電子移動度トランジスタ(HEMT)

# 2.2.1 HEMT の動作原理

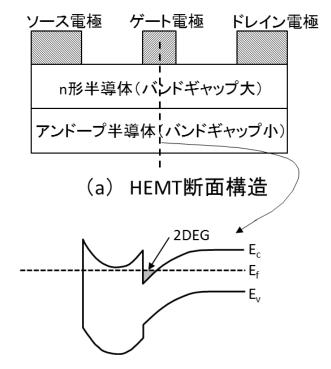

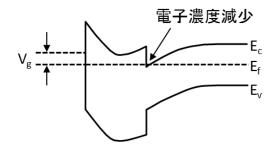

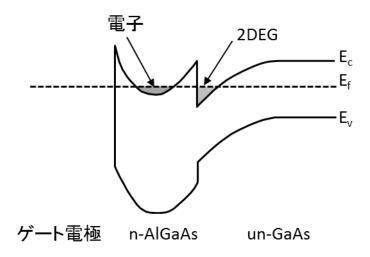

バンドギャップの異なる半導体を接合(ヘテロ接合)した場合、その界面にお いて伝導帯および価電子帯双方でバンドの不連続が発生する。図 2.1 (a) に示 すように、バンドギャップの大きい半導体を n 形とし、小さい方をアンドープ として接合し、n形半導体表面にショットキ電極を形成すると、図中の点線部分 のバンド構造は図 2.1 (b) のようになる。ショットキ電極と半導体界面で半導 体側に発生する空乏層および、ヘテロ接合界面で n 形半導体側に発生する空乏 層により、n 形半導体中の伝導帯は電子が枯渇する。一方、バンド不連続により ヘテロ接合界面付近アンドープ半導体側伝導帯でバンドのくぼみが生じ、n 形半 導体のドナー層から電子が供給され、アンドープ半導体側のそのくぼみ部分に 電子が集まる。くぼみ部分の幅はおよそ 10nm 程度と薄いため、幅方向への電 子の散乱は少なくなる。また、くぼみ部分はアンドープ半導体であるため、不純 物散乱も少ない。その結果、くぼみ部分の電子の移動度は大きくなり、高速動作 が可能となる。電子を供給する n 形半導体層は電子供給層、電子が集中するく ぼみは二次元電子ガス層(2DEG)と呼ばれている。n 形半導体表面のショット キ電極をゲート電極として電圧を印加すると、図 2.1 (c) に示すように 2DEG の電子濃度を制御することが可能となる。このように高移動度の二次元電子ガ ス層をチャネルとした電界効果型トランジスタを高電子移動度トランジスタ (HEMT)と言い、1979年に富士通研究所の三村氏らによって発明された [10]。

ゲート電極 n形半導体 アンドープ半導体

(b) HEMTバンド構造(V<sub>g</sub> = 0) V<sub>g</sub>:ゲート電圧

ゲート電極 n形半導体 アンドープ半導体

(c) HEMTバンド構造 ( $V_g$  < 0)  $V_g$ : ゲート電圧

図2.1 HEMT構造図

#### 2.2.2 AIGaAs/GaAs 系 HEMT

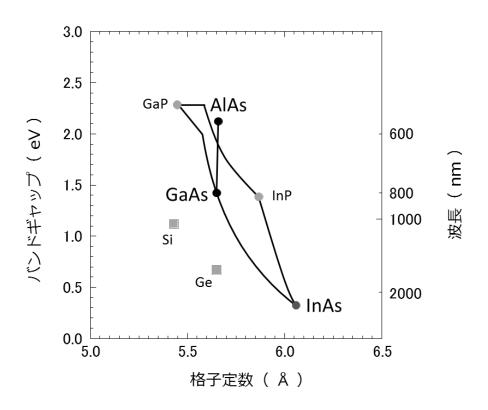

GaAs は関亜鉛鉱型の結晶で、バンドギャップは  $1.43 \mathrm{eV}$ 、格子定数は  $5.653 \, \mathrm{A}$  である。一方、AlAs も関亜鉛鉱型の結晶で、バンドギャップは  $2.12 \mathrm{eV}$  であるが、格子定数は  $5.6611 \, \mathrm{Ab}$  と GaAs に非常に近い値である。化合物半導体においては、一般的に格子定数が大きくなるとバンドギャップは小さくなる傾向にあるが、GaAs と AlAs の関係はその例外である。格子定数がほぼ等しいため GaAs と AlAs の接合では結晶欠陥の少ない良質なヘテロ接合が成長可能である。また、GaAs と AlAs の混晶である  $\mathrm{Al}_{x}\mathrm{Ga}_{1-x}\mathrm{As}$  は、 $\mathrm{x}$  の値を変化することで格子定数をより GaAs に近づけることが可能であり、バンドギャップを GaAs より大きくすることが可能である。このように GaAs と AlGaAs は、格子定数がほぼ等しくバンドギャップが異なるため、HEMT 構造を形成する上で非常に有用な材料である。

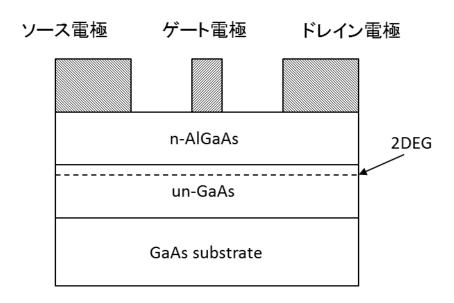

図 2.2 に主な化合物混晶半導体の格子定数とバンドギャップの関係を示す。Al の組成を少なくすることで、格子定数はより GaAs に近づくが、バンドギャップは小さくなる。HEMT では多くの場合 x の値は  $0.15\sim0.3$  が用いられる。この時のバンドギャップは  $1.6\sim1.8$ eV となる。図 2.3 に基本的な AlGaAs/GaAs HEMT の断面構造を示す。

図2.2 格子定数とバンドギャップの関係

図2.3 AlGaAs/GaAs HEMT断面構造

# 2.2.3 ダブルヘテロ構造 HEMT

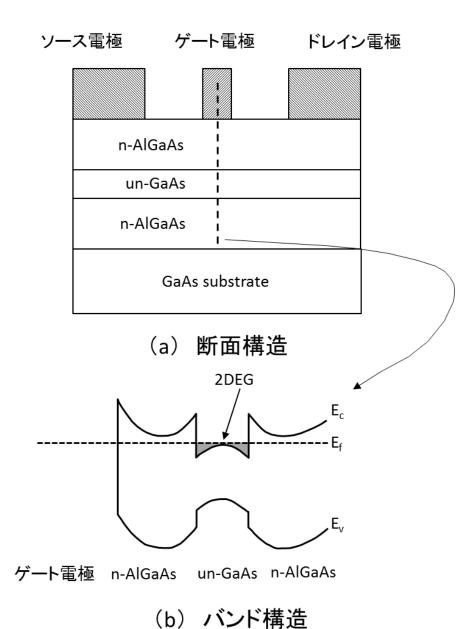

HEMT においてより大きな電流を得るためには、2DEG の電子濃度を大きくする必要がある。そのためには電子供給層である n-AlGaAs 層のドーピング濃度を大きくするのが効果的である。しかし、図 2.4 に示すように、n-AlGaAs 層のドーピング濃度を大きくすると n-AlGaAs 層の伝導帯にも電子が発生し、2DEG チャネルと並行して n-AlGaAs 層でも電流が流れる、いわゆるパラレルコンダクションが発生することがある。n-AlGaAs 層は n 形半導体であり、その移動度は 2DEG に比べ小さいため、パラレルコンダクションの発生によりデバイスの性能は劣化する。そこでパラレルコンダクションの発生を防止しつつ、2DEG の電子濃度を増加させる構造として、ダブルヘテロ構造 HEMT が考案された [43-44]。

図 2.5 (a) にダブルヘテロ構造 HEMT の基本的な断面構造を、同(b)にダブルヘテロ構造 HEMT のエネルギーバンド図を示す。図 2.5 (a) に示すように、ダブルヘテロ構造 HEMT は表面側の電子供給層 (n-AlGaAs 層) に加え、2DEGが形成される un-GaAs 層下方 (GaAs 基板側) にも電子供給層 (n-AlGaAs 層)が形成された構造となっている。図 2.5 (b) に示すように、un-GaAs 層の両側から電子が供給されるため、2DEG 層の電子濃度を 2 倍にすることも可能である。しかし、下方の電子供給層はゲート電極から離れた位置に配置されているため、そのドーピング濃度によってはピンチオフが困難となる場合があるため、それぞれの電子供給層のドーピング濃度は最適化が必要である。

図2.4 AlGaAsに高濃度のドーピングを行った時の エネルギーバンド構造 AlGaAs層伝導帯に存在する電子により 2DEGとのパラレルコンダクションが発生

図2.5 ダブルヘテロ構造HEMT断面図

### **2.2.4** シュードモルフィック HEMT (P-HEMT)

InAs は、表 1.1 に示した通り、GaAs より電子移動度が大きく、InAs をトランジスタのチャネルに適用することでより高速動作が期待できる。しかし、InAs はIII-V族化合物半導体の中では最も格子定数が大きく、格子整合が可能な基板が入手困難である。一方、GaAs との混晶である  $In_xGa_{1-x}As$  は、x の値を調整することで格子定数を変化させることが可能であり、x=0.53 の時 InP と格子整合することが知られている。InGaAs もまた x の値に応じて GaAs よりも大きな移動度を有し、InP 基板上 InGaAs HEMT は GaAs HEMT を超える高速デバイスとして広く研究開発が進められている。しかし、InP 基板は高価であり InP HEMT は費用対効果の面でまだ議論の余地が残されている。そこでより安価な GaAs 基板を用いての高速化が模索され、シュードモルフィック HEMT (Pseudomorphic-HEMT: P-HEMT) が考案された [45-47]。

図 2.6 (a) にダブルヘテロ構造 P-HEMT の基本的な断面構造を、同(b)に P-HEMT のエネルギーバンド図を示す。半絶縁性 GaAs 基板上に下側キャリア 供給層である n-AlGaAs、2DEG 層として InGaAs、上側キャリア供給層として n-AlGaAs を順次配置した構造となっている。通常 InGaAs は GaAs(AlGaAs)と格子整合しないが、xの値を  $0.1\sim0.25$  まで小さくすることで格子定数をより GaAs(AlGaAs)に近づけ、疑似的に格子整合させている。InGaAs は  $x=0.1\sim0.25$  でも GaAs に比べ電子移動度が大きく、より高速化が期待できる。また、図 2.6 (b) に示すように、InGaAs は GaAs に比べバンドギャップが小さいためより多くの電子を蓄積することが可能であり、より大きな電流が得られることも期待できる。

P-HEMT の応用として、x の値を 0.3 程度まで大きくしたメタモルフィック HEMT も検討されている [48-52]。 InGaAs の In 組成比を大きくすることで、より大きな移動度を得ることを目的としたデバイスである。x の値が大きくなると格子定数も大きくなり、GaAs との間で格子不整合が発生するが、結晶成長時の条件を最適化することで格子不整合による転位の発生を抑制し、高速化を実現している。

図2.6 シュードモルフィックHEMT断面図

### 2.3 オフセットゲート構造 HEMT

### 2.3.1 寄生成分の HEMT 性能への影響

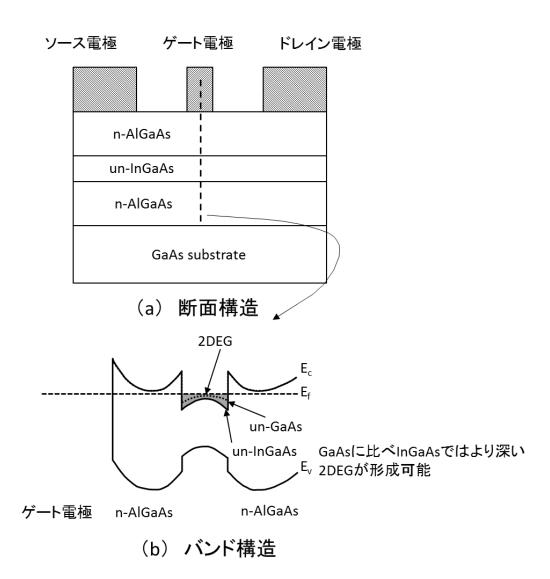

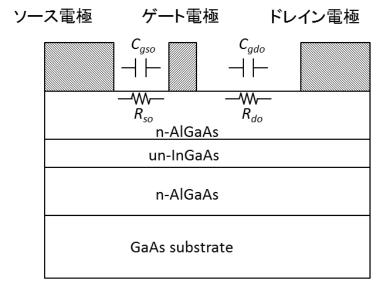

図 2.7 に HEMT の小信号等価回路を示す。ここで  $R_g$  はゲート抵抗、 $R_d$  はドレイン抵抗、 $R_s$  はソース抵抗、 $R_i$  はゲート空乏層下の半導体直列抵抗、 $L_g$  はゲートインダクタンス、 $L_d$  はドレインインダクタンス、 $L_s$  はソースインダクタンス、 $L_s$  はドレインスクタンス、 $L_g$  はゲート・ドレイン間容量、 $C_{gs}$  はゲート・ソース間容量、 $C_{ds}$  はドレイン・ソース間容量、 $C_{m}$  は相互コンダクタンス、 $C_{gd}$  はドレインコンダクタンス、 $C_{gd}$  はドレインコンダクタンスである。同回路から最大有能電力利得 (Maximum Available Gain: MAG) は次式で計算される [53]。

MAG

$$= \frac{\left(\frac{f_{T}}{f}\right)^{2}}{4g_{d}\left(R_{i} + R_{s} + R_{g} + \frac{2\pi f_{T}L_{s}}{2}\right) + 4\pi f_{T}C_{gd}\left(R_{i} + R_{texts} + 2R_{g} + 2\pi f_{T}L_{s}\right)} \quad (2.1)$$

$$\cong \frac{\left(\frac{f_{\rm T}}{f}\right)^2}{4R_{\rm s}(g_{\rm d} + \pi f_{\rm T}C_{\rm gd})} \tag{2.1}$$

ここで fr は遮断周波数で、次式で表される。

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi (C_{\rm gs} + C_{\rm gd})} \tag{2.2}$$

各パラメータが MAG にどの程度影響を及ぼすか、その感度(k) について次式を用いて評価した。

$$k = \frac{G_A(+20\%) - G_A}{G_A} \times 100\%$$

(2.3)

ここで  $G_A$ は、実際のデバイス測定結果から(2.1)式を用いて計算した MAGの値、 $G_A$ (+20%)は同測定結果の内一つのパラメータを 20%増加した時の MAGの計算値である。k の絶対値が大きいほどそのパラメータが MAG に与える影響が大きいことを示している。

表 2.1 に各パラメータが MAG に与える影響を評価した結果を示す。表より、 $C_{gs}$ 、 $C_{gd}$ 、 $g_m$ 、 $R_s$  の影響が大きいことがわかる。特に  $g_m$  と  $C_{gd}$  の影響が大きく、 $g_m$  を向上させることと、 $C_{gd}$  を低減させることが重要である。

図2.7 HEMTの小信号等価回路

表 2.1 HEMT における各パラメータの MAG への影響感度

| パラメータ                      | 感度:k(%) |

|----------------------------|---------|

| $\mathrm{C}_{\mathrm{gs}}$ | -3.8    |

| $\mathrm{C}_{\mathrm{gd}}$ | -7.8    |

| $\mathrm{C}_{\mathrm{ds}}$ | -1.8    |

| g <sub>m</sub>             | +8.1    |

| $\mathbf{g}_{\mathrm{d}}$  | -0.7    |

| $R_{\rm s}$                | -5      |

| Rd                         | 0       |

| $ m R_{g}$                 | 0       |

| $R_{i}$                    | -0.7    |

### 2.3.2 オフセットゲート HEMT の提案

$g_m$ の向上と  $C_{gs}$ の低減は、ゲート長を短縮することが効果的である。本研究では EB 描画法を用いて  $0.15\,\mu$  m のゲート長の形成に成功した。しかし、さらなるゲート長の短縮はリソグラフィー技術により制約され限界がある。また、 $C_{gs}$  と  $C_{gd}$  を低減させるためには、それぞれゲート・ソース間距離およびゲート・ドレイン間距離を大きくすることが効果的である。しかし、ゲート・ソース間距離を大きくすると  $R_s$  が増大し、 $C_{gs}$  の低減効果は失われる。一方、ゲート・ドレイン間距離を大きくすると  $R_d$  が増大するが、表 2.1 より  $R_d$  は MAG に与える影響が小さく、 $R_d$  の増大による特性劣化は限定的である。

そこで、ゲート・ソース間距離は変化せず、ゲート・ドレイン間距離のみ大きくしたいわゆるオフセットゲート構造が特性向上に有効であると考えられる [54]。図 2.8 に基本的なノンオフセットゲート構造 HEMT とオフセットゲート構造 HEMT の断面構造を示す。オフセットゲート構造は、他のパラメータ ( $g_m$ 、  $R_s$ 、 $C_{gs}$ 等) に影響を及ぼすことなく  $C_{gd}$  の減少が可能であり、HEMT の特性向上が期待できる [55]。

ノンオフセットゲート構造HEMT

オフセットゲート構造HEMT

図2.8 HEMT断面構造

### 2.3.3 オフセットゲート P-HEMT の構造

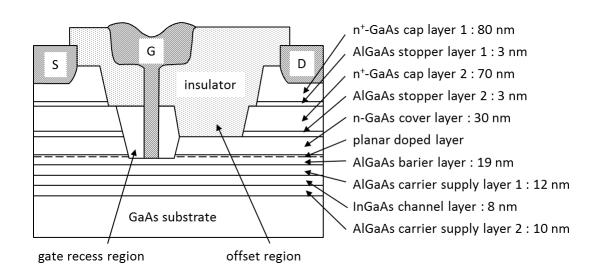

図 2.9 に本研究で評価を行ったオフセットゲート P-HEMT の断面構造を示す。 ゲート電極・ソース電極間距離に比べ、ゲート電極・ドレイン電極間距離が大き くなっているのが特徴である。各エピタキシャル層は半絶縁性 GaAs 基板上に MBE 法により成長した。n型層は Si をドーピングすることで形成した。チャネルには  $In_xGa_{1-x}As$  (x=0.25) を用いたシュードモルフィック構造を採用した。 また、チャネル層である InGaAs の上下には、キャリア供給層として n-AlGaAs を配置したダブルヘテロ構造を採用した。 キャリア供給層の上層のその他の層は順に n-AlGaAs バリア層、n-GaAs カバー層、n-AlGaAs エッチングストッパ層、n+-GaAs キャップ層 2、n-AlGaAs エッチングストッパ層、n+-GaAs キャップ層 1となっている。各層の膜厚は図 2.9 に示す通りである。

n-AlGaAs バリア層中には、n-GaAs カバー層とのコンタクト抵抗を低減するために約 2nm の Si プレーナドープ層を挿入した [56-57]。

ゲート電極はゲート長  $0.15\,\mu$  m の T 型構造を採用した。ゲート電極と n-AlGaAs バリア層の接触部分周辺(ゲートリセス領域)は、 $C_{gs}$  および  $C_{gd}$  低減のため表面保護絶縁膜を除去した中空状態となっている。

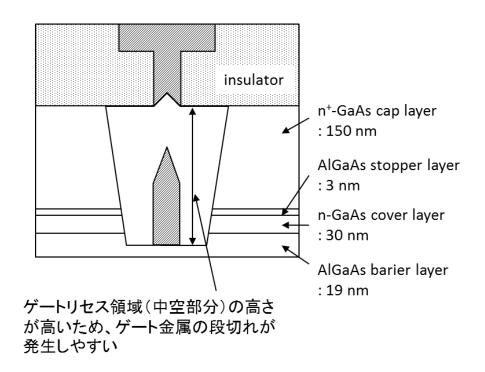

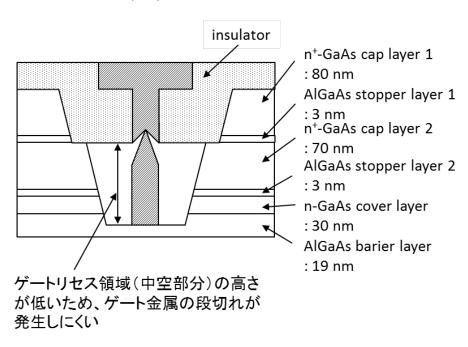

ソース・ドレイン電極には AuGe 系のアロイ電極を用いた。AuGe はアロイを行うことで GaAs と合金を形成する。それにより GaAs と AuGe 間のバリアが薄くなり容易にトンネリングが起こり、見かけ上オーミック性を示すようになる。この時 GaAs との合金化領域は 100nm 以上におよび、n+-GaAs キャップ層の膜厚が 100nm 以下の場合、合金化領域は下層の AlGaAs 層まで及ぶことになる。その場合チャネル層と合金化層とのコンタクト抵抗は増大する。したがって、n+-GaAs キャップ層の膜厚は 150nm 程度は必要である。一方、ゲート開口部の寸法は  $0.15\mu$  m 程度と狭く、ゲート金属蒸着時に開口部の絶縁膜側面に付着した金属が開口部をふさぐ形となり、開口部を通過する金属は徐々に減少する。やがて開口部は閉止し、以降金属は通過できなくなる。したがって、図 2.10 に示すように、n+-GaAs キャップ層の膜厚が 150nm 以上の場合、ゲートリセス領域

の高さも 150nm 以上となり、ゲート電極の段切れが問題となる。そこで、 $n^{+-}$  GaAs キャップ層の膜厚を 150nm 以上確保しつつゲートリセス領域の高さをゲート電極の段切れが発生しにくい 100nm 程度とするため、 $n^{+-}$  GaAs キャップ層を 2 段構造とした。本構造により、ゲートリセス領域の高さを  $n^{+-}$  GaAs キャップ層 2 と  $n^{-}$  GaAs カバー層等の合計厚さ 100nm 程度にすることが可能となり、ゲート電極の段切れを防止することができる。

図2.9 オフセットゲートP-HEMT断面構造

n+-GaAs cap layerが単層構造

n+-GaAs cap layerが2層構造

図2.10 HEMTゲート部拡大図

## 2.4 オフセットゲート P-HEMT 作製プロセスフロー

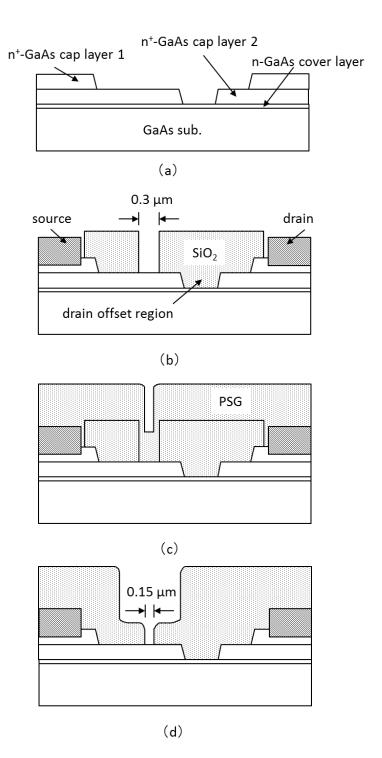

図 2.11 に本研究において開発したオフセットゲート P-HEMT の作製プロセスフローを示す。まず素子分離のためのメサエッチングをウエットエッチング法で行った。次にソース電極とドレイン電極が形成される領域以外の  $n^+$ -GaAsキャップ層 1 のエッチングをドライエッチング法で行った。ドライエッチングは Electron Cyclotron Resonance-RIE (ECR-RIE) を用い、反応ガスは SF6を使用した。SF6を用いたエッチングにより GaAs と AlGaAs のエッチング選択比は 1000 倍以上となり、 $n^+$ -GaAs キャップ層の高選択エッチングが可能となる。AlGaAs は GaAs に比ベバンドギャップが大きく抵抗が大きくなる。したがって AlGaAs の膜厚が厚くなるとキャップ層領域の抵抗が増大する懸念がある。本構造では n-AlGaAs エッチングストッパ層の膜厚を薄くすることが可能であるため、キャップ層領域の抵抗を極力小さくすることが可能である。続いてオフセット領域の  $n^+$ -GaAs キャップ層 2 のエッチングを同じくドライエッチング法で行った(図 2.11 (a))。

次にソース・ドレイン領域の  $n^+$ -GaAs キャップ層 1 上にソース・ドレイン電極を形成した。次に表面保護膜として Chemical Vaper Deposition(CVD)法により  $SiO_2$  を全面に堆積した。CVD は熱 CVD 法を用い、反応ガスとして  $SiH_4$  と  $O_2$  の混合ガスを使用した。ゲート電極形成部分に EB 描画法により  $0.3\,\mu$  m の開口パターンを形成し、ドライエッチング法で  $SiO_2$  の異方性エッチングを行った。ドライエッチングはアノードカップル型の RIE を用い、反応ガスは  $CHF_3$  と  $C_2F_6$  の混合ガスを使用した(図 2.11 (b))。

次に CVD 法を用いて全面に phospho silicate glass (PSG) を形成した。CVD は熱 CVD 法を用い、反応ガスとして  $PH_3$  と  $SiH_4$  と  $O_2$  の混合ガスを使用した。 PSG は被覆性に優れ、段差部分の表面や側面部分にも比較的均一な膜厚で膜を 堆積することができる。PSG の膜厚を最適化することで、 $0.3\,\mu$  m の開口部を制 御性良く  $0.15\,\mu$  m に短縮することができる(図 2.11 (c))。

次に T 型ゲートの T 字部分の幅に合わせた開口パターンを形成し、ドライエ

ッチング法で PSG の異方性エッチングを行い  $0.15\,\mu$  m の開口パターンを形成した (図 2.11 (d))。

次に  $0.15 \, \mu$  m の開口部を通して  $n^+$ -GaAs キャップ層 2 のエッチングをドライエッチング法(ECR-RIE)で行った。この時  $n^+$ -GaAs キャップ層 2 のサイドエッチング量を制御し、先にエッチングを行っているオフセット部分まで  $n^+$ -GaAs キャップ層 2 のサイドエッチングを行う。前述したように GaAs と AlGaAs のエッチング選択比は 1000 倍以上なので、エッチング時間にほとんど依存せず GaAs のみのエッチングが可能である。 $n^-$ AlGaAs エッチングストッパ層の下層には  $n^-$ GaAs カバー層が存在するため、この層がドライエッチングダメージのカバー層となり、ゲート電極が形成される  $n^-$ AlGaAs バリア層表面へのダメージを回避することができる(図 2.11 (e)) [58]。

続いて n-GaAs カバー層のエッチングをウエットエッチング法で行った(図 2.11 (f))。エッチング液はクエン酸と過酸化水素の混合液を用いた。クエン酸系のエッチング液はアンモニア水溶液を用いて pH を調整することで、GaAs と AlGaAs の高選択エッチングが可能である。エッチングは、過酸化水素が酸化剤として GaAs を酸化し、GaAs の酸化物をクエン酸が分解除去する形で行われる。GaAs がエッチング除去された後、AlGaAs 層でエッチングが停止するまで 5nm 程度の初期削れが発生する。この初期削れによりゲートリセス領域では 2nm 程度のプレーナドープ層が除去される。プレーナドープ層が残存した状態でゲート電極を形成した場合ゲート耐圧の低下が懸念されるが、プレーナドープ層が除去されることによってゲート耐圧は保たれる。

n-AlGaAs バリア層の初期削れ量により HEMT の  $V_{th}$  は変化するが、エッチング液の pH を正確に制御すれば初期削れ量はほぼ一定であり、あらかじめ初期削れ量を考慮して n-AlGaAs バリア層の膜厚および濃度を設定すれば、安定した  $V_{th}$  を得ることができる。しかし、クエン酸系エッチング液は所定の pH 範囲内であれば高選択比が得られるが、範囲外では急激に選択性は失われる。 GaAs のクエン酸エッチング後エッチング液洗浄のため超純水による洗浄が行われるが、超純水浸漬の瞬間、ウエハ表面に残存したクエン酸エッチング液と超純水が混合されることで pH は大きく変化する。この時エッチング液の高選択

性は失われ、ウエハ表面のエッチング液が十分薄くなるまで AlGaAs のエッチングが進行する。これは  $V_{th}$  ばらつきの原因となる。この AlGaAs の過剰エッチングを防止するため、エッチング後処理工程を導入した。以下にエッチング手順を説明する。クエン酸エッチング終了後、エッチングに使用するクエン酸エッチング液と同じ pH を有し、過酸化水素を混入していないリンス液に一旦試料を浸漬し、pH 値を維持したまま表面に残存している過酸化水素を洗浄除去し、その後超純水に浸漬してリンス液を洗浄する。 リンス液中は高選択性を維持できる pH であるため、浸漬中エッチングは進行しない。リンス液には過酸化水素は含まれていないため、浸漬中ウエハ表面の残存過酸化水素の濃度は徐々に薄くなっていき、やがてエッチングに寄与しない濃度に到達する。その後超純水に浸漬して pH が変化しても過酸化水素がウエハ表面に残存していないため、エッチングは進行せず AlGaAs の過剰エッチングを防止しつつクエン酸エッチング液を洗浄することが可能となる。

最後にゲート電極を形成した。ゲート電極はAlを用いた(図 2.11 (g))。

図2.11 オフセットゲートP-HEMT作製プロセスフロー

# 2.5 オフセットゲート P-HEMT 特性評価結果

## 2.5.1 DC 特性評価結果

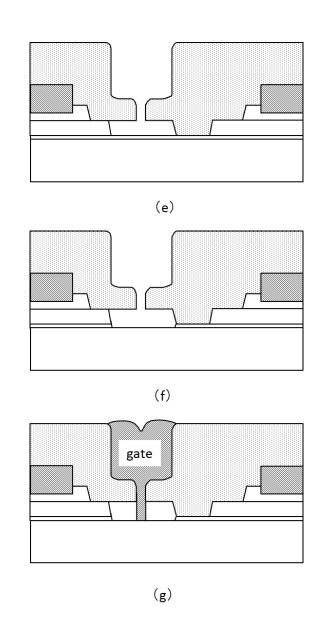

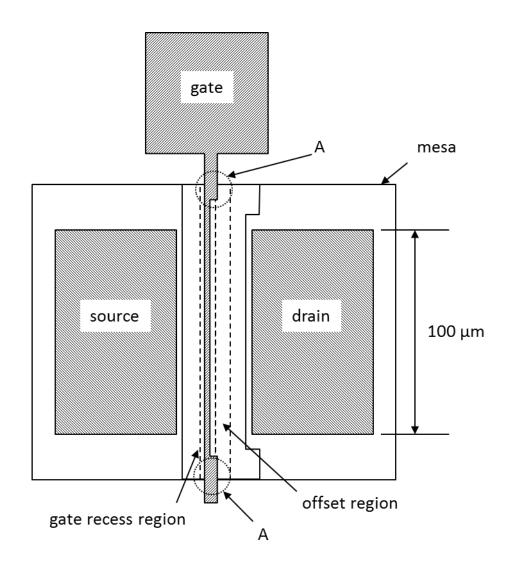

図 2.12 に本研究で DC 特性評価を行った HEMT のレイアウト図を示す。ゲート長  $0.15\,\mu$  m、ゲート幅  $100\,\mu$  m の素子を用いて測定を行った。メサ端部分には段差が存在するため、 $0.15\,\mu$  m 程度の微細パターンの場合ゲート電極の段切れが発生しやすい。そこで、ゲート電極が形成される部分のメサ端は、あらかじめパターン寸法を大きくしゲート電極の段切れを防止している(図 2.12 の A 部分)。

HEMT のしきい値電圧( $V_{th}$ )は-1V で、ゲート・ソース間電圧  $V_{gs}$ =0.5V の 時飽和電流 50mA となった。ドレイン・ソース間電圧  $V_{ds}$ =3V で最大  $g_m$ =55mS が得られた。また、ゲート・ドレイン間耐圧は、リーク電流値 1mA/mm となる 時の電圧で定義すると、13V となった。

図2.12 HEMTレイアウト図(DC測定用)

## 2.5.2 RF 特性評価結果

図 2.13 に RF 特性評価を行った HEMT のレイアウト図を示す。オフセットゲート構造 HEMT と、比較のためノンオフセットゲート構造 HEMT についても評価を行った。測定周波数は  $0.1\sim40 \mathrm{GHz}$  の範囲で行った。

表 2.2 に HEMT の等価回路パラメータの測定結果を示す。オフセットゲート構造の効果により、ノンオフセットゲート構造に比べ  $C_{gd}$  が約 25%、 $g_{d}$  が約 30% 低減した。 $R_{d}$  が約 20%増大したが、前述の通り  $R_{d}$  は MAG に大きな影響を及ぼさない。 $g_{m}$  は両者共にほぼ等しい値となった。両者の  $R_{s}$  がほぼ等しいことから、式 (2.4) で与えられる真正相互コンダクタンス  $(g_{m0})$  も等しくなると考えられる。

$$g_m = \frac{g_{m0}}{1 + g_{m0}R_c} \tag{2.4}$$

以上述べたように、本研究によるオフセットゲート構造 HEMT では、 $R_s$ 、 $C_{gs}$ 、及び  $g_m$  の劣化を伴わずに、 $C_{gd}$  の向上が可能となった。

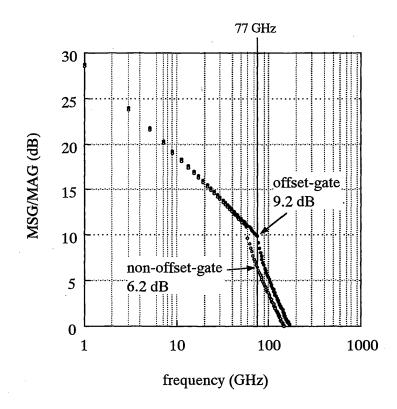

図 2.14 にシミュレーションにより求めた MAG の周波数依存性を示す。オフセットゲート構造 HEMT では、77GHz において 9.2dB の MAG が得られた。これは、ノンオフセット構造 HEMT に比べ 3dB 高い値となった。また、最大発信周波数( $f_{max}$ )は 170GHz となった。

non-offset-gate structure HEMT

図2.13 HEMTレイアウト図(RF測定用)

表 2.2 HEMT 等価回路パラメータ (測定値)

|                          | オフセットゲート | ノンオフセットゲート |

|--------------------------|----------|------------|

| $ m R_s$ ( $ m \Omega$ ) | 4.8      | 4.9        |

| $R_{d}(\Omega)$          | 10.9     | 8.8        |

| C <sub>gs</sub> (fF)     | 102      | 102        |

| C <sub>gd</sub> (fF)     | 9.8      | 12.0       |

| g <sub>m</sub> (mS)      | 60       | 59         |

| g <sub>d</sub> (mS)      | 1.96     | 2.86       |

図2.14 MAGの周波数依存性

# 2.6 ミリ波レーダー用 Monolithic Microwave Integrated Circuit

# 2.6.1 Monolithic Microwave Integrated Circuit の構造

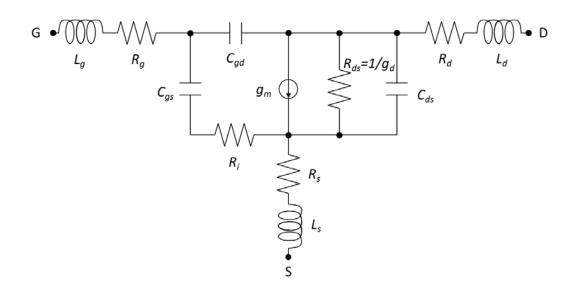

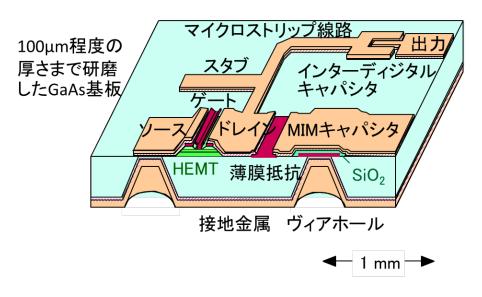

図 2.15 に基本的な MMIC の鳥瞰図を示す。MMIC は、能動素子である HEMT と、受動素子である抵抗、キャバシタ等で構成され、信号の伝送路としてスタブを含むマイクロストリップ線路が配置されている。 GaAs 基板は  $80\,\mu$  m 程度まで研磨により薄層化され、各素子は基板を貫通して形成される VIA ホールを通して裏面で接地される。抵抗素子は  $100\,\Omega/\Box$ の WSiN 膜を用い、キャパシタ素子は  $600 \mathrm{pF/mm^2}$ の SiN Metal-Insulator-Metal (MIM) キャパシタを用いた [59-61]。

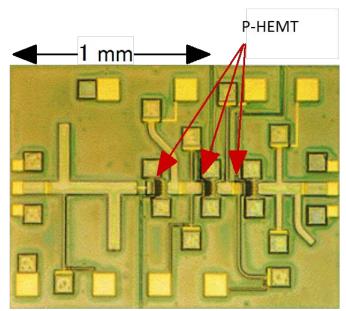

図 2.16 に本研究で評価を行ったミリ波車載レーダー用 77GHz3 段パワーアンプの写真を示す。HEMT を 3 段配置しているのが特徴である。HEMT のゲート幅は、1 段目と 2 段目は  $50\,\mu$  m、3 段目は  $100\,\mu$  m である。

図2.15 MMIC鳥瞰図

77GHzミリ波パワーアンプMMIC (出力:10 mW)

図2.16 ミリ波車載レーダ用3段パワーアンプ

# 2.6.2 3 段パワーアンプ特性評価結果

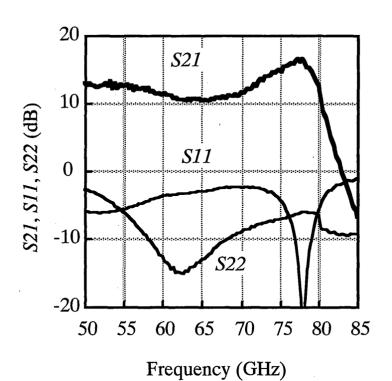

図 2.17 に 3 段パワーアンプにおける小信号利得の周波数特性を示す。 $V_{ds}$ =3.5V 印加時、周波数 77GHz において小信号利得 16.5dB が得られた。

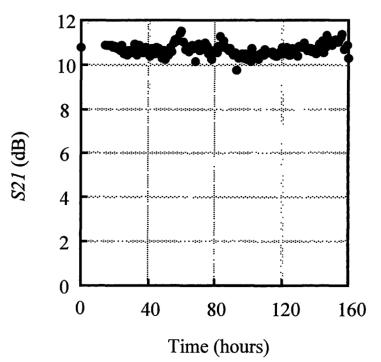

また、同パワーアンプについて、簡易寿命試験も行った。測定は試料温度 175  $\mathbb{C}$ 、 $V_{ds}=3.5$  V、 $V_{gs}=-0.2$  V で行った。図 2.18 に小信号利得の測定時間依存性を示す。測定時間 160 hr においても小信号利得の減少は見られず、一定の値となった。これまで報告されている InGaAs HEMT が破壊される活性化エネルギー1.7eV や [62]、その他の報告にある FET および MMIC の活性化エネルギー1.3  $\sim 2.5eV$  [63-65] 等の値からおおよその中心値 1.5eV を用いて寿命を計算すると、自動車で必要とされる最高使用温度 85  $\mathbb{C}$  における寿命は 30 年となった。

図2.17 3段パワーアンプにおける 小信号利得の周波数依存性

図2.18 3段パワーアンプの簡易寿命試験結果

### 2.7 まとめ

オフセットゲート構造を有する InGaAs チャネル P-HEMT を試作し、評価した結果、ノンオフセットゲート構造に比べ  $C_{gd}$  が約 25%低減し、 $f_{max}$ =170GHz が得られた。また、シミュレーションにより求めた MAG は、周波数 77GHz において 9.2dB となり、これはノンオフセット構造 HEMT に比べ 3dB 高い値となった。

同 P-HEMT を用いた 3 段パワーアンプを試作した結果、周波数  $77 \mathrm{GHz}$  において小信号利得  $16.5 \mathrm{dB}$  が得られた。また、同パワーアンプについて簡易寿命試験を行ったところ、試料温度  $175 ^{\circ} \mathrm{C}$ で測定時間  $160 \mathrm{hr}$  においても小信号利得の減少は見られず一定の値となった。これは、活性化エネルギーを  $1.5 \mathrm{eV}$  と仮定して寿命を計算すると、 $85 ^{\circ} \mathrm{C}$ で 30 年の寿命に相当する。

# 第3章 パワー半導体デバイスプロセス

#### 3.1 はじめに

p-n ダイオードはトランジスタに比べ作製プロセスは比較的単純であり、その特性も結晶構造に大きく影響され、作製プロセスの改善による特性向上の余地は小さい。しかし、より高い特性目標達成のため結晶ドーピング濃度や膜厚の厳密な制御が高く要求されるにつれ、これまで大きな問題となっていなかったプロセスの制御性等が問題視されるようになってきた。本章では従来のp-n ダイオード作製プロセスにおける問題点の改善として、p 形電極上コンタクトホール形成プロセスのドライエッチング化と、メサ構造形成時のドライエッチングダメージ回避、および回復プロセスの検討を行った結果について述べた。

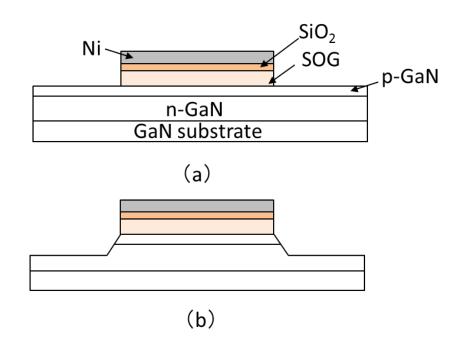

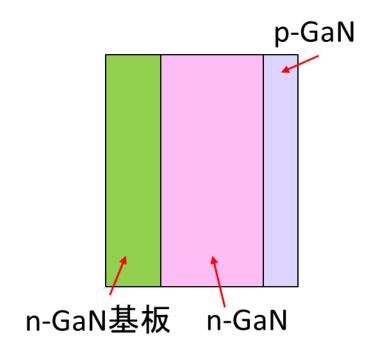

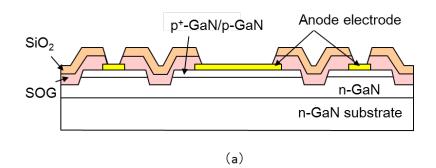

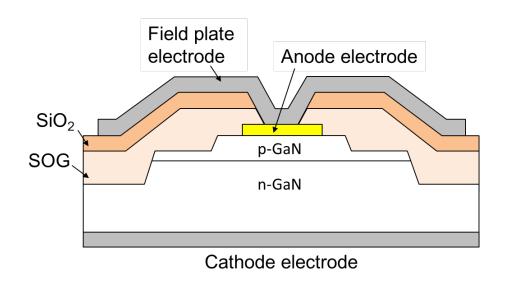

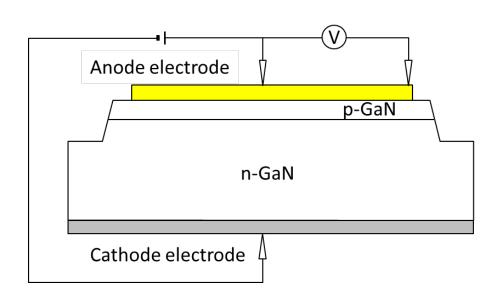

# 3.2 p-n ダイオード断面構造

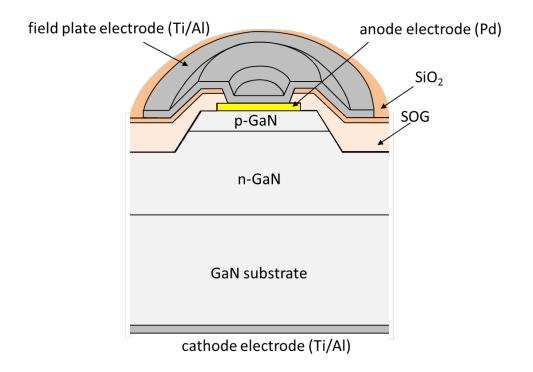

図 3.1 に本研究における p-n ダイオードの断面構造を示す。 n 形の GaN 基板上に n-GaN 層と p-GaN 層をそれぞれ成長した構造で、p-GaN 層表面にはアノード電極が、GaN 基板表面にはカソード電極がそれぞれ形成されている。素子分離は p-GaN 層をエッチングしたメサ構造を用いた。 p-n ダイオードの形状は、形状の不均一により発生することが懸念される場所による電界分布の相違を極力回避するため円形とした。 p-n ダイオードの表面保護膜は、膜形成時のダメージがほとんど無視できる Spin on Glass (SOG) と表面保護特性に優れた  $SiO_2$  の多層構造を用いた。 p-n ダイオードのメサ端付近の電界集中緩和のため、フィールドプレート (FP) 電極を p-n ダイオード周辺部分に配置した [66-68]。

図3.1 自立GaN基板上p-nダイオードの断面構造

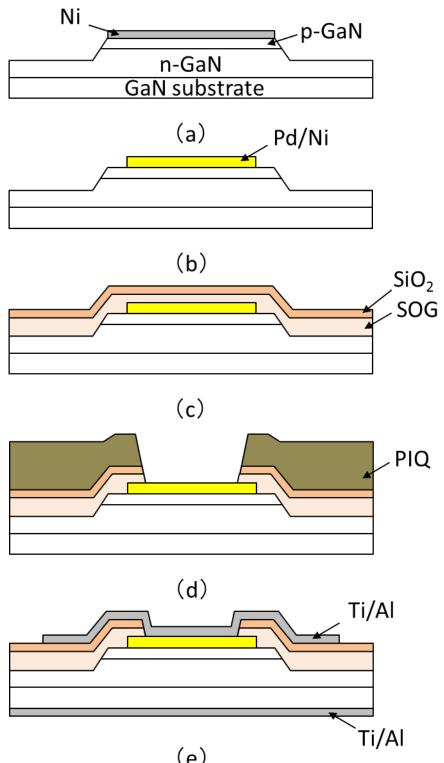

# 3.3 p-n ダイオード作製プロセスフロー

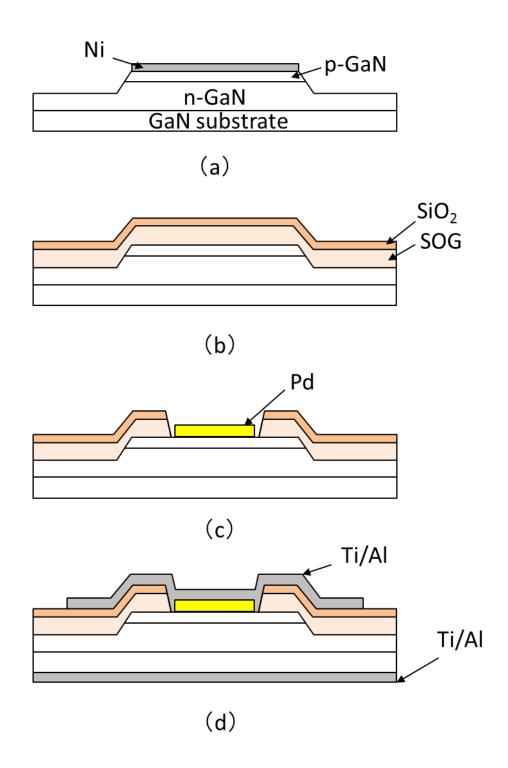

図 3.2 に本研究における p-n ダイオードの基本作製プロセスフローを示す。 GaN 基板上に Metal Organic-Vapor Phase Epitaxy(<math>MO-VPE)法 [69-70]で n-GaN 層(Si ドープ)および p-GaN 層(Mg ドープ)を成長した後、Mg 活性化のために  $850^{\circ}$ C 30 分( $N_2$ 中)のアニールを行った。次に、EB 蒸着法で Ni を蒸着し、リフトオフ法でメサエッチング用パターンを形成し、Ni をマスクとして GaN のエッチングを行なった(図 3.2 (a))。エッチングは Inductive Coupled Plasma-Reactive Ion Etching(ICP-RIE)法にて行い、反応ガスは  $CF_4$  と Ar の混合ガスを用いた。コイル出力は 400W、RF 出力は 150W とした。

次に、全面に表面保護膜である SOG と SiO<sub>2</sub>を形成した。SOG は日揮触媒化成製セラメート LNT-K を用い、塗布後、ホットプレートにて 120  $\mathbb{C}$  5分、350  $\mathbb{C}$  30分のアニールを行い形成した。SiO<sub>2</sub>はスパッタリング法を用いて形成した(図 3.2 (b))。

次に、コンタクトホール用のレジストパターンを形成し、HFにて SOG と  $SiO_2$ のエッチングを行った。続いて EB 蒸着法で Pd を蒸着し、リフトオフ法で p 形オーミック電極を形成した(図 3.2 (c))。

次に、EB 蒸着法で Ti/Al を蒸着し、リフトオフ法で FP 電極を形成した。最後に裏面に EB 蒸着法で Ti/Al を蒸着し、n 形オーミック電極を形成し完成である(図 3.2 (d))。

図3.2 p-nダイオード作製プロセスフロー

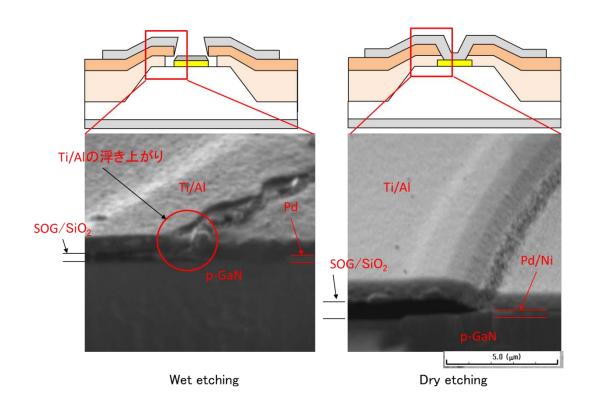

## 3.4 コンタクトホール加工のドライエッチング化

前述の通りより高い特性目標を掲げるにあたり、これまで顕在化していなかった p-n ダイオード作製プロセスの問題点が明らかになってきた。以下の項にて従来プロセスでの問題点の改善に関する検討結果を述べる。

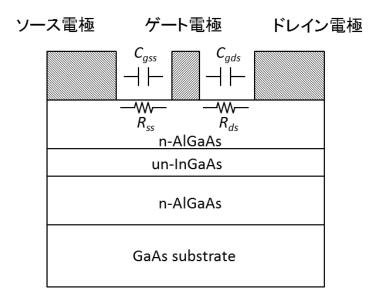

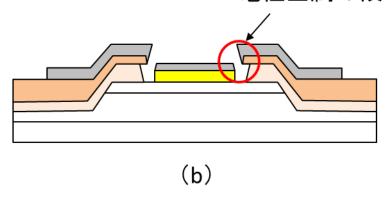

問題点の一つ目は、コンタクトホール加工後の SOG と  $SiO_2$  の形状である。 SOG と  $SiO_2$  は HF に対するエッチングレートが異なり SOG の方が  $SiO_2$  よりエッチングレートが速いため、コンタクトホール加工後のエッチング形状は、図 3.3 (a) に示すように、 $SiO_2$  に比べ SOG のサイドエッチング量が大きくなる。このような形状のコンタクトホール上に電極金属を EB 蒸着法で蒸着すると、図 3.3 (b) に示すように、電極金属に段切れが発生することが懸念される。段切れにより p 形電極と FP 電極が絶縁された場合、FP 電極によるメサ端の電界集中緩和効果は失われ、耐圧劣化の原因となり得る。そこでコンタクトホール加工方法として、SOG と  $SiO_2$  のエッチングレートが等しいドライエッチング法の適用を検討した。またドライエッチング法を適用した場合、p-GaN 層上に直接 SOG が形成されていると SOG ドライエッチング時 p-GaN 層が直接ドライエッチングに晒されるため、p-GaN 層を保護するため、保護層を兼ねた p-形オーミック電極の先行作製プロセスも併せて検討した [71]。

# 電極金属の段切れの懸念有

図3.3 p-nダイオードのコンタクトホール形状

図 3.4 に作製プロセスフローを示す。図 3.2 (a) に示したメサ形成プロセスと同様にメサを形成した後(図 3.4 (a))、表面保護膜形成前にp 形オーミック電極 (Pd/Ni) をリフトオフ法で形成した(図 3.4 (b))。Pd は  $SiO_2$  や SOG との接着性が低いため、Pd 上に直接 SOG を形成すると Pd 上の SOG が剥がれたり、クラックが発生したりすることが懸念される。そこでp 形オーミック電極は、後に形成する SOG との接着性向上のため、Pd 上に Ni を蒸着した 2 層構造とした。

次に、全面に表面保護膜である SOG と  $SiO_2$  を形成した(図 3.4 (c))。SOG と  $SiO_2$  の形成方法は前述の通りである。

次に、SOG と  $SiO_2$  の加工用マスクパターンを形成し、ドライエッチング法で SOG と  $SiO_2$  の加工を行った(図 3.4 (d))。加工用のマスクパターンは、日立化成製感光性ポリイミド HD8820 を用いた。形成条件は、塗布後 120 で 5 分間のベークを行い、露光現像後、150 で 5 分間、200 で 30 分間のベークを行った。ドライエッチングは ICP-RIE 法を用い、エッチング条件は前述の通りである。

ドライエッチング後、マスクであるポリイミドを同じく ICP-RIE 法を用いて除去した。反応ガスは  $O_2$  を用い、コイル出力は 400W、RF 出力はポリイミド以外の膜が極力エッチングされないように 0 とした。

以下のプロセスは従来プロセスと同様である(図 3.4 (e))。

図3.5に従来のウエットエッチング法によるコンタクト加工プロセスおよび、本研究で検討したドライエッチング法によるコンタクト加工プロセス後の断面形状観察結果を示す。ウエットエッチング法により加工を行った場合、本試料においては金属の段切れは観察されなかったが、金属の浮き上がりが観られ、不安定な接触になっていると考えられる。それに対し、ドライエッチング法により加工を行った場合、良好なテーパ形状となり、良好な金属の被覆性が観察された。

(e) (Triple of the control of the

図3.5 p-nダイオードのコンタクトホール形状観察結果

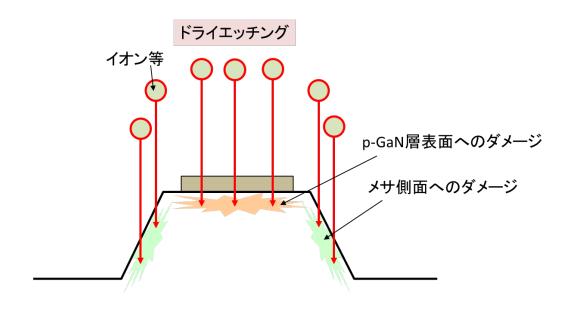

# 3.5 メサエッチング時のドライエッチングダメージ低減

問題点の二つ目は、ドライエッチング時のダメージによる特性の劣化である。前述の通りメサエッチングは ICP-RIE 法により行っている。エッチング中に発生するイオン等の衝突衝撃により GaN はダメージを受ける。ダメージは主に2つの場所で発生すると考えられる。図 3.6 に示すように、1つ目はエッチングマスクである Ni をエッチング時に発生するイオン等が突き抜けることによる p-GaN 層表面へのダメージであり、2つ目はメサ側面へのダメージである。それらのダメージを低減するためのプロセスについて検討した結果を以下に述べる。

図3.6 メサエッチング時の ドライエッチングダメージ概念図

# 3.5.1 3層マスク構造によるドライエッチングダメージ低減

メサエッチングの際のエッチングマスクは膜厚 300nm の Ni を用いているが、エッチングが進行するにつれて Ni も同時にエッチングされ膜厚が薄くなる。エッチング時に発生するイオン等の Ni 侵入深さは明らかではないが、薄層化された Ni を通過したイオン等が GaN 表面に達することによりダメージが発生する事が懸念される。Ni は厚膜化により剥がれが生じやすく、また、Ni の厚膜化によりリフトオフ用スペーサ膜も厚膜化する必要があり、Ni の厚膜化は困難である。一方、SOG や  $SiO_2$  は厚膜化は容易であるが、GaN よりエッチングレートが高いためエッチングマスクとしては機能しない。そこで、エッチングマスクとして Ni を用い、ダメージカバー層として Ni の下層に SOG と  $SiO_2$  を形成した 3 層構造パターンを検討した。

図 3.7 に本研究で検討したメサエッチングプロセスを示す。試料全面に SOG と  $SiO_2$  を形成し、リフトオフ法により Ni のマスクパターンを形成した(図 3.7 (a))。SOG と  $SiO_2$  の形成方法は前述の通りである。その後 Ni をマスク としてドライエッチング法で GaN のエッチングを行った(図 3.7 (b))。以下のプロセスは前述の通りである。

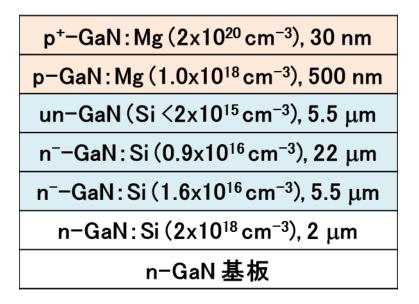

上記プロセスにより p-n ダイオードの試作を行い、特性評価を行った。図 3.8 に試作を行った試料の層構造を示す。

図3.7 3層マスク構造を用いた メサ形成プロセスフロー

$p^+$ -GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm p-GaN: Mg (1.0x10<sup>18</sup> cm<sup>-3</sup>), 500 nm un-GaN (Si <2x10<sup>15</sup> cm<sup>-3</sup>), 5.5 μm n<sup>-</sup>-GaN: Si (0.9x10<sup>16</sup> cm<sup>-3</sup>), 22 μm n<sup>-</sup>-GaN: Si (1.6x10<sup>16</sup> cm<sup>-3</sup>), 5.5 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm n-GaN 基板

図3.8 p-nダイオードの層構造

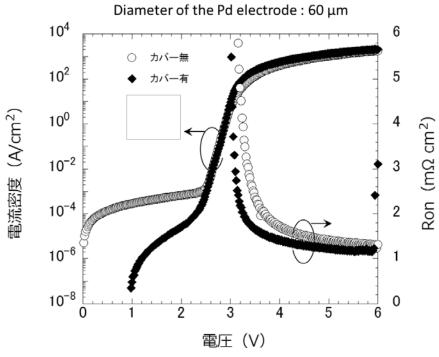

図 3.9 に従来プロセスおよび本研究で検討を行ったカバー層付メサ形成プロセスにより試作した p-n ダイオードの順方向 I-V 特性評価結果を示す。p-n ダイオードの電極径は  $60\,\mu$  m である。順方向電圧 5V において、オン抵抗は従来プロセスの 1.39m  $\Omega$  cm² に対し、カバー層付プロセスでは 1.22 m  $\Omega$  cm² と約 15%低減した。これは、従来プロセスでは Ni を突き抜けたイオン等が p-GaN 層表面にダメージを発生させ、p型コンタクト抵抗を増大させているのに対し、カバー層付プロセスでは、Ni を突き抜けたイオン等が p-GaN 層まで到達することを防止できた効果であると推測される。

図 3.10 に従来プロセスおよび本研究で検討を行ったカバー層付メサ形成プロセスにより試作した p-n ダイオードの耐圧の電極径依存性を示す。逆方向耐圧は両者の間に相違は見られなかった。これは、メサ側面へのダメージはカバー層の有無に関係なく同様に発生するため差が生じないのに加え、p-GaN 層表面へのダメージは逆方向耐圧には影響を及ぼさない事が原因と考えられる。したがって、耐圧向上のためにはメサ側面へのダメージを低減する必要がある。

図3.9 順方向I-V特性評価結果

図3.10 耐圧の電極径依存性評価結果

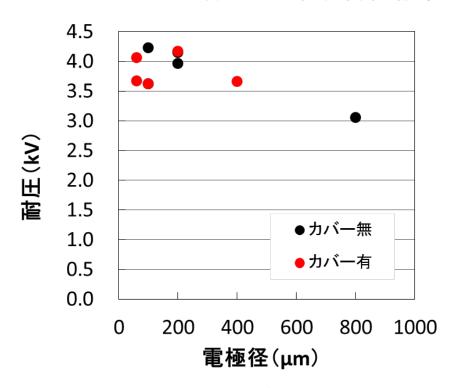

# 3.5.2 ドライエッチングダメージのアニールによる回復

前述の通り、3 層マスク構造ではメサ側面へのダメージを低減することは出来ない。そこで、ドライエッチングダメージのアニールによる回復を試みた [72]。図 3.11 にアニールによるダメージ回復プロセスフローを示す。まず図 3.7 に示した 3 層マスク構造メサ形成プロセスを用いてメサを形成した(図 3.11 (a))。

次に Ni を除去して全面にスパッタリング法で SiN を形成した(図 3.11 (b))。

次にレジストマスクで p-GaN 表面上の SiN と SiO<sub>2</sub>、SOG を HF を用いてエッチング除去した(図 3.11(c))。続いてダメージ回復を兼ねた Mg 活性化アニールを行った。アニール条件は 850 $^\circ$  30 分(N<sub>2</sub>中)である。メサ形成により p-GaN 層や n-GaN 層の側面が露出した状態でアニールを行うと、そこから Ga や N の抜けが発生しやすく特性劣化の原因となり得る。そこでアニール時のメサ側面保護のため SiN 膜を形成した。また、全面が SiN で覆われている状態でアニールを行うと、p-GaN 層表面から H の抜けが発生しにくいため Mg の活性化が妨げられる恐れがある。そこで p-GaN 上の SiN 表面はエッチングを行い p-GaN 層表面を露出させた。以降は図 3.4 に示したプロセスと同様に行った。

図3.11 アニールによるダメージ回復プロセスフロー

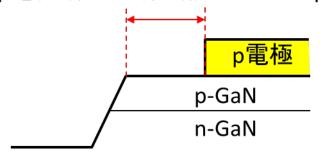

また本研究では p 電極端からメサ端までの距離がどのように特性に影響を与えるかも評価するため、図 3.12 に示すように p 電極端からメサ端までの距離を  $5\sim100\,\mu$  m まで変化させた素子も作製した。図 3.13 に試作を行った試料の層構造を示す。p-n ダイオードの電極径は  $60\,\mu$  m である。

図 3.14 に耐圧の p 電極端・メサ端距離依存性を示す。 p 電極端・メサ端距離の変化による特性の変化は見られなかった。 p・n ダイオードの逆方向電圧印加時の破壊は、最も電界が集中するメサ端で起こることが多い。メサ端部分にダメージを受けた p・n ダイオードは、p 電極端からの距離に関わらず、一定の電圧印加時にメサ端で破壊が発生すると考えられる。本試料では、ばらつきはあるものの、回復アニールによって耐圧の向上がみられた。破壊箇所がメサ端が中心である事に相違はないが、その部分のダメージがアニールにより回復したことで耐圧が向上したものと思われる [73]。

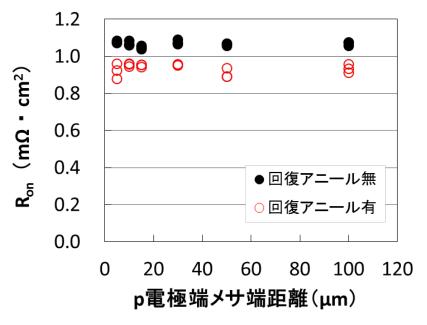

図 3.15 にオン抵抗の p 電極端-メサ端距離依存性を示す。回復アニール有の試料でオン抵抗の低下が見られた。しかし本試作では、回復アニール無の試料はメサエッチングの際に 3 層マスク構造を用いていない。回復アニール有の試料は 3 層マスク構造を用いているため、本試作における評価結果のオン抵抗の差は回復アニールの効果と 3 層マスク構造の効果の切り分けをすることが困難である。また、耐圧同様オン抵抗に関しても p 電極端-メサ端距離の変化による特性の変化は見られなかった。p-GaN 層は n-GaN 層に比べ膜厚が薄いため、p-GaN 層の横方向の抵抗は比較的高くなり、p-GaN 層内での横方向の電流の拡がりは小さくなると思われる [74]。そのためメサ端付近では p-GaN 層に電流はほとんど流れず、本研究で検討を行った p 電極端-メサ端距離の範囲内では距離依存性が観測できなかったと考えられる。p 電極端-メサ端距離 5  $\mu$   $\mu$  以下で評価を行う必要がある。

p電極端-メサ端距離: X=5~100μm

図3.12 評価試料の断面構造

$p^+$ -GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm p-GaN: Mg (1x10<sup>18</sup> cm<sup>-3</sup>), 500 nm un-GaN (Si <2x10<sup>15</sup> cm<sup>-3</sup>), 3.0 μm n<sup>-</sup>-GaN: Si (1.15x10<sup>16</sup> cm<sup>-3</sup>), 19 μm n<sup>-</sup>-GaN: Si (1.6x10<sup>16</sup> cm<sup>-3</sup>), 5 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm n-GaN 基板

図3.13 p-nダイオードの層構造

図3.14 耐圧のp電極端メサ端距離依存性評価結果

図3.15 オン抵抗のp電極端 メサ端距離依存性評価結果

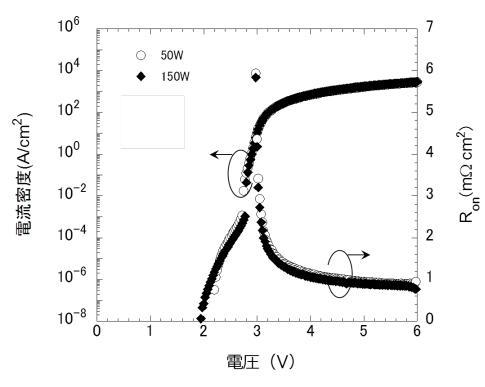

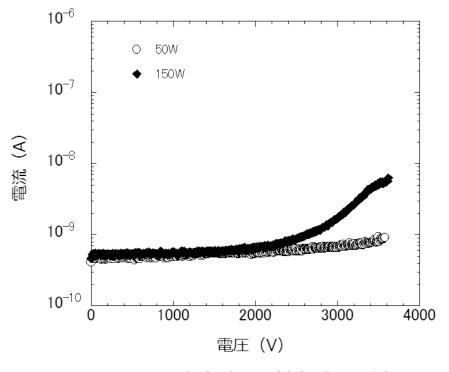

### 3.5.3 低パワードライエッチングによるダメージ低減

ドライエッチングはエッチングガス雰囲気中で放電を起こしイオン等を発生させ、そのイオン等をバイアスを印加してエッチング対象物に向かって加速し、イオン等と対象物を衝突あるいは反応させることにより行う。したがって、イオン等を加速させるエネルギーが大きければダメージは大きくなる。現状加速エネルギーは 150W で行っているが、ダメージ低減のためそれを 50W に減少してエッチングを行い特性を比較した。本試料は、両者ともに 3 層マスク構造を用いて試作を行った。試料の層構造は、図 3.8 に示した構造と同じ構造のものを用いた。p-n ダイオードの電極径は 60  $\mu$  m である。

図 3.16 に順方向 I-V 特性評価結果を示す。本試料の p 電極端-メサ端距離は  $15 \mu$  m である。両者の間に特性の大きな相違は観測されなかった。前述したように、p-GaN 層の横方向の抵抗は比較的高いため、p 電極端-メサ端距離の大きい素子のメサ側面のダメージの影響は観測されにくいと思われる。

図 3.17 に逆方向 I-V 特性評価結果を示す。破壊耐圧は両者の間に大きな相違は見られなかった。しかし 2kV 以上の電圧で、150W の試料に比べ 50W の試料は電流値が小さくなり、3kV における電流値は 150W の  $1.7x10^{-9}A$  に対し50W では  $7x10^{-10}A$  と半分程度となった。加速エネルギーを低くしたことでメサ側面へのダメージが減少し、その部分を流れるリーク電流が減少したものと予想されるが、現時点では詳細は不明である。

図3.16 順方向I-V特性評価結果

図3.17 逆方向I-V特性評価結果

#### 3.6 まとめ

p·n ダイオード作製プロセスにおいて明らかとなった問題点について、それらを改善する検討を行った。

p型電極上に形成されるコンタクトホールに関し、従来のウエットエッチング 法から新たにドライエッチング法の検討を行い、良好な FP 電極形状が得られ た。

また、メサ形成時のドライエッチングダメージに関し、ドライエッチング時のマスクとして 3 層マスク構造を適用し、p-GaN 層表面のドライエッチングダメージ低減を図り、従来プロセスに比べ約 15%オン抵抗を低減した。一方 3 層マスク構造では対応できないメサ側面のドライエッチングダメージに関しては、メサ側面を SiN 膜で保護した状態で  $850^{\circ}$  C 30 分のアニールを行い、耐圧の向上を果たした。加えてドライエッチング時の加速エネルギーを 150W から 50W に減少することで、メサ側面のリーク電流を抑制し逆方向電流を減少させることが出来た。

#### 第4章 パワー半導体デバイスの高耐圧化

#### 4.1 はじめに

高電圧、大電流での使用が想定されるパワー半導体デバイスは、デバイスの高耐圧化と同時に低消費電力化・高効率化が重要である。本研究で着目した p-n ダイオードにおける低消費電力化・高効率化のためにはデバイスのオン抵抗の低減が必要であるが、高耐圧化と低オン抵抗化はトレードオフの関係にあり両立は困難である。また、高電圧印加時におけるデバイス保護の観点から、アバランシェ耐量(アバランシェ降伏による電流増加から p-n ダイオード破壊に至るまでの許容エネルギー)は大きいことが望ましい。本研究では、上記課題を改善するため p-n ダイオード層構造の改善およびデバイス構造の改善を行った。

層構造の改善として、オン抵抗の増大を極力抑制しつつ耐圧の向上を図るべくマルチドリフト層構造を有する p-n ダイオードの検討および、アバランシェ耐量向上のため、パンチスルー現象を利用することでダイオード降伏後も破壊が生じにくい高アバランシェ耐量 p-n ダイオードの検討を行った。

また、デバイス構造の改善として、p-n ダイオードの降伏はメサ端で電界が最も集中するため主にメサ端で発生することから [75-76]、メサ端での電界集中を緩和することが可能となるガードリング構造 p-n ダイオードおよび、p-GaN 層薄層化 p-n ダイオードの検討を行った。

## 4.2 マルチドリフト層構造 p-n ダイオード

## 4.2.1 p-n ダイオード空乏層中の電界分布

p 型半導体とn 形半導体を接触すると、p-n 接合界面にはp 層側、n 層側それ ぞれに空乏層が拡がる [77]。p 層側およびn 層側の空乏層幅をそれぞれ  $X_p$ 、 $X_n$  とすると、

$$X_p = \sqrt{\frac{2\varepsilon N_d}{qN_a(N_d + N_a)}} \phi_B \tag{4.1}$$

$$X_n = \sqrt{\frac{2\varepsilon N_a}{qN_d(N_d + N_a)}} \phi_B \tag{4.2}$$

となる。ここで、q は電荷素量( $1.602\times10^{-19}$  C)、 $\epsilon$  は誘電率、 $N_a$  は p 層のドーピング濃度、 $N_d$  は n 層のドーピング濃度、 $\phi_B$  はビルトインポテンシャルである。この時、空乏層内部には電界が発生する。空乏層中任意の位置 X における電界強度は p 層側で、

$$E = -\frac{qN_a}{\varepsilon} (X + X_p) \tag{4.3}$$

n層側で、

$$E = \frac{qN_d}{\varepsilon}(X + X_n) \tag{4.4}$$

となる。ただし X=0 は p-n 接合の位置であり、この場合  $X_p>0$ 、 $X_n<0$  となる。 p-n 接合間に電圧 V を印加すると空乏層の幅は変化するが、その時の空乏層幅は、それぞれ下記式で表される。

$$X_p = \sqrt{\frac{2\varepsilon N_d}{qN_a(N_d + N_a)}(\emptyset_B - V)}$$

(4.5)

$$X_n = \sqrt{\frac{2\varepsilon N_a}{qN_d(N_d + N_a)}(\emptyset_B - V)}$$

(4.6)

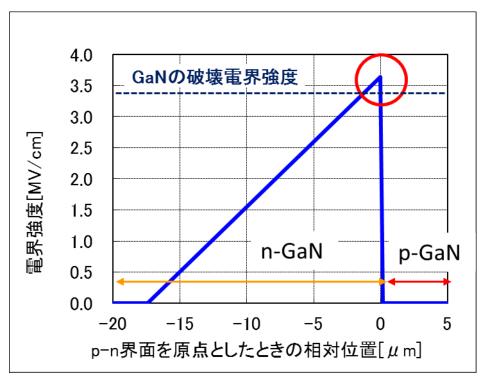

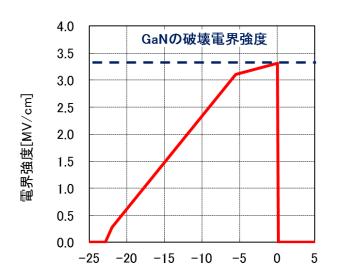

図 4.1 に式 (4.4) から求めた、図 3.1 に示した p-n ダイオードの n 層側空乏層中の電界強度分布(絶対値)を示す。横軸の 0 は p-n 接合界面で、左側負の値

が n 層側、右側正の値が p 層側の相対位置を示している。電界強度は p-n 接合界面で最大となり、基板側に向かって減少していく。表 1.1 に示したように、 GaN の絶縁破壊電界強度は 3.3 MV/cm であるため、式 (4.6) 中の p-n 接合間の電圧 V を増加し、電界強度の最大値が 3.3 MV/cm に達した時ダイオードはブレークダウンを起こす。電界強度の最大値は p-n 接合界面であるため、p-n ダイオードのブレークダウンは p-n 接合界面で発生する。 V の値を p-n ダイオードの目標耐圧の値として設定すれば、p-n 接合界面の電界強度が 3.3 MV/cm となる時の  $N_a$  と  $N_d$  を見積もることが可能となる。ここで  $N_a$  の値を固定すると、耐圧は  $N_d$  の濃度や膜厚により制御出来る。このように濃度や膜厚により耐圧を決定する n 形層はドリフト層と呼ばれている。

耐圧を向上するためには  $N_d$ を小さくすることが有効であるが、 $N_d$ を小さくすると n-GaN 層の抵抗が大きくなりオン抵抗が増大するため、単純に  $N_d$  を小さくすることは必ずしも特性向上には繋がらない。

図4.1 p-nダイオードの空乏層電界強度分布

### 4.2.2 マルチドリフト層構造 p-n ダイオードの電界分布

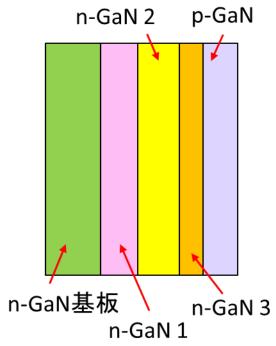

図 4.1 に示した通り、n 層側空乏層中の電界はp-n 接合界面付近で最大となる。 それは p-n 接合界面付近以外の部分で p-n 接合界面付近の電界強度を超えない程度に電界強度が増加しても、耐圧には大きな影響を与えない事を意味している。したがって、p-n 接合界面付近の  $N_d$  を減少し、それ以外の部分の  $N_d$  を増加することで、n-GaN 層の抵抗増大を極力抑制したうえで耐圧向上が可能となる [66]。このように  $N_d$  の異なる 2 層のドリフト層を有する p-n ダイオードは、ダブルドリフト層構造 p-n ダイオードと呼ばれる。

図 4.2 にダブルドリフト層構造 p-n ダイオードの n 層側空乏層中の電界強度分布を示す。p-n 接合界面付近のみの  $N_d$  を減少することで、p-n 接合界面付近の電界強度のみ減少している事が分かる。

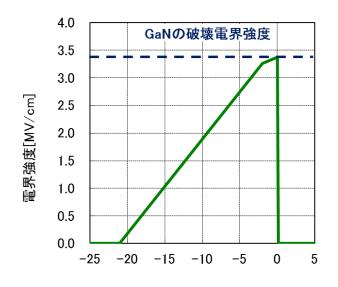

さらなる高耐圧化のためには、さらに p-n 接合界面付近の  $N_d$  を減少する必要がある。しかし、結晶成長装置の性能上  $N_d$  濃度の低減には限界が存在する。低濃度化が困難な場合、低濃度層の厚膜化が高耐圧化には効果的である。しかし、低濃度層を厚膜化した場合 n-GaN 層の抵抗増大が顕著になる。耐圧向上とオン抵抗増大抑制の調整を行うため、ドリフト層中に中間の濃度を有する層を 1 層加えたトリプルドリフト層構造が提案された。図 4.3 にこの時の n 層側空乏層中の電界強度分布を示す。p-n 接合界面付近で電界強度が最大となるのは他の構造と同様であるが、ドリフト層中の他の位置での電界強度がトリプルドリフト層構造ではより平均化されている事が分かる。なお所望の耐圧及びオン抵抗を得るためには、ドリフト層各層  $N_d$  の最適化を要する。

キャリア濃度: n-GaN1 > n-GaN2

図4.2 ダブルドリフト層構造p-nダイオードの 空乏層電界強度分布

キャリア濃度 : n-GaN 1 > n-GaN 2 > n-GaN 3

図4.3 トリプルドリフト層構造p-nダイオードの 空乏層電界強度分布

# 4.2.3 マルチドリフト層構造 p-n ダイオード特性評価結果

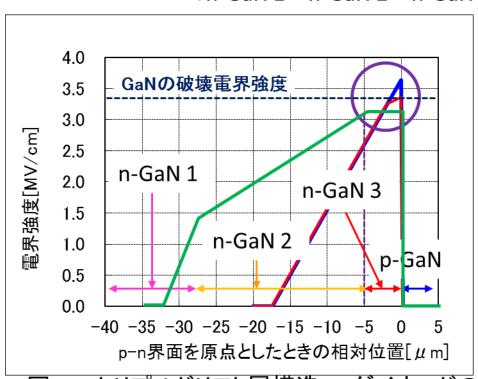

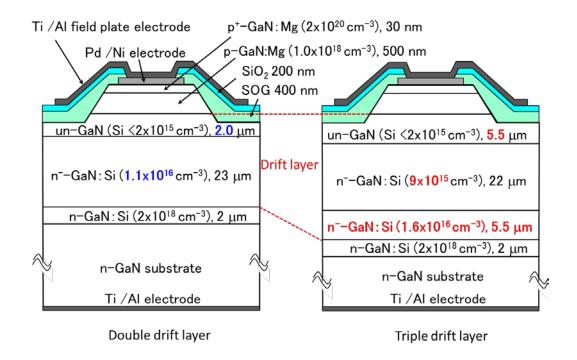

ダブルドリフト層構造および、トリプルドリフト層構造を有する p-n 接合結晶を用いて p-n ダイオードを作製し、その特性を評価した [78-79]。図 4.4 にそれぞれの結晶構造を示す。本試作では、図 3.4 に示したプロセスと同様メサエッチング時に 3 層マスク構造を用いず、ドライエッチング時の RF 出力は 150W として行った。

図 4.5 にそれぞれの結晶構造から計算した n 層側空乏層中の電界強度分布を示す。それぞれの結晶構造から求めた耐圧の理論値は、ダブルドリフト層構造で 3.2kV、トリプルドリフト層構造で 4.6kV となった。

図4.4 p-nダイオードの断面構造

pn界面を原点としたときの相対位置[μm]

逆方向印加電圧:3200V (a)ダブルドリフト層構造

pn界面を原点としたときの相対位置[μm]

逆方向印加電圧:4600V

(b)トリプルドリフト層構造

図4.5 p-nダイオードの空乏層電界分布

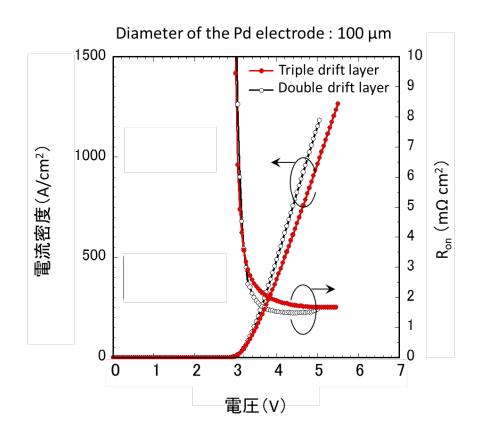

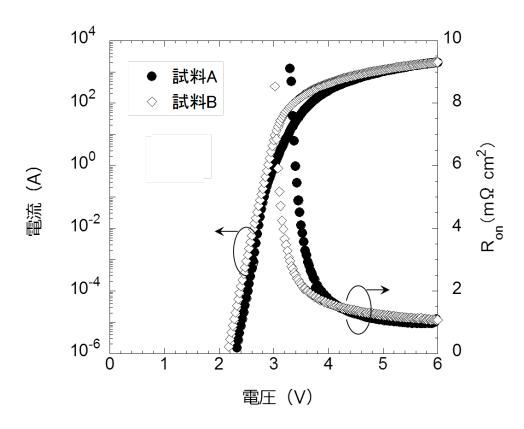

図 4.6 にそれぞれの順方向 I-V 特性評価結果を示す。p-n ダイオードの電極径は  $100\,\mu$  m である。順方向電圧 5V におけるオン抵抗は、ダブルドリフト層構造で  $1.2 \mathrm{m}\,\Omega\,\mathrm{cm}^2$ 、トリプルドリフト層構造で  $1.6 \mathrm{m}\,\Omega\,\mathrm{cm}^2$  となった。

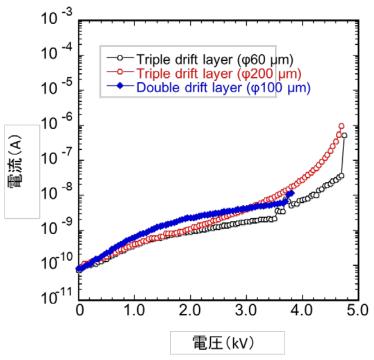

図 4.7 にそれぞれの逆方向 I-V 特性評価結果を示す。耐圧は、ダブルドリフト 層構造で 3.9kV、トリプルドリフト層構造で 4.7kV となった。この結果は、耐圧の理論値とほぼ同等か超えるものであり、極めて良好な結果である。

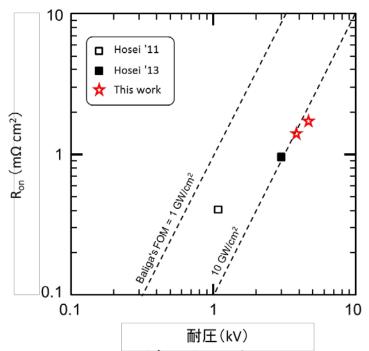

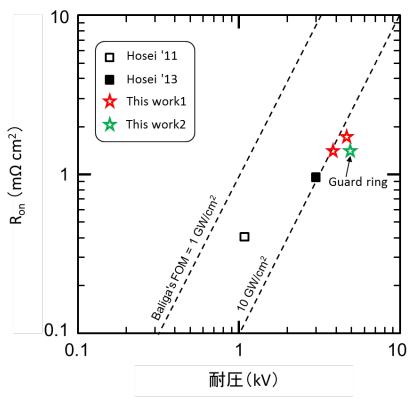

図 4.8 にこれらの結果から求めたそれぞれの p-n ダイオードの Baliga の性能指数を示す。同時にこれまで法政大学で行ってきた p-n ダイオードの評価結果についても表示した [66-68]。Baliga の性能指数とは、素子のオン抵抗と耐圧の関係を表したもので、半導体デバイスの性能を表す指標の一つである。Baliga の性能指数は次式で与えられる [27-28]。

$$BFOM = \frac{V_B^2}{R_{on}} \tag{4.7}$$

ここで $V_B$ は耐圧、 $R_{on}$ はオン抵抗である。

図中の  $10GW/cm^2$  のラインは前述の通り GaN の理論限界値である。

それぞれの Baliga の性能指数値は、ダブルドリフト層構造で 12.7 GW/cm<sup>2</sup>、トリプルドリフト層構造で 13.8 GW/cm<sup>2</sup>となり、両者ともに理論限界値である 10GW/cm<sup>2</sup>を大きく超える値となった。理論限界値はドリフト層が単層の場合の計算値であり、本試作で理論限界値を大きく超える値が得られたのは、ドリフ

ト層を多層構造とすることで耐圧が向上し、オン抵抗の増大を最小限に抑制することが出来たためであると考えられる。

図4.6 順方向I-V特性評価結果

図4.7 逆方向I-V特性評価結果

図4.8 p-nダイオードのBFOM BFOM: Baliga's Figure of Merit

## 4.3 ガードリング構造による p-n ダイオードの高耐圧化

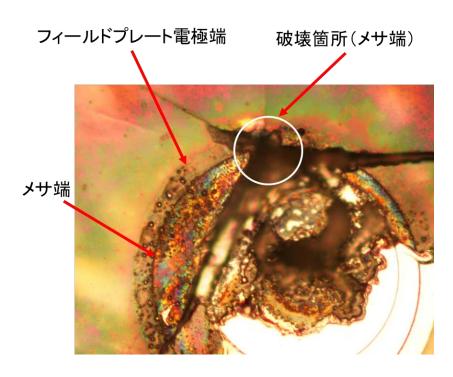

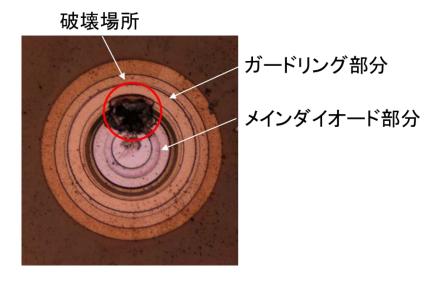

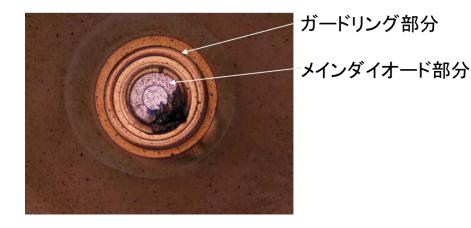

前述したように、マルチドリフト層構造を適用した p·n ダイオードにおいて、ほぼ理論値通りの耐圧が得られた。しかし、図 4.9 に示すように p·n ダイオードのブレークダウン後の破壊箇所は主にメサ端付近である。これは、メサ端付近の電界集中をまだ有効に抑制できていない事を表しており、この部分の電界集中を緩和することでより高耐圧が得られる可能性を示唆している。本項ではメイン p·n ダイオードの周辺部分にガードリング構造 p·n ダイオードを配置し、メイン p·n ダイオードのメサ端部分の電界集中を緩和することで、高耐圧化を図った結果について述べる [80]。

図4.9 p-nダイオードブレークダウン後の 表面観察結果

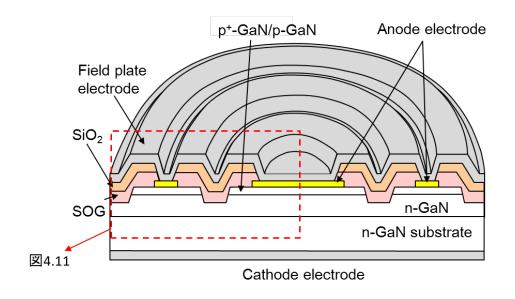

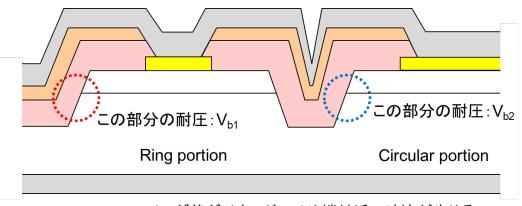

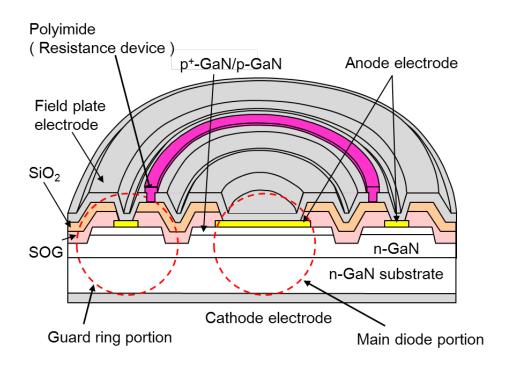

## 4.3.1 ガードリング構造 p-n ダイオード

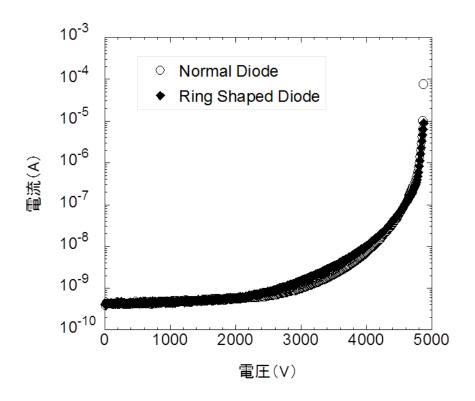

図 4.10 にメイン p-n ダイオードの周辺部分にリング状 p-n ダイオードを配置した p-n ダイオードの断面構造を示す。このような p-n ダイオードでは、メイン p-n ダイオード部分のメサ端部分よりリング状 p-n ダイオード部分のメサ端部分よりリング状 p-n ダイオード部分のメサ端部分でより大きく電界が集中し、ブレークダウン時の p-n ダイオードの破壊はリング状 p-n ダイオード部分のメサ端付近で発生する。図 4.12 にリング状 p-n ダイオード有の p-n ダイオードと通常 p-n ダイオードの逆方向 I-V 特性評価結果を示す。図に示した通り、リング状 p-n ダイオード有の p-n ダイオードでも通常の p-n ダイオードに比べ耐圧は低下していない。これは、リング状 p-n ダイオード有の p-n ダイオードでは、リング状 p-n ダイオード部分のメサ端部分で通常 p-n ダイオードのメサ端部分とほぼ等しい電界集中が発生し、メイン p-n ダイオード部分のメサ端部分の耐圧は通常の p-n ダイオードに比べ改善されているということを意味している(図 4.11)。したがって、リング状 p-n ダイオード部分のメサ端部分の耐圧を V<sub>b1</sub>、メイン p-n ダイオード部分のメサ端部分の耐圧を V<sub>b2</sub> の関係が成立する。

図4.10 リング状p-nダイオードの断面構造

$V_{b2} < V_{b1}$ : リング状ダイオードのメサ端付近で破壊が生じる

図4.11 リング状p-nダイオードの断面構造 (リング状部分の拡大)

図4.12 逆方向I-V特性評価結果

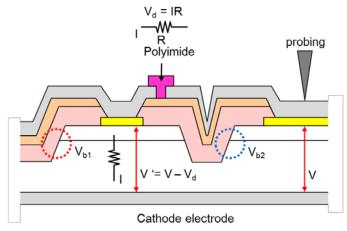

図 4.13 に本研究で提案したガードリング構造 p-n ダイオードの断面構造を示 す。図 4.10 に示したリング状 p-n ダイオード有の p-n ダイオードのリング状部 分とメイン p-n ダイオード部分の間に抵抗素子を挿入した構造となっている(こ のような構造の時リング状 p-n ダイオード部分をガードリングと呼ぶ)。このよ うな構造では、逆方向電圧印加時に抵抗素子の抵抗値に応じてガードリング部 分とメイン p-n ダイオード部分の間に電圧降下が生じる。ガードリング部分と メイン p-n ダイオード部分の間の電圧降下がほぼ 0 の時、逆方向印加電圧が Vならば、カソード電極とガードリング間の電圧はカソード電極とメイン p-n ダ イオード部分の間の電圧とほぼ等しく V となる。ガードリング部分とメイン pn ダイオード部分の間に  $V_d$  の電圧降下が生じた場合、カソード電極とメイン pn ダイオード部分の間の電圧は変わらず V であるが、カソード電極とガードリ ング部分間の電圧は  $V-V_d$  となる。もし、 $V_{b2}-V_{b1}>V_d$  ならば、 $V-V_d=V_{b1}$  の 時ガードリング部分のメサ端付近で破壊が生じる。この場合は Va 分耐圧が向上 したことになる。もし、 $V_{b2}-V_{b1}$ < $V_{d}$ ならば、 $V-V_{d}=V_{b1}$ の時ガードリング部分 のメサ端付近で破壊は生じず、 $V = V_{b2}$ の時メイン p-n ダイオード部分のメサ端 付近で破壊が生じる。この場合は  $V_{b2}-V_{b1}$  分耐圧が向上したことになる。つま り  $V_{b2}-V_{b1}$ < $V_{a}$  となるように抵抗素子の抵抗値を設定することでより大きな耐 圧の向上が見込まれる。

図4.13 ガードリング構造p-nダイオードの断面構造

$V_{b2}$ - $V_{b1}$ > $V_{d}$ ならば

V=V<sub>b1</sub>の時

V – V<sub>d</sub><V<sub>b1</sub>なので

ガードリングメサ端で破壊は発生しない

V – V<sub>d</sub>=V<sub>b1</sub>の時 ガードリングメサ端付近で破壊

V<sub>b2</sub>-V<sub>b1</sub>< V<sub>d</sub>ならば

v-V<sub>a</sub>=V<sub>b1</sub>の時 ガードリングメサ端で破壊は発生しない

V=V<sub>b2</sub>の時

メインダイオードのメサ端付近で破壊

V<sub>d</sub>分耐圧向上

V<sub>b2</sub>-V<sub>b1</sub>分耐圧向上

図4.14 ガードリング構造p-nダイオードの断面構造 (ガードリング部分拡大)

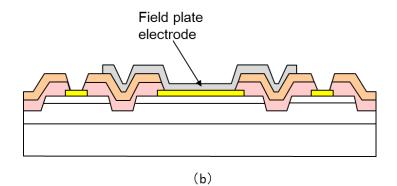

## 4.3.2 ガードリング構造 p-n ダイオードの作製プロセスフロー

図 4.15 にガードリング構造 p-n ダイオードの作製プロセスフローを示す。メサエッチング時にメイン p-n ダイオード部分と同時にガードリング部分となるメサ領域を形成した後、コンタクトホール加工までは図 3.4 に示したプロセスと同様に行った(図 4.15 (a))。これ以降の試作は、特に言及が無ければ全てメサエッチング時に 3 層マスク構造を用い、ドライエッチング時の RF 出力は 50W として行う。

コンタクトホール加工後、メイン p-n ダイオード部分のフィールドプレート電極をリフトオフ法で形成し(図 4.15 (b))、その後ガードリング部分のフィールドプレート電極を同じくリフトオフ法で形成した(図 4.15 (c))。

試料裏面にn形オーミック電極を形成し、最後に抵抗素子を形成した(図 4.15 (d))。抵抗素子は日立化成製感光性ポリイミド HD8820 を用いた。形成方法は、試料にポリイミドを塗布し、120  $^{\circ}$   $^{\circ}$   $^{\circ}$  5 分のベーク後露光現像し、150  $^{\circ}$   $^{\circ}$  5 分 および 350  $^{\circ}$   $^{$

Polyimide (Resistance device)

図4.15 ガードリング構造p-nダイオードの プロセスフロー

#### 4.3.3 抵抗素子の I-V 特性

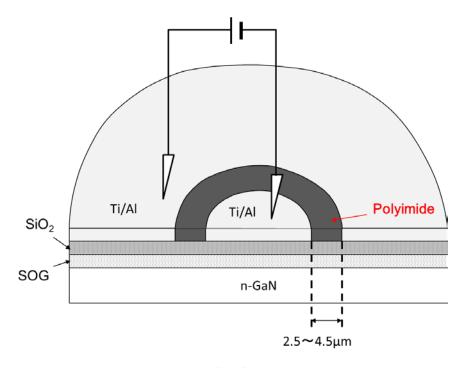

ガードリング構造 p-n ダイオードの評価に先立ち、図 4.16 示す素子を用いて抵抗素子の I-V 特性の評価を行った。抵抗素子の幅は  $2.5\sim4.5\,\mu$  m の間で変化した。

図 4.17 に I-V 特性評価結果を示す。抵抗素子の幅に係らず電流値が大きくばらつき不安定な結果となった。これは、抵抗材料であるポリイミドのベーク温度が 350  $^{\circ}$  と比較的低温であるため、ポリイミドが完全に硬化せず、不安定な状態になっている事が考えられる。ポリイミドの形成は  $\mathbf{p}$  電極形成後であるため、 $\mathbf{p}$  形層と  $\mathbf{p}$  電極とのコンタクトの悪化を防止するため 350  $^{\circ}$   $^{\circ}$  を超える温度での処理は現状困難である。より特性を安定させるためには、抵抗値を適度な値に安定的に調整する必要がある。

図4.16 抵抗評価用素子

図4.17 抵抗素子のI-V特性評価結果

### 4.3.4 ガードリング部分とメイン p-n ダイオード部分間の電圧降下

実際ガードリング部分とメインp-nダイオード部分間でどの程度の電圧降下が発生しているかを直接的に概算するため、図 4.18 示す素子の測定を行った。メイン p-n ダイオード部分のコンタクトホールを形成しない事で、フィールドプレート電極とメイン p-n ダイオード部分とを電気的に分離している。抵抗素子を挿入していない p-n ダイオードと耐圧を比較することで、ガードリング部分とメイン p-n ダイオード部分間の電圧降下を概算することが可能となる。

図 4.19 に図 4.18 示す素子の抵抗素子幅  $3\mu$  m および  $4\mu$  m の時の耐圧測定結果を示す。また、比較のため抵抗素子が挿入されていない素子の測定結果も示す。評価を行った試料の層構造は図 4.20 に示す通りである。抵抗素子を挿入していない p-n ダイオードの耐圧約 4.7kV に対し、抵抗素子幅  $3\mu$  m 素子で約 100~ 200V 高い 4.9kV、抵抗素子幅  $4\mu$  m 素子で約 400V 高い 5.1kV となった。この結果から、ガードリング部分とメイン p-n ダイオード部分間の電圧降下は 100~ 400V 程度であると概算できる。

図4.18 電圧降下測定用素子の断面構造

図4.19 逆方向I-V特性評価結果

$p^+$ -GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm p-GaN: Mg (1.0x10<sup>18</sup> cm<sup>-3</sup>), 500 nm un-GaN (Si <2x10<sup>15</sup> cm<sup>-3</sup>), 5 μm n<sup>-</sup>-GaN: Si (1.05x10<sup>16</sup> cm<sup>-3</sup>), 20 μm n<sup>-</sup>-GaN: Si (1.6x10<sup>16</sup> cm<sup>-3</sup>), 5 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm n-GaN 基板

図4.20 p-nダイオードの層構造

### 4.3.5 ガードリング構造 p-n ダイオードの抵抗素子幅依存性評価結果

試作を行った試料の層構造は、図 4.4 に示したトリプルドリフト層構造のものと同じ構造のものを用いた。図 4.21 にガードリング構造 p·n ダイオードと通常 p·n ダイオードの順方向 I-V 特性評価結果を示す。両者の特性に違いは見られなかった。ガードリング部分とメイン p·n ダイオード部分の間に高抵抗な素子が挿入されているため、ガードリング部分は順方向 I-V 特性に影響を及ぼさない。

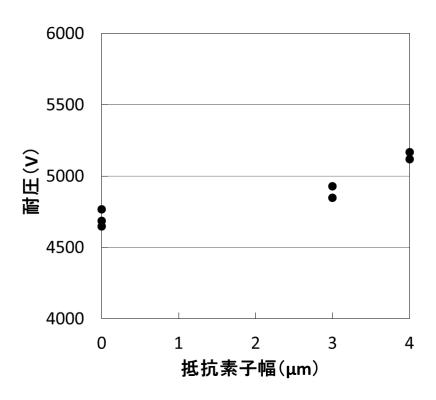

図 4.22 に耐圧の抵抗素子幅依存性評価結果を示す。通常 p·n ダイオードに比べガードリング構造 p·n ダイオードは、評価を行った全ての抵抗幅において耐圧が 100~200V 程度向上した素子が存在した。

図 4.23 にガードリング構造 p-n ダイオードのブレークダウン後の表面観察結果を示す。耐圧が向上した素子では、全ての抵抗幅で破壊はメイン p-n ダイオード部分のメサ端付近で発生した。メイン p-n ダイオード部分のメサ端付近での破壊は、メイン p-n ダイオード部分のメサ端付近よりガードリング部分のメサ端付近の耐圧が向上していることを示唆している。本検討では耐圧の向上は  $100\sim200V$  であり、抵抗素子が正常に形成できていると考えた場合、ガードリング部分とメイン p-n ダイオード部分間での電圧降下が  $100\sim400V$  程度である事も考慮して(4.5.4 参照)、耐圧の向上が観測された素子については全て  $V_{b2}$ - $V_{b1}$ < $V_{d}$  の関係が成立していると考えられる。しかし、一部の素子で耐圧の向上が見られないものが存在し、その素子の多くはガードリング部分のメサ端付近で破壊が起こっている。これらに関しては抵抗素子が正常に形成されていない事が予想され、やはり高耐圧を安定的に得るためには、抵抗素子の最適化・安定

図4.21 順方向I-V特性評価結果

図4.22 耐圧の抵抗素子幅依存性

図4.23 ブレークダウン後の表面観察結果

### 4.3.6 高耐圧仕様結晶を用いたガードリング構造 p-n ダイオードの評価

前述の結果を踏まえ、4.7kV 耐圧を達成したウエハを用いてガードリング構造 p-n ダイオードの試作を行い評価した。なお、図 4.15 に示したガードリング部分のフィールドプレート電極とメイン p-n ダイオード部分のフィールドプレート電極を別々に作製するプロセスでは、両フィールドプレート電極作製時のリソグラフィーの際合わせずれにより両フィールドプレート電極が接触する恐れがあるため、本試作では両フィールドプレート電極を同一のマスクで同時に作製するセルフアラインプロセスを適用した。この場合、両フィールドプレート電極の間隔が短いとリフトオフ用パターン形成が困難であるため、両フィールドプレート電極の間隔(つまり抵抗素子の幅)は 3 μ m 以上とした。

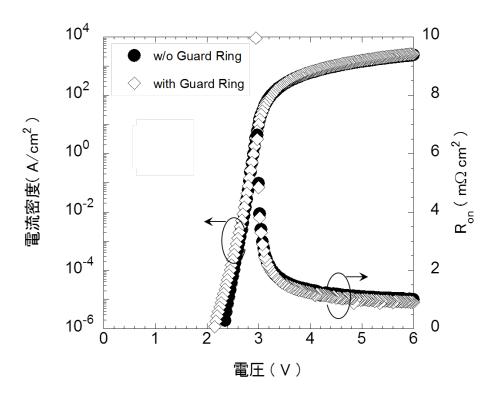

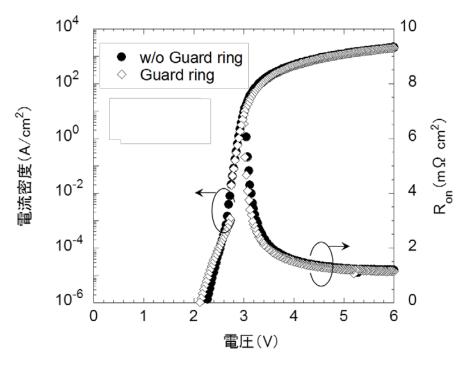

図 4.24 にガードリング構造 p-n ダイオードと通常 p-n ダイオードの順方向 I-V 特性評価結果を示す。p-n ダイオードの p 形電極径は  $60\,\mu$  m である。両者の特性に相違は見られなかった。

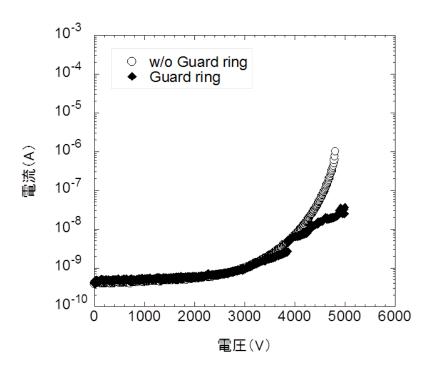

図 4.25 にガードリング構造 p-n ダイオードと通常 p-n ダイオードの逆方向 I-V 特性評価結果を示す。p-n ダイオードの p 形電極径は  $60\,\mu$  m である。抵抗素子の幅  $4\,\mu$  m のガードリング構造 p-n ダイオードにおいて耐圧 5kV を達成した。

図 4.26 にこれらの結果から求めたガードリング構造 p-n ダイオードの Baliga の性能指数を示す。本試作では Baliga の性能指数は、理論限界である 10  $GW/cm^2$  を大きく超える 20  $GW/cm^2$  が得られた。

図 4.27 にガードリング構造 p-n ダイオードのブレークダウン後の表面観察結

果を示す。本試料においても破壊はメイン p-n ダイオード部分のメサ端付近で発生している。したがって、本試料の素子も  $V_{b2}-V_{b1}$ < $V_{d}$  の関係が成立していると考えられる。

図4.24 順方向I-V特性評価結果

図4.25 逆方向I-V特性評価結果

図4.26 p-nダイオードのBFOM BFOM: Baliga's Figure of Merit

図4.27 ブレークダウン後の表面観察結果

#### 4.4 パンチスルー現象を利用した可逆性 p-n ダイオードの作製

#### 4.4.1 p-n ダイオードのアバランシェ降伏

GaN p-n ダイオードの逆方向電圧印加時の破壊は、主にアバランシェ降伏 [81] が原因で発生する。以下にアバランシェ降伏について簡単に説明する。

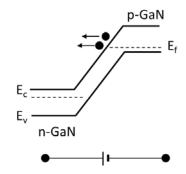

図 4.28 にアバランシェ降伏現象を示す模式図を示す。p·n 接合に大きな逆方向電圧を印加すると、空乏層内に熱励起で発生した電子が加速され格子内に散乱される。その散乱電子が結晶原子と衝突し原子内の価電子を励起して電子・正孔対を生成する。生成されたキャリアもまた逆方向電圧で加速され、同じように次々と価電子を励起する。このようにキャリアが増加することで電流が急激に増加しやがて降伏するような現象を電子雪崩降伏 (アバランシェ降伏)という。アバランシェ降伏が発生すると、多くの場合 p·n ダイオードは破壊され元の特性を示さなくなる。アバランシェ降伏による電流増加から p·n ダイオード破壊に至るまでの許容エネルギーはアバランシェ耐量と呼ばれ、アバランシェ耐量を超えるエネルギーを与えた時 p·n ダイオードはアバランシェ降伏による局所的な発熱等で破壊される。

アバランシェ降伏はいわゆる頓死と呼ばれる突然破壊が発生する場合が多く、特に p-n ダイオードの構造上部分的に電界が集中しやすい場所が存在する場合はそれが顕著である。そしてその場合は比較的低いリーク電流で破壊が生じる。頓死の場合事前に降伏の瞬間を察知することは困難である。実用上は降伏の直前を察知することが出来れば、その瞬間にパワーの供給を停止することでデバ

イスの保護が容易となる。そこでアバランシェ降伏が発生しにくい、いわゆる頓 死の起こりにくい p-n ダイオードについて検討を行った。この場合比較的高い リーク電流レベルでも破壊が生じないため、比較的低いリーク電流で破壊が生 じる場合に比べ降伏のタイミングを察知しやすく、所定のリーク電流値を超え た段階でパワーの供給を停止することが可能となる。

逆方向電圧印加により電子が加速

電子が結晶原子と衝突→電子・正孔対が発生

発生した電子・正孔対が逆方向電圧で加速→結晶原子と衝突→電子・正孔対が発生

大電流が流れ降伏

# 図4.28 アバランシェ降伏現象模式図

### 4.4.2 パンチスルー現象

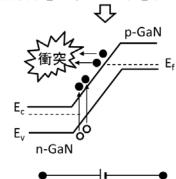

図 4.29 にパンチスルー現象を示す模式図を示す。p-GaN 表面に被着した Pd は本来ショットキー接触となるが、p-GaN 層の濃度を高くすることで金属・半導 体界面に形成される空乏層の厚さを極めて薄くすることが可能であり、キャリ アである正孔は薄い空乏層をトンネリング現象により容易に通り抜けることが 出来、実質的にオーミック接触となる。p-n 接合に逆方向電圧を印加すると、両 者のアクセプタ、ドナー濃度に応じて接合界面から両側に空乏層が拡がる。本来 空乏層にはほとんどキャリアが存在しないため、逆方向電圧印加時流れる電流 は極めて小さい。しかし p 形層側空乏層が大きく拡がりほぼ p 形層中全域が空 乏化されると、p形層側空乏層中に電子をキャリアとした導電性が生じ電流が流 れる。このような現象はパンチスルー現象と呼ばれている [82-83]。p 形層側空 乏層中に導電性が生じるパンチスルー現象は、電流の増加の仕方がアバランシ ェ降伏と異なり緩やかなため p-n ダイオードは破壊されにくい。したがって、 パンチスルー現象がアバランシェ降伏より先に起きるような p-n ダイオードは 破壊が発生するまでの許容電流増加量が大きく(すなわちアバランシェ耐量が 大きく)、この電流増加を検知して保護回路を動作できる。この場合、p-n ダイ オードは破壊されないため p-n ダイオードに可逆性が生じる。したがって、ア バランシェ降伏が発生する電圧より低い電圧でパンチスルー現象が発生するよ うに p 形層のアクセプタ濃度や膜厚を調整することで、アバランシェ降伏の起 こりにくい可逆性 p-n ダイオードを作製することが可能であると考えられる。

図4.29 パンチスル一現象模式図

#### 4.4.3 逆方向 I-V 特性の温度依存性

半導体のキャリアの緩和時間が短くなると、電子雪崩による電流増幅度合いが減少するので、アバランシェ耐量は増加し降伏電圧も高くなる。p-n ダイオードの温度を上昇させると格子振動により緩和時間が短くなり飽和電子速度が小さくなるため、逆方向電圧印加時降伏電圧は増加する。つまり、p-n ダイオードの降伏原因としてアバランシェ降伏が支配的である場合、温度の上昇により降伏電圧は増加する [84]。

一方、パンチスルー電圧の温度依存性は空乏層幅の温度依存性すなわち拡散電位の温度依存性と関連性を有するが、拡散電位の温度依存性はほとんど見られないので(微減)、パンチスルー電圧の温度依存性はほとんど見られない(微増)と考えられる。

参考として、降伏原因としては他にツェナー降伏現象が存在するが、この場合は温度の上昇により降伏電圧は減少する。

したがって、p-n ダイオードの逆方向 I-V 特性の温度依存性を測定することで、 どのようなメカニズムで降伏が発生しているか推定することが出来る。

#### 4.4.4 逆方向 I-V 特性の温度依存性評価結果

意図的にパンチスルー現象を発生させることでアバランシェ降伏によるp-n ダイオードの破壊を抑制することが出来るか評価するため、確実にパンチスルー

現象が発生すると思われる層構造を有する試料で p-n ダイオードを作製し、逆方向 I-V 特性の評価を行った。

図 4.30 に評価を行った試料の層構造を示す。p-GaN 層の Mg ドーピング濃度は  $2\times10^{20}$   $cm^{-3}$  と高濃度であるが、Mg は  $10^{19}$   $cm^{-3}$ 以上ドーピングしてもそれ以上はアクセプタとして機能しないと言われており、実質的なアクセプタ濃度は  $10^{19}$   $cm^{-3}$ 以下であると考えられる。しかし、高濃度の p-GaN 層は金属とのオーミック接触には良好に寄与するため、コンタクト抵抗低減を目的として結晶最表面に高濃度の p-GaN 層を形成した。上述の通り実質的なアクセプタ濃度が低いのに加え、膜厚が 10nm と薄いので確実にパンチスルー現象は発生する構造である。

$p^+$ -GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 10 nm

$n^-$ -GaN: Si (1.0x10<sup>16</sup> cm<sup>-3</sup>), 5  $\mu$ m

n-GaN: Si  $(2x10^{18} \text{ cm}^{-3})$ , 1  $\mu$ m

n-GaN 基板

図4.30 p-nダイオードの層構造

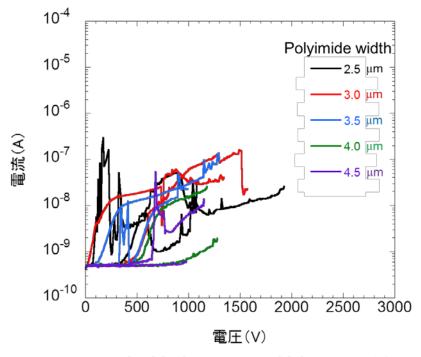

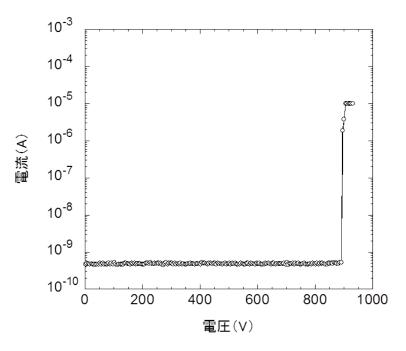

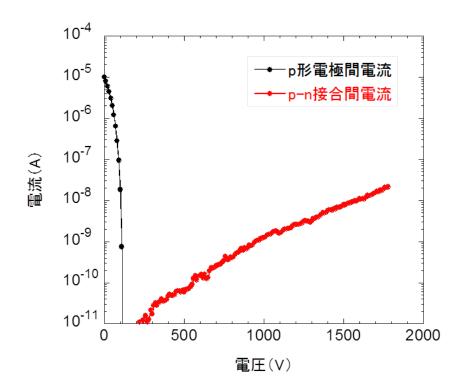

図 4.31 に逆方向 I-V 特性評価結果を示す。逆方向電圧約 900V 付近で電流が 急激に増加し、コンプライアンス電流値まで到達するが、p-n ダイオードは破壊 されず同素子を再測定しても同様の特性を示した。

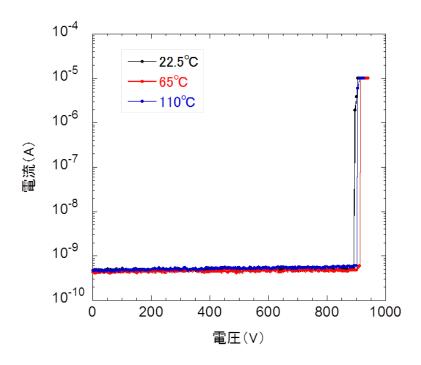

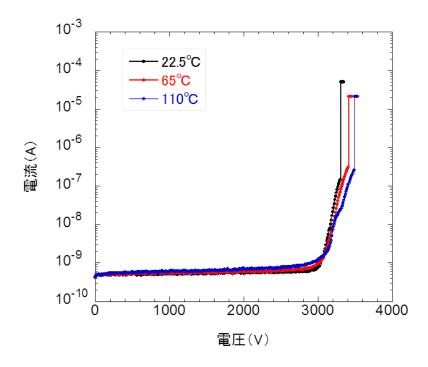

続いて同試料について降伏メカニズム解明のため逆方向 I-V 特性の温度依存性を評価した。図 4.32 に逆方向 I-V 特性の温度依存性評価結果を示す。測定温度は  $22.5^{\circ}$ C、 $65^{\circ}$ C、 $110^{\circ}$ Cで行った。耐圧は温度に依存せずほぼ同じ値となった。以上の結果から本試料においては約  $900^{\circ}$ V でパンチスルー現象が発生し、それによりアバランシェ降伏が抑制されていると考えられる。

図4.31 逆方向I-V特性評価結果

図4.32 逆方向I-V特性の温度依存性評価結果

#### 4.4.5 高耐圧仕様可逆性 p-n ダイオードの検討

上記結果を基に p-GaN 層アクセプタ濃度が低くなっている高耐圧仕様の結晶を用いて p-n ダイオードの試作を行った。図 4.33 に評価を行った試料の層構造を示す。また、表 4.1 に同試料および通常の p-GaN 層アクセプタ濃度を有する p-n ダイオード結晶の Transfer length method (TLM) により求めた p-GaN 層シート抵抗および p 形オーミック電極とのコンタクト抵抗の値を示す。

$p^+$ -GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm p-GaN: Mg (1.0x10<sup>18</sup> cm<sup>-3</sup>), 500 nm un-GaN (Si <2x10<sup>15</sup> cm<sup>-3</sup>), 5 μm  $n^-$ -GaN: Si (1.05x10<sup>16</sup> cm<sup>-3</sup>), 20 μm  $n^-$ -GaN: Si (1.6x10<sup>16</sup> cm<sup>-3</sup>), 5 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm

図4.33 p-nダイオードの層構造

表 4.1 p-n ダイオード結晶の TLM 評価結果

| 試料 No. | シート抵抗                     | コンタクト抵抗              |

|--------|---------------------------|----------------------|

|        | $(\mathrm{k}\Omega/\Box)$ | $(m\Omega{ m cm}^2)$ |

| 試料 A   | 130~340                   | 30~140               |

| 試料 B   | 36~38                     | 3~5                  |

試料 A は可逆性評価試料

試料 B は比較のために記載した高耐圧仕様の通常 p-GaN 層アクセプタ濃度を有する p-n ダイオード結晶

両試料共 p-GaN 層の Mg ドーピング濃度は  $1\times 10^{18}$   $cm^{-3}$  であるが、表 4.1 に 示した通り試料 A の p-GaN 層シート抵抗は試料 B に比べ  $4\sim 9$  倍程度大きくなっている。したがって試料 A の実質的なアクセプタ濃度は試料 B の  $1/4\sim 1/9$  程度になっていると考えられる。結果としてパンチスルー現象が発生するために 十分なアクセプタ濃度であると思われるので、試作に同試料を適用した。評価に 用いた p-n ダイオードの p 形電極径は  $60~\mu$  m である。

図 4.34 に順方向 I-V 特性評価結果を示す。比較のため試料 B の測定結果を同時に示した。試料 B に比べ試料 A は電圧  $3\sim4V$  付近で電流値が小さくなった。 試料 A では p-GaN 層のアクセプタ濃度が低いため電流値が減少したものと思われる。しかし、シート抵抗測定結果に見られた  $4\sim9$  倍程度の抵抗差に相当する電流値の減少は見られていない。これは、p-GaN 層の膜厚が n-GaN 層の膜厚

に比べ極めて薄いため、全体の抵抗に対する p-GaN 層の抵抗成分の影響割合が低い事と、後述するフォトンリサイクリング現象による電流増幅効果が全体の抵抗に対して支配的になるためであると考えられる。

図4.34 順方向I-V特性評価結果

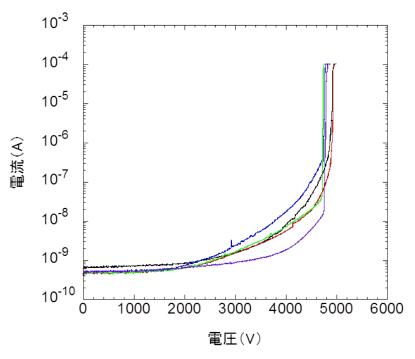

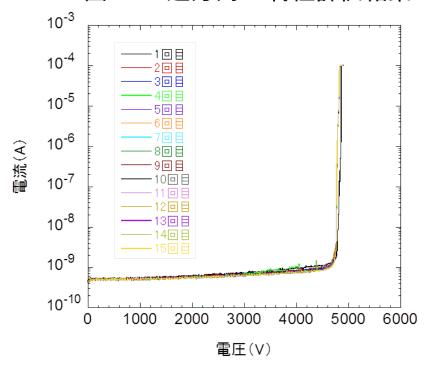

図 4.35 に逆方向 I-V 特性評価結果を示す。図中には複数素子の測定結果を示した。3kV 以上の電圧でリーク電流が若干大きいものの、測定した多くの素子で p-n ダイオードの破壊は観測されなかった。耐圧も 4.7~4.9kV と高く、このような高い耐圧で破壊が観測されない p-n ダイオードは過去に報告例がなく、極めて優れた結果であると考えられる。

図 4.36 に同じ素子を繰り返し逆方向 I-V 測定した結果を示す。15 回の繰り返し測定でも特性に変化は見られなかった。これはアバランシェ降伏が発生する前にパンチスルー現象が発生し、それによりアバランシェ降伏を抑制できているためであると思われる。

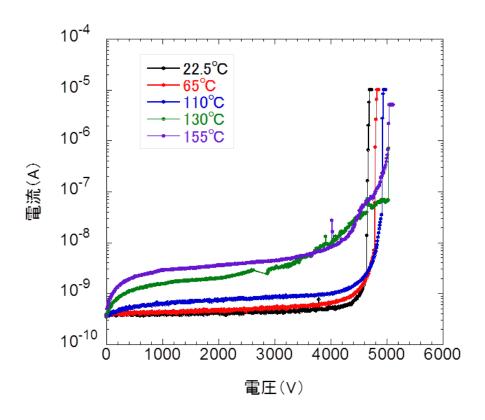

本試料においても降伏メカニズム解明のため逆方向 I-V 特性の温度依存性を評価した。図 4.37 に逆方向 I-V 特性の温度依存性評価結果を示す。図 4.32 に示した逆方向 I-V 特性の温度依存性評価結果と異なり、本試料の評価結果では逆方向 I-V 特性に温度依存性が見られた。しかし、測定時の温度を 130  $\mathbb{C}$  、155  $\mathbb{C}$  と さらに上げて測定したところ、耐圧は 130  $\mathbb{C}$  以上でほぼ同じ値を示した。以下に図 4.32 に示した結果と図 4.37 に示した結果の相違について考察を行う。

図 4.30 に示した層構造でアバランシェ降伏が発生する電圧 (p-n 接合界面の電界強度が約 3.3MV/cm となる時の電圧)の理論値は約 1.5kV と計算される。しかし、p-GaN 層 (p+-GaN 層)の膜厚を薄くすることでパンチスルー現象を発生させ、アバランシェ降伏は発生しにくい仕様となっている。パンチスルーが発生する電圧の実測値は図 4.31 に示した通り約 900V であり、アバランシェ降伏発生電圧と約 600V の差が存在する。この差のためパンチスルー現象発生電圧ではアバランシェ現象により発生するキャリアはほとんど存在せず、パンチスル

ー現象に対する影響も無視できる。一方、図 4.33 に示した層構造ではアバラン シェ降伏が発生する電圧の理論値は約 4.6kV で、図 4.35 に示した降伏電圧実測 値約 4.7~4.9kV とほぼ同等かむしろ低い電圧である。このため 4.7kV 付近では アバランシェ現象により相当数のキャリアが発生していると考えられる。この キャリアがパンチスルー現象の発生に影響を及ぼし、本来パンチスルー現象が 発生する電圧より低い電圧でパンチスルー現象を発生させていると考えられる。 アバランシェ現象には温度依存性が存在するため、測定時の温度が高くなると パンチスルー現象の発生をアシストするのに必要なキャリアが発生する電圧も 高くなり、パンチスルー現象による降伏電圧も高くなる。この傾向はパンチスル 一現象の発生をアバランシェ現象により発生するキャリアがアシストする関係 となる温度の間は継続し、その間降伏電圧に温度依存性が生じることとなる。し かし、さらに測定温度を上昇させると、温度依存性がほとんど見られないパンチ スルー現象が発生する電圧と、温度依存性の存在するアバランシェ降伏が発生 する電圧が乖離し、パンチスルー発生にアバランシェ現象が影響を及ぼさなく なる。このため本来パンチスルー現象が発生する電圧で降伏が発生し、以降温度 を上昇してもその電圧は変化しない。したがって 130℃以上の温度では降伏電 圧が飽和したものと思われる。図 4.37 より本試料のパンチスルー電圧は約 5.1kV であると考えられる。

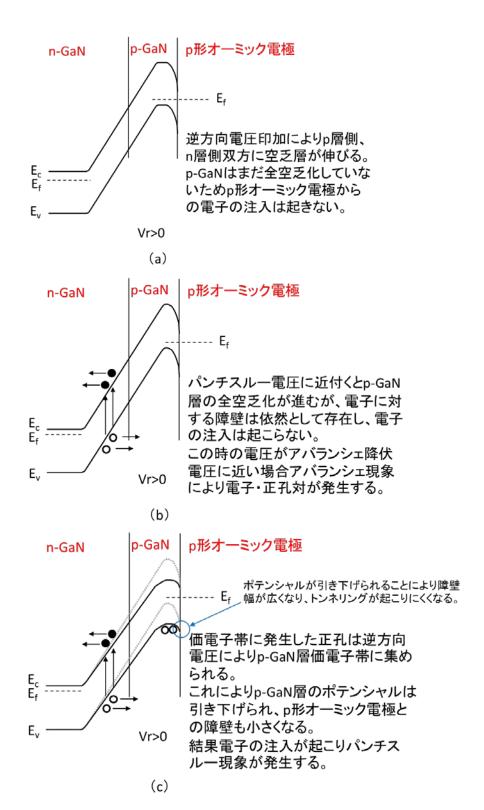

次にパンチスルー現象をアバランシェ現象がどのようにアシストするか考察する。図 4.38 に p-n ダイオードのバンド構造を示す。降伏電圧以下の逆方向電圧印加時には、p型電極と p-GaN 層伝導帯間に存在する障壁により電子の移動が妨げられ電流がほとんど流れないのは前述の通りである(図 4.38 (a))。アバランシェ降伏電圧に近い電圧を印加するとアバランシェ現象により電子・正孔

対が空乏層内で発生する。同電圧がパンチスルー電圧に近い値の時は、同電圧印 加時に p-GaN 層は空乏化が進み全空乏化に近い状態となる (図 4.38 (b))。空 乏層中に発生している正孔は印加電圧により p-GaN 層価電子帯に集められ、p-GaN 層に集まった正孔は p-GaN 層を正の電位に帯電させるため伝導帯障壁を 僅かに下げる方向に作用する。この作用により本来のパンチスルー電圧より低 い電圧で p-GaN 層は全空乏化しパンチスルー現象が発生することとなる (図 4.38 (c))。p 型電極と p-GaN 層の間には正孔に対する障壁が存在するが、厚さ が非常に薄いためトンネリング現象により正孔は容易に通過することが可能と なるという事は前述の通りであるが、前記 p-GaN 層伝導帯障壁を下げる作用に より正孔に対する障壁幅は広くなり、トンネリング現象は発生しにくくなるた め p-GaN 層価電子帯にはより正孔が集まりやすくなる。こうしたサイクルによ り、より低い電圧でパンチスルー現象が発生すると考えられる。測定温度が上昇 しアバランシェ降伏電圧が高くなると、アバランシェ現象による電子・正孔対の 発生より p-GaN 層の全空乏化が先に生じるため、上記のような p-GaN 層伝導 帯障壁を下げる作用は起こらず本来パンチスルー現象が発生する電圧で降伏が 起こる事となる。

以上が可逆性 p-n ダイオードの可逆性メカニズムであると考えているが、本メカニズムによればパンチスルー現象が発生する電圧をアバランシェ降伏が発生する電圧より若干高く設定することで、本構造における破壊耐圧を最大限引き出しつつ可逆性を持たせることが可能であると考えられる。本試料では結果として p-GaN 層アクセプタ濃度の低い結晶を用いて試作できたが、今後は意図的に p-GaN 層アクセプタ濃度を制御することでより高性能化が可能である。

図4.35 逆方向I-V特性評価結果

図4.36 逆方向I-V特性繰り返し測定結果

図4.37 逆方向I-V特性の温度依存性評価結果

図4.38 パンチスルー現象と アバランシェ降伏現象の関係

## 4.5 高抵抗 p-GaN 層を持つ高耐圧 p-n ダイオード

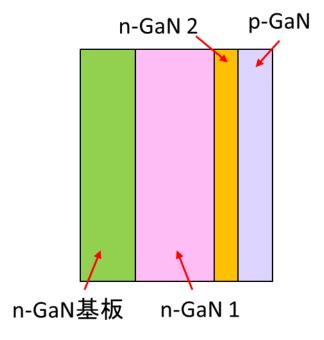

前述の通り、ガードリング構造 p-n ダイオードにおいて一定の高耐圧化が成し遂げられた。しかし、順方向特性において、ガードリング構造ではガードリング部分は一切特性に寄与せず、面積効率の点では課題が残されている。そこで、p-GaN 層の一部を高抵抗化することで同様の高耐圧効果が得られる p-n ダイオード構造の検討を行った。

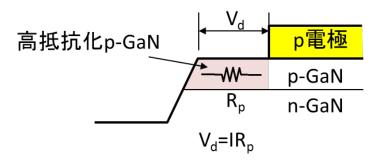

## 4.5.1 p-GaN 層の高抵抗化による高耐圧化

メサ型 p·n ダイオードにおいて、メサ端付近で最も電界が集中しその部分で破壊が発生するというのは既述の通りである。これは p 形電極直下の p·GaN 層とメサ端付近の p·GaN 層の電位がほぼ同電位であるということが前提である。図4.39 に示すように、p 形電極端からメサ端までの p·GaN 層の一部又は全部を高抵抗化することで、p 形電極端・メサ端間に電圧降下を発生させることが出来れば、n 形電極・メサ端間の電位を n 形電極・p 形電極端間の電位より小さくすることが出来、メサ端部分の電界集中を緩和することが可能であると考えられる。この時の電界集中緩和メカニズムは、ガードリング構造 p·n ダイオードのガードリング部メサ端付近の電界集中緩和メカニズムと同様である。

$R_p$ の値に応じた電圧降下 $V_d$ が生じる

図4.39 p-nダイオードの断面構造

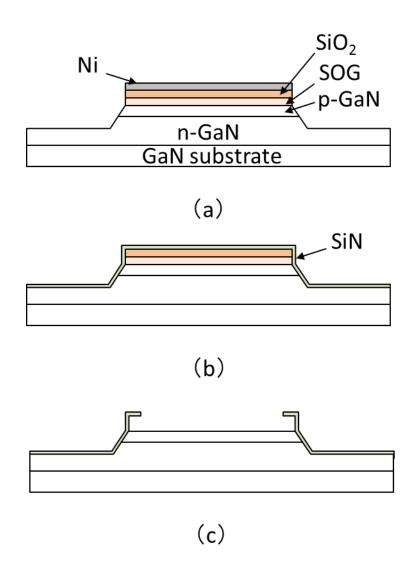

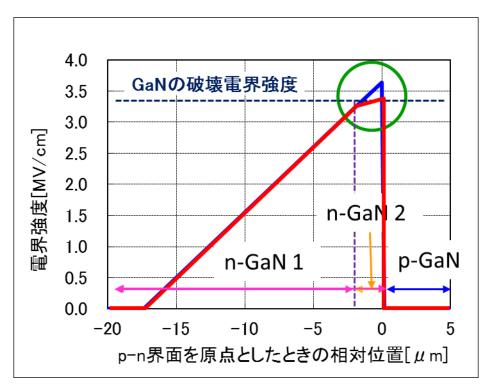

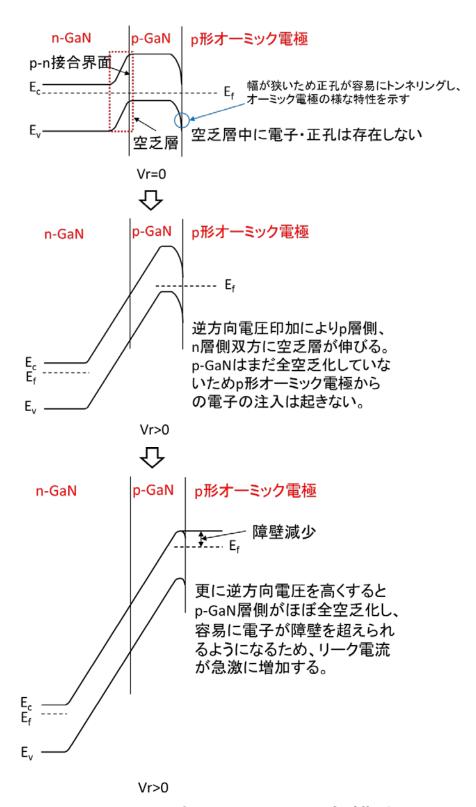

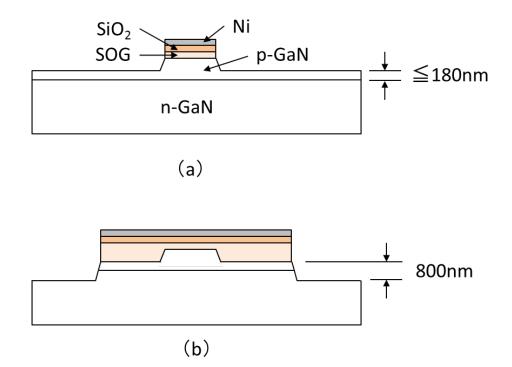

#### 4.5.2 p-GaN 層の薄層化による高抵抗化

図 4.40 に p-GaN 層薄層化 p-n ダイオードの断面構造を示す。前述の通り p-n 接合に逆方向電圧を印加すると、両者のアクセプタ、ドナー濃度に応じて接合界面から両側に空乏層が拡がる。電圧を増加していくとやがて p-GaN 層は全て空乏化する。この時 p-GaN 層は高抵抗化し電流をほとんど流さない。 p-n ダイオードの仕様耐圧付近の電圧印加時に p-GaN 層が全空乏化するように p 形電極端からメサ端までの p-GaN 層の一部又は全部を薄層化することで、薄層化部分は高抵抗化するため、耐圧付近の電圧印加時に p 形電極端-メサ端間に電圧降下を発生させることができる。 p 形電極端-メサ端距離や薄層化後の p-GaN 層膜厚を最適化することで所望の電圧降下値を得ることが可能である。 また、 p-GaN 層膜厚をより薄く制御することが可能となれば、 p 形電極端-メサ端距離をより近づけることが出来、 p-n ダイオードの面積効率も向上する。

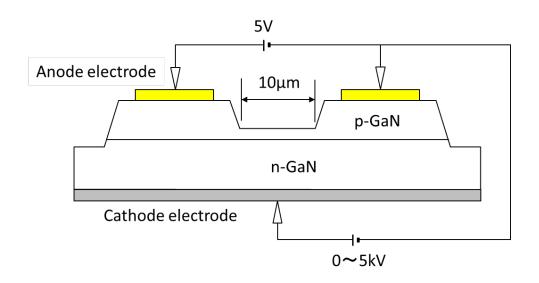

本研究では p 形電極端からメサ端までの p-GaN 層の一部をドライエッチング法でエッチングすることで、p-GaN 層の薄層化を実現した。図 4.41 に試作に用いた試料の層構造を示す。p-GaN 層の Mg ドーピング濃度が  $1\times10^{18}$  cm<sup>-3</sup> の場合、p-GaN 層の膜厚が約 180nm 以下であれば 3kV 以上の逆方向電圧印加により p-GaN 層は全空乏化する。したがって残 p-GaN 層膜厚 180nm 以下を目標にp-GaN 層のエッチングを行った。p 形電極端-メサ端間の p-GaN 層薄層化領域幅を  $5\sim80\,\mu$  m の範囲で変化し、p 形電極端-メサ端距離依存性の評価も行った。評価に用いた p-n ダイオードの p 形電極径は  $60\,\mu$  m である。

図4.40 p-GaN層薄層化p-nダイオード断面構造

図4.41 p-nダイオードの層構造

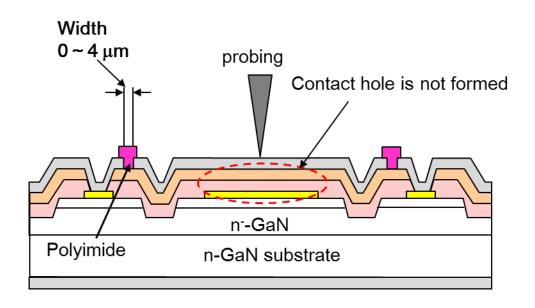

# 4.5.3 p-GaN 層薄層化 p-n ダイオードの作製プロセスフロー

図 4.42 に p-GaN 層薄層化 p-n ダイオードの作製プロセスフローを示す。活性化アニールの後、Ni マスクで p-GaN 層薄層化領域を p-GaN 層残膜厚 180nm以下を目標にドライエッチング法でエッチングした(図 4.42 (a))。

続いてメサ領域以外の部分を同じく Ni マスクでエッチング量 800nm 程度を目標にエッチングした ( $\boxtimes 4.42$  (b))。

以下のプロセスは従来通りである。

図4.42 p-GaN層薄層化p-nダイオードプロセスフロー

#### 4.5.4 空乏化した p-GaN 層の I-V 特性評価結果

p-n ダイオードの評価に先立ち、逆方向電圧印加時に薄層化 p-GaN 層が全空 乏化しているかどうか確認するため、逆方向電圧印加時の薄層化 p-GaN 層の I-V 特性について評価した。

図 4.43 に評価に用いた素子の構造図を示す。図に示すように p+-GaN 層上に所定の間隔を空けて p形オーミック電極を形成し、電極間の p-GaN 層を薄層化した(薄層化幅  $10\,\mu$  m)。裏面には n 形オーミック電極を形成した。p 形オーミック電極間に一定の電圧 5V を印加し、裏面 n 形オーミック電極に印加する逆方向電圧を変化した時の p 形オーミック電極間の電流を測定した。

図4.43 空乏化したp-GaN層のI-V特性評価用素子

図 4.44 に I-V 特性評価結果を示す。n 形オーミック電極に印加した逆方向電圧の変化に伴い p 形オーミック電極間の電流が減少し、逆方向電圧 120V 程度でほぼ 0 となった。その後 p-n 接合の逆方向リーク電流が増加し 1.8kV 付近で降伏したため、4kV 以上での p 形オーミック電極間電流の測定は出来なかったが、120V 以上ですでに p-GaN 層はほぼ全空乏化していると思われる。

図4.44 空乏化したp-GaN層のI-V特性評価結果

## 4.5.5 p-GaN 層薄層化 p-n ダイオードの特性評価結果

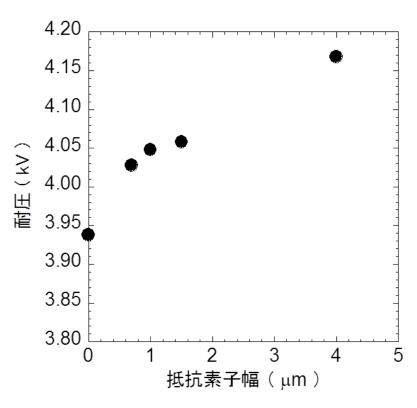

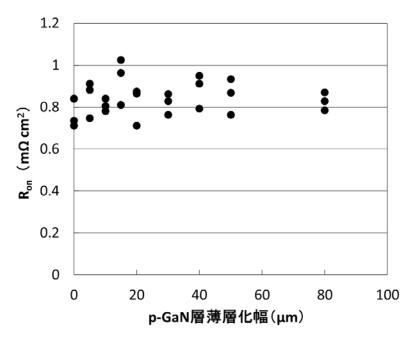

図 4.45 に順方向 I-V 測定時のオン抵抗の p-GaN 層薄層化幅依存性を示す。p-GaN 層薄層化の幅 0 が通常構造 p-n ダイオードの値である。通常構造 p-n ダイオードの値に比べ、p-GaN 層薄層化 p-n ダイオードは僅かではあるがオン抵抗が増加しているように見えるが、素子間ばらつきのため明確な傾向はない。

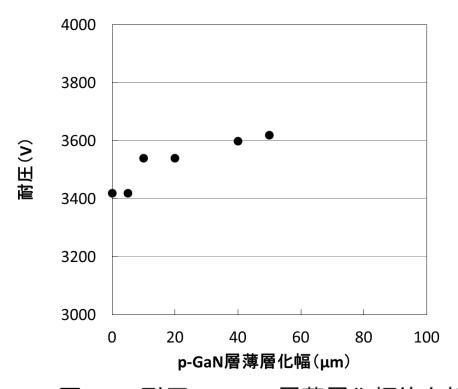

図 4.46 に耐圧の p-GaN 層薄層化幅依存性を示す。通常構造 p-n ダイオードの値に比べ、p-GaN 層薄層化 p-n ダイオードは  $100\sim200$ V 程度耐圧の向上が見られた。 ガードリング構造 p-n ダイオードにおいて耐圧の向上は 200V 程度であり、本検討の結果は概ね妥当な結果と思われる。なお、p-GaN 層薄層化幅 80  $\mu$  m の素子は測定した素子全てで耐圧が 3kV 以下であった。

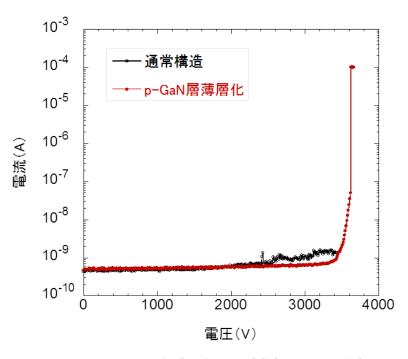

図 4.47 に通常構造 p-n ダイオードと p-GaN 層薄層化 p-n ダイオードの逆方向 I-V 特性評価結果を示す。通常構造 p-n ダイオードがいわゆる頓死という形で破壊が発生しているのに対し、p-GaN 層薄層化 p-n ダイオードは破壊が発生しない素子が多く見られた。通常構造 p-n ダイオードに関しては典型的なアバランシェ降伏と考えられるが、p-GaN 層薄層化 p-n ダイオードは別のメカニズムが想定される。そこで p-GaN 層薄層化 p-n ダイオードについて逆方向 I-V 特性の温度依存性評価を行った。図 4.48 に p-GaN 層薄層化 p-n ダイオードの逆方向 I-V 特性温度依存性評価結果を示す。温度の上昇と共に耐圧が増加するアバランシェ降伏の特長を示した [85]。アバランシェ降伏が発生しているのに p-n ダイオードの破壊が起こらないのは、アバランシェ耐量が向上しているためであると考えられる。4.5.1 項で説明した通り p-GaN 層薄層化 p-n ダイオードではメ

サ端付近の電界集中が緩和されている事が期待できる。一方 p 形電極直下の p-GaN 層は元々電界は分散しており、部分的に電界が集中している場所は存在しないと考えられる。アバランシェ降伏による p-n ダイオードの破壊は、電界が一部分に集中している時にその場所で起こりやすいと推定され、p-GaN 層薄層化 p-n ダイオードのように全体的に電界が分散している状況では破壊に至りにくいと思われる。しかし、全ての素子で一律に電界が分散されているわけではなく、初回測定や繰り返し測定を行うことで破壊が生じる素子も相当数存在するため、層構造やデバイス構造の最適化は必要であると考えられる。

図4.45 オン抵抗のp-GaN層薄層化幅依存性

図4.46 耐圧のp-GaN層薄層化幅依存性

図4.47 逆方向I-V特性評価結果

図4.48 逆方向I-V特性の温度依存性評価結果

# 4.5.6 p-GaN 層薄層化 p-n ダイオードと可逆性 p-n ダイオードの関係性

p-GaN 層薄層化 p-n ダイオードと前項で述べた可逆性 p-n ダイオードは、p-GaN 層を全空乏化するという点で共通する。そこで両者の特長について比較し、構造的に共有できる部分はないか検証した。

まず可逆性 p-n ダイオードであるが、降伏時に p-n ダイオードの破壊が発生しにくいというのが最大の特長である。その名の通り可逆性を有するというのは実用上非常に有効な特徴であり、それを 4kV を遥かに超える電圧で実現できるのは注目に値する。また、その特性を p-GaN 層の Mg ドーピング濃度もしくは膜厚の調整のみで得られるため、プロセス上の問題点も存在しない。図 4.37 に示した通りパンチスルー電圧をアバランシェ降伏電圧より若干高く設定してもアバランシェ降伏による p-n ダイオードの破壊は生じにくく、層構造の設計裕度も高い。

次に p-GaN 層薄層化 p-n ダイオードであるが、メサ端での電界集中を緩和することが出来るので、結晶が持つ耐圧に関する潜在能力を 100%引き出すことができる可能性を秘めている。また、その最大耐圧で可逆性も得られるという特徴を有している。

以上の特長から、p-GaN 層薄層化 p-n ダイオードでメサ端での電界集中を緩和し、結晶が有する耐圧に関する潜在能力を可能な限り引き出した状態でパンチスルー電圧を設定する事でより高い降伏電圧で可逆性を得ることが可能となる。

#### 4.6 まとめ

GaN 基板上 p-n ダイオードの高耐圧化を目的としてダイオード層構造の検討を行った。オン抵抗の増大を最小限に抑制しつつ高耐圧化が可能なトリプルドリフト層構造を適用し、耐圧 4.7kV を達成した。

また、p-n ダイオードのメサ端付近での電界集中を緩和するため、ガードリング構造 p-n ダイオードの検討を行った。メイン p-n ダイオード部分とガードリング部分の間に抵抗素子を挿入することで生じる両者の間の電圧降下を利用して、ガードリング部分のメサ端付近の電界集中を緩和し、通常構造 p-n ダイオードに比べ約 200V 高い耐圧 5kV が得られた。

続いて、降伏時の p-n ダイオードの破壊を防止し、可逆性を実現するためパンチスルー現象を利用した可逆性 p-n ダイオードの検討を行った。p-GaN 層のアクセプタ濃度が低い結晶を用い、降伏電圧に近い逆方向電圧印加時に p-GaN 層を全空乏化することでパンチスルー現象を発生させ、p-n ダイオードの可逆性を実現した。15 回の繰り返し測定でも破壊が生じない約 4.8kV 耐圧の p-n ダイオードが得られた。

また、ガードリング構造 p-n ダイオードの改良版として p-GaN 層薄層化 p-n ダイオードの検討を行った。p 電極端-メサ端間の p-GaN 層を薄層化することで 逆方向電圧印加時に p 電極端-メサ端間の p-GaN 層を全空乏化が可能となり、 それにより薄層化部分の p-GaN 層が高抵抗化し、p 電極端-メサ端間に電圧降下が発生する。本構造によりメサ端付近の電界集中が緩和し、通常構造 p-n ダイオードに比べ約 200V の耐圧向上効果が得られた。これはガードリング構造 p-n

ダイオードによる耐圧向上効果とほぼ同程度の効果であった。

#### 第5章 パワー半導体デバイスの大電流化

#### 5.1 はじめに

円形電極構造の GaN 基板上 p-n ダイオードは順方向 I-V 特性電流密度の電極面積依存性を有する。その理由はフォトンリサイクリング現象で説明が可能である。本章では 4 つの異なる電流密度領域からなるモデルで実測値とのフィッティングを行い、フォトンリサイクリング現象による順方向 I-V 特性電流密度の電極面積依存性の説明の妥当性について述べた。また、フォトンリサイクリング現象を利用した大電流化のための櫛形電極構造 p-n ダイオードの提案を行い、その特性評価結果について述べた。

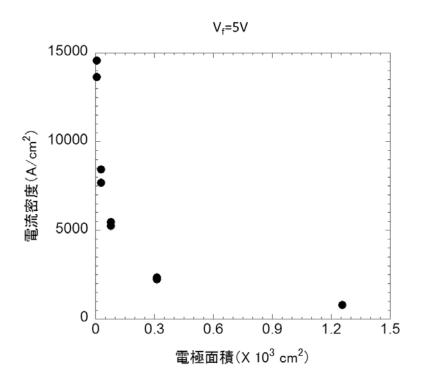

### 5.2 電流密度の p 形電極面積依存性

図 5.1 に順方向電圧 5V 時の電流密度の p 形電極面積依存性を示す。評価に使用した試料の層構造は図 5.2 に示す通りである。通常電流密度は、印加電圧が一定ならば電極面積に関わらず一定である。しかし本研究で評価を行った GaN p・n ダイオードの電流密度は、図から明らかなように、面積の増加と共に減少している。図 4.4 に示した通り、p 形電極端からメサ端までは一定の距離が存在し、その距離が同じならば、その部分がメサ面積全体に占める面積の割合は p 形電極面積が大きくなるほど小さくなる。p 形電極から注入された順方向電流は、p・GaN 層で横方向に拡がり、p 電極端メサ端間の面積が全体に占める割合が大きくなる p 形電極面積の小さい素子ほど電流密度が大きくなるということが考えられるが、図 3.15 に示した通り、オン抵抗の p 電極端メサ端距離依存性は観測されていないので、p・GaN 層内での電流の横方向拡がりは小さいと考えられる。したがって、図 5.1 に示した電流密度の p 形電極面積依存性は、p・GaN 層内での電流の横方向拡がりとは別のメカニズムが働いていると考えられる。

図5.1 電流密度のp形電極面積依存性

p<sup>+</sup>-GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm p-GaN: Mg (1.0x10<sup>18</sup> cm<sup>-3</sup>), 500 nm n<sup>-</sup>-GaN: Si (1.3x10<sup>16</sup> cm<sup>-3</sup>), 10 μm n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm n-GaN 基板

図5.2 p-nダイオードの層構造

### 5.3 フォトンリサイクリング現象

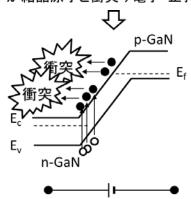

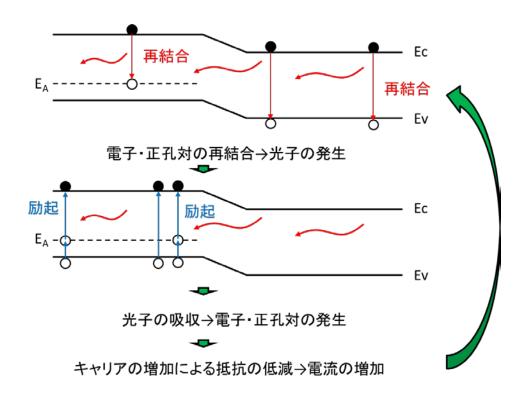

フォトンリサイクリング現象とは、日立製作所中央研究所の望月氏らによって 提唱された現象である [86-88]。図 5.3 にフォトンリサイクリング現象を説明す るバンド構造図を示す。

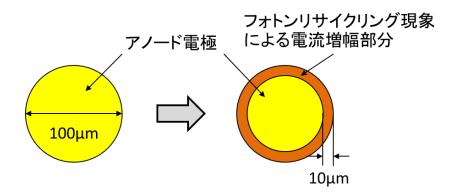

GaN 中に存在する電子・正孔対は順方向電圧印加により順方向電流として注入され、やがて再結合する。GaN は直接遷移型の半導体であるため、再結合の際光子を発生する。その光子を吸収した価電子帯中の電子は Mg アクセプタをイオン化し、価電子帯中に正孔を生成する。正孔の増加により p-GaN 層の抵抗が低減し電流が増加する。増加した正孔もやがて電子と再結合し光子を発生する。その光子を吸収することで正孔が増加するというサイクルを繰り返し、電流は増加する。このような光子による電流の増幅作用をフォトンリサイクリング現象という。円形電極の p-n ダイオードでは、このような現象が電界強度の大きい電極周辺で特に強く発生すると考えられている。そして、フォトンリサイクリング現象が強く発生する電極周辺部分の幅は電極径に関わらず一定と考えられるため、フォトンリサイクリング現象が強く発生している領域が占める面積割合が大きい、p 形電極面積の小さい素子で電流密度が大きくなると思われる。

図 5.4 に順方向電流注入時の発光を観察した結果を示す。順方向電圧 4V で強い紫外光の発光が観察された。この時顕微 Electroluminescence (EL) マッピング像から求めた p-n ダイオードの中心付近と周辺付近の発光強度比は 2 倍以上と観測されており、発光パターンからも電極周辺部への電流集中モデルを裏付ける結果が得られている [89]。

# 図5.3 フォトンリサイクリング現象説明図

図5.4 p-nダイオードの発光

### 5.4 p 形電極内電流分布

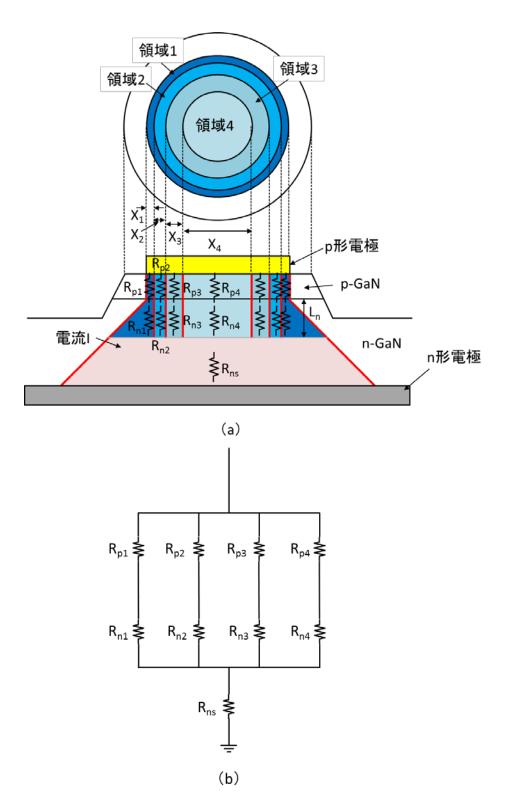

順方向電流注入時に電極周辺部分の発光強度が大きくなることは上述の通り確認できたが、実際に電流が p 形電極内でどのように分布しているか概算するため、図 5.5 (a) に示すようなモデルを用いて、抵抗の電極面積依存性実測値とのフィッティングを行った [90]。電流密度は階段状ではなく連続的に分布すると思われるが、本研究では電流密度値の異なる 4 つの領域に分割した多段モデルを用いた。フィッティングを簡易化するため、下記の通りモデルにいくつかの仮定を用いた。

- ① p 形電極から p-GaN 層に注入された電流は、p-GaN 層内では横方向に拡散しない。

- ② p-GaN 層から n-GaN 層へ注入された電流は、拡散長  $L_n$  の間は最外殼の領域のみ一定の角度で横方向に拡散する。その他の領域では横方向の拡散は生じない。

- ③ Ln後は全領域の電流が交じり合い等しい一つの値となる。

図 3.15 の結果から①の仮定は推定される。また、順方向電圧で注入された電流は、基板方向に向かって  $45^\circ$  の角度で拡がると言われており [28]、そこから ②の仮定を設定した。

上記の仮定に基づくフィッティングモデルの等価回路を図 5.5 (b) に示す。フィッティングは、p-GaN 層内での各領域の幅  $X_1 \sim X_4$ 、p-GaN 層内での各領域の直列抵抗  $R_{p1} \sim R_{p4}$ 、拡散長  $L_n$  内における n-GaN 層内での各領域の直列抵抗  $R_{n1} \sim R_{n4}$ 、拡散長  $L_n$  以降の各領域の電流値が交じり合った後の合成抵抗値  $R_{ns}$ 、および拡散長  $L_n$  をパラメータとして、実測抵抗値と一致するように各パラメータを変化して行った。図 5.6 にフィッティングを行った試料の層構造を示す。異なる層構造で比較するため、図に示すような 2 種類の試料の測定結果でフィッティングを行った。p-n ダイオードの実測値は、電極径  $10 \sim 400~\mu$  m のものを用いた。

図5.5 順方向電圧印加時の電流分布モデル

p<sup>+</sup>-GaN: Mg (2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm

p-GaN: Mg (1.0x10<sup>18</sup> cm<sup>-3</sup>), 500 nm

n<sup>-</sup>-GaN: Si (1.3x10<sup>16</sup> cm<sup>-3</sup>), 10 μm

n-GaN: Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm

n-GaN 基板

### (a) 試料1

$p^+$ -GaN: Mg (2x10 $^{20}$  cm $^{-3}$ ), 30 nm p-GaN: Mg (1.0x10 $^{18}$  cm $^{-3}$ ), 500 nm un-GaN (Si <2x10 $^{15}$  cm $^{-3}$ ), 2  $\mu$ m  $n^-$ -GaN: Si (0.8x10 $^{16}$  cm $^{-3}$ ), 23  $\mu$ m n-GaN: Si (2x10 $^{18}$  cm $^{-3}$ ), 2  $\mu$ m n-GaN 基板

## (b) 試料2

図5.6 p-nダイオードの層構造

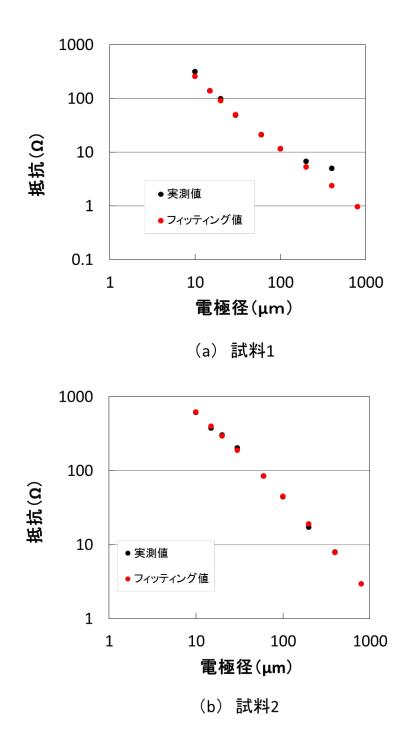

図 5.7 (a) および (b) に抵抗実測値とフィッティング値の電極径依存性を示す。実測値は順方向電圧 5V 時の値を用いた。電極径  $100\,\mu$  m 以下の素子では実測値とフィッティング値が比較的良く一致している。しかし試料 1 では電極径  $200\,\mu$  m 以上の素子でずれが生じ始め、実測値に比べフィッティング値が小さな値となっている。電極径の大きな素子に関してはフォトンリサイクリング現象の影響の割合が減少するため、フォトンリサイクリング現象による電流増幅効果が小さくなると考えられるのは前述の通りであり、本モデルによるフィッティングはそれを考慮した構造で行ったが、ずれが生じた電極径が大きい素子ではそれ以外にも電流を減少させるメカニズムが存在すると考えられる。ここで検討を行っている p-n ダイオードの電流値は電極面積に比例はしないものの、電極面積が大きくなれば増加はするので、電極面積の増加、すなわち電流値の増加に伴い p-n ダイオードは発熱すると思われる。この発熱により p-n ダイオードの抵抗が増加し電流値が減少することが予想されるが、現状検証は出来ていない。今後確認を要する。

表 5.1 にフィッティングにより求めた各領域幅  $X_1 \sim X_3$  の値を示す。 $X_1 \sim X_3$  の合計幅はおおよそ  $11 \, \mu$  m となった。望月氏らは TLM の矩形パターン電極を用いた実験等でフォトンリサイクリング現象により電流が増加する領域を約  $10 \, \mu$  m と推定している [91]。望月氏らの実験では、その領域では抵抗が一様であるという仮定のもと計算を行っているが、本研究ではより実デバイスに近づけるため多段モデルを用いてその領域を細分化して計算した。しかし、多段モデルを用いても両者の計算結果に大きな相違は見られなかった。

表 5.1 フィッティングから求めた電流増幅領域幅

| 試料   | X <sub>1</sub> (μ m) | X <sub>2</sub> (μ m) | X <sub>3</sub> (μ m) |

|------|----------------------|----------------------|----------------------|

| 試料 1 | 1.1                  | 3.9                  | 6                    |

| 試料 2 | 1.1                  | 3.9                  | 6                    |

図5.7 4領域モデルによる抵抗フィッティング結果

表 5.2 および表 5.3 にフィッティングから求めた各領域毎の電流密度を示す。電極中心付近の最も電流密度が小さい部分に比べ、電極周辺部分のフォトンリサイクリング現象により電流が最も増加していると考えられる領域は、試料 1で9倍程度、試料 2で 20 倍程度電流密度が大きくなっている。これに対し、顕微 EL マッピング像から求めたダイオードの中心付近と周辺付近の発光強度比は 2 倍程度となっている。フィッティングは 4 つの領域に分割した多段モデルで行っているが、領域 2 および領域 3 の電流密度を考慮しても両者の結果は大きく異なる。この差は、顕微 EL マッピングにより求めた強度比は、ステージのステップ送りと光学系の解像度の制限からやや小さい値となってしまうのと、フィッティングに用いたモデルもいくつかの仮定が含まれているのに加え、不連続の多段モデルを用いている等必ずしも最適化されていないのが原因と思われる。また、同じ領域でも電極径が異なると電流密度も異なる結果となった。これはフォトンリサイクリング現象以外にも電極面積に対し電流密度依存性をもたらす原因が存在していることを示唆している。本研究で得られた様々な測定結果からフィードバックを行い、より最適なモデルを検討する。

表 5.2 フィッティングから求めた各領域毎の電流密度(試料 1)

| 電極径(μ | 領域 1 ( μ m) | 領域 2 ( μ m) | 領域 3 (μm) | 領域 4 (μ m) |

|-------|-------------|-------------|-----------|------------|

| m)    |             |             |           |            |

| 10    | 41.0        | 13.7        |           |            |

| 15    | 40.0        | 13.5        | 9.63      |            |

| 20    | 39.0        | 13.2        | 9.41      |            |

| 30    | 36.9        | 12.5        | 8.94      | 3.94       |

| 60    | 31.7        | 10.8        | 7.71      | 3.40       |

| 100   | 26.4        | 9.0         | 6.43      | 2.83       |

| 200   | 18.6        | 6.34        | 4.53      | 2.00       |

| 400   | 12.3        | 4.21        | 3.01      | 1.33       |

表 5.3 フィッティングから求めた各領域毎の電流密度 (試料 2)

| 電極径(μ | 領域 1 ( μ m)                               | 領域 2 ( μ m) | 領域 3 (μm) | 領域 4 (μ m) |  |  |

|-------|-------------------------------------------|-------------|-----------|------------|--|--|

| m)    | 電流密度 (10 <sup>4</sup> A/cm <sup>2</sup> ) |             |           |            |  |  |

| 10    | 24.8                                      | 1.07        |           |            |  |  |

| 15    | 23.4                                      | 1.05        | 0.973     |            |  |  |

| 20    | 22.3                                      | 1.04        | 0.961     |            |  |  |

| 30    | 20.8                                      | 1.01        | 0.936     | 0.902      |  |  |

| 60    | 18.0                                      | 0.933       | 0.863     | 0.832      |  |  |

| 100   | 15.7                                      | 0.836       | 0.773     | 0.745      |  |  |

| 200   | 12.0                                      | 0.656       | 0.607     | 0.585      |  |  |

| 400   | 8.53                                      | 0.473       | 0.437     | 0.422      |  |  |

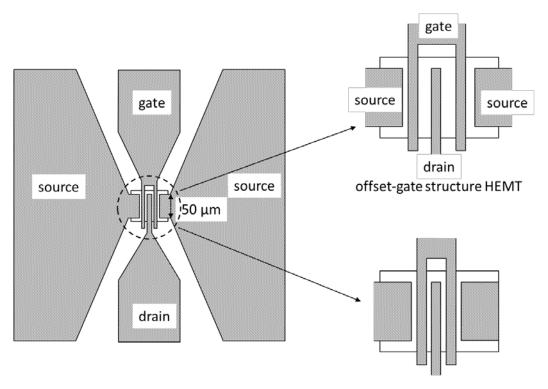

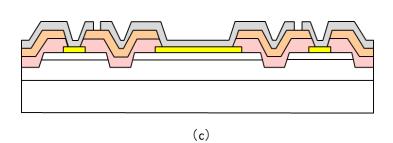

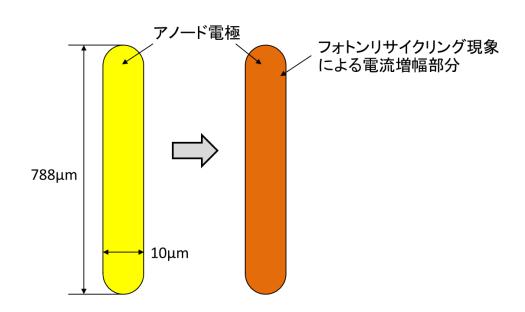

### 5.5 櫛形電極構造による大電流化

p-n ダイオードにより大きな電流を流すためには、アノード電極の面積を大きくする必要がある。しかし、電極を大きくすると p-n ダイオードの中心付近でフォトンリサイクリング現象による電流増幅効果が得られにくくなるため、より効率的に電極面積増加分の電流を増加させることは困難である事は前述の通りである(図 5.8 (a))。しかし、電流増幅効果が得られにくい、電極端から 10  $\mu$  m より内側の電極面積を可能な限り小さくし、かつ電極全体の面積を増加することが出来れば、効率的に電極面積増加分の電流を増加させることが可能である。そこで、図 5.8 (b) に示すような櫛形電極構造 p-n ダイオードの検討を行った。例えば櫛形電極の横幅を  $20\,\mu$  m 以下に設定し、縦幅を大きくすれば、電極全体でフォトンリサイクリング現象による電流増幅効果が得られ、かつ電極面積も大きくすることが可能となる。

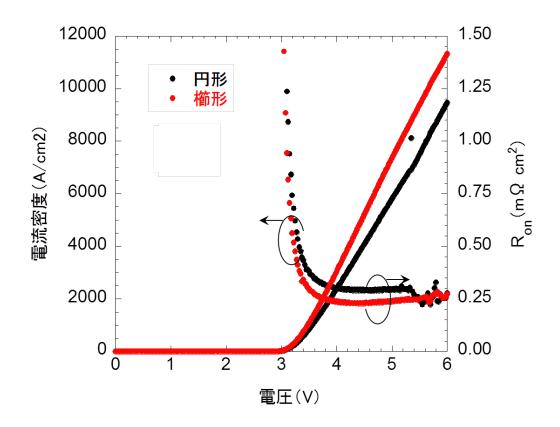

評価に用いた試料の層構造は図 5.9 に示す通りである。試料の寸法は、櫛形電極構造 p-n ダイオードは図 5.8 (b) に示した横幅  $10\,\mu$  m、縦幅  $788\,\mu$  m で、比較のため電極径  $100\,\mu$  m の円形電極構造 p-n ダイオードも測定した。両者の電極面積はほぼ等しい。

図 5.10 に両者の順方向 IV 特性を示す。櫛形電極構造 p-n ダイオードは、円形電極構造 p-n ダイオードに比べ約 20%オン抵抗が低減した。ここで、再度図 5.1 の電流密度の電極面積依存性評価結果を参照すると、電極径  $100\,\mu$  m の素子に比べ、例えば電極径  $30\,\mu$  m の素子は電流密度が 2 倍以上となっている。電極径  $30\,\mu$  m の素子は中心部分にフォトンリサイクリング現象による電流増幅効果が生じていない領域が存在すると思われる。それにもかかわらず電極径  $100\,\mu$  m の素子に比べ電流密度が 2 倍以上となっていることから、よりフォトンリサイクリング現象による電流増幅効果が大きいと考えられる櫛形電極構造 p-n ダイオードでは、電流密度が 2 倍以上となることが期待できるが、20%程度の向上に留まっている。原因の一つは p-n ダイオードの発熱による抵抗の増加が考えられるが、さらなる検証を要する。

電極中心部分で電流増幅が起こらないため 効果的に電流を増加させることが困難

### (a) 円形構造p-nダイオード

電極全体で電流増幅が起こるため効果的に 電流を増加させることが出来る

(b) 櫛形構造p-nダイオード

## 図5.8 p-nダイオードの電極構造

p<sup>+</sup>-GaN:Mg (1.2x10<sup>20</sup> cm<sup>-3</sup>), 30 nm

p-GaN:Mg (1.5x10<sup>18</sup> cm<sup>-3</sup>), 400 nm

n<sup>-</sup>-GaN:Si (0.9x10<sup>16</sup> cm<sup>-3</sup>), 1.5 μm

n-GaN:Si (2x10<sup>18</sup> cm<sup>-3</sup>), 2 μm

n-GaN 基板

図5.9 p-nダイオードの層構造

図5.10 順方向I-V特性評価結果

### 5.6 p 形電極横方向抵抗の影響による電極周辺部分の電圧降下

上述の櫛形電極構造 p-n ダイオードで電流増幅効果が目論見通り得られていない理由として、p 形電極横方向抵抗について検討した。現在 p-GaN 層上に形成されている電極金属は、p-GaN 層表面から順に Pd(200nm)、Ni(50nm)、Ti(30nm)、Al(250nm)という構造になっており、合計膜厚は 530nm である。一方 p-n ダイオードの径は、上述の評価素子では円形電極構造 p-n ダイオードで  $100\,\mu$  m、櫛形電極構造 p-n ダイオードでは長辺方向で 788nm となっている。つまり櫛形電極構造 p-n ダイオードで中心付近に測定プローブを接触させた場合、電極端部分までは約  $390\,\mu$  m の距離が存在し、それは電極膜厚の 780 倍程度になる。抵抗も 780 倍程度になると考えられ、電極中心から電極端の間で相応の電圧降下が発生し、電極端では所望の電圧が印加されてない事が予想される。そこで順方向電圧印加時の電極中心から電極端の間の電圧を測定評価した。

図 5.11 に測定方法を示す。通常測定通り p 形電極中心に針を立て順方向電圧を印加する。同時に電極端にも針を立て、中心に立てた針と電極端に立てた針の間の電圧を測定した。測定素子の p 形電極径は  $100\sim800\,\mu$  m の円形電極構造 p-n ダイオードを用いた。

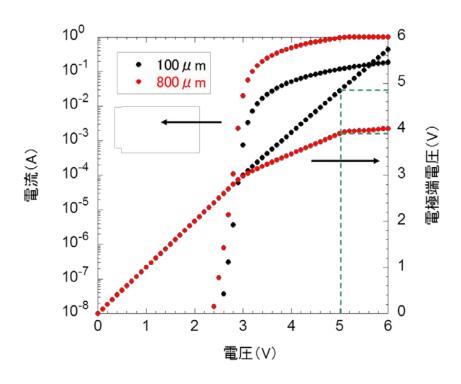

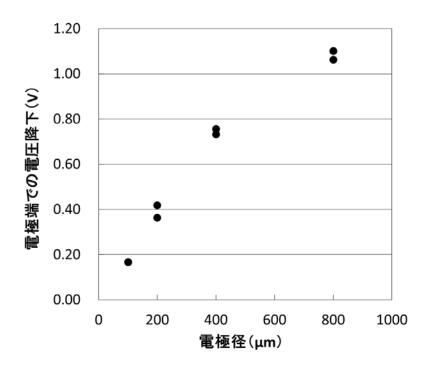

図 5.12 に p 形電極径  $100 \mu$  m および  $800 \mu$  m 素子の順方向 I-V 特性を示す。 縦軸第 2 軸は電極端での電圧を示している。なお、 $800 \mu$  m 素子では順方向電圧 5V を超えた辺りで電流値が 1A を超えコンプライアンス電流に達しているため、5V を超えた順方向電圧印加時の電極端での電圧値も参考程度に参照していただきたい。また、図 5.13 に順方向電圧 5V 時の電極端における電圧降下の p 形電極径依存性を示す。 p 形電極径の増加に伴い電圧降下値は増加し、 p 形電極径  $100 \mu$  m の素子では電極端での電圧降下は 0.2V 程度であるのに対し、 p 形電極径  $800 \mu$  m の素子では 1V 以上の電圧降下が見られた。

以上の結果から p 形電極径 100 μ m の円形電極構造 p-n ダイオードでは電極 全体に比較的均等に電圧が印加されているのに対し、長辺方向の寸法が 788nm である櫛形電極構造 p-n ダイオードではその大部分で電圧が有効に印加されて いない事が考えられる。櫛形電極構造 p-n ダイオードで電流増幅効果が目論見通り得られていないのは、測定の際に p 形電極上で発生する電圧降下が理由の全てであるとは言えないが、大きな影響を及ぼしていると思われる。また、上記の4つの異なる電流密度領域からなるモデルと実測値とのフィッティングにおいて、電極径200 $\mu$ m 以上の素子で実測値とのずれが生じているが、そのずれは電極端での電圧降下が原因の一つであると考えられる。メッキ等を利用し電極膜厚をより厚くする、より抵抗率の低い金属を使用する等の対策を講じる必要がある。また、当面の測定方法として、電極全体に一様に電圧を印加できる測定系を検討する必要もある。

図5.11 p-nダイオード断面構造

図5.12 順方向I-V測定時の電極端電圧測定結果

図5.13 電極端での電圧降下電極径依存性

#### 5.7 まとめ

GaN 上 p-n ダイオードに見られる電流密度の電極面積依存性の原因について説明するため、4つの異なる電流密度領域を有するモデルにより実測値とのフィッティングを行った。その結果 p 形電極端から約  $10\,\mu$  m 幅で電流密度の大きな領域が存在することが確認できた。これは望月氏らにより提唱されたフォトンリサイクリング現象との整合性が取れた結果である。しかし電極径  $200\,\mu$  m 以上の p-n ダイオードではモデルに一致しない素子も見られ、フォトンリサイクリング現象のみでは説明が困難である事が分かった。

この結果を基に p-n ダイオードの大電流化を図るため櫛形電極構造 p-n ダイオードの試作を行い評価した。その結果、同じ電極面積の円形電極構造 p-n ダイオードに比べオン抵抗が約 20%減少した。しかし、この結果も期待値に比べ低い電流となっており、やはりフォトンリサイクリング現象のみでは説明が困難である事が改めて確認された。

フォトンリサイクリング現象以外で電流密度の電極面積依存性が生じる原因を解析するため、p 形電極の中心と電極端間での電圧降下を測定した。その結果、電極径 800  $\mu$  m の素子で 1V 以上の電圧降下が生じている事が分かった。この事から電流密度の電極面積依存性が生じる原因は、少なくとも、

- ① フォトンリサイクリング現象

- ② p-n ダイオード面積増加に伴う電流増加による温度上昇が原因の抵抗の増大

- ③ p 形電極電極端での電圧降下

- の3つの原因の複合であると考えられる。

### 第6章 結論

### 6.1 結言

本論文では、化合物半導体を用いた高速デバイスおよびパワーデバイスのデバイスプロセスの研究について述べた。

第2章のテーマは高速デバイスの研究である。高速デバイスとしてオフセット ゲート P-HEMT および同 P-HEMT を搭載した MMIC の開発を行い以下の結 論を得た。

- ① ノンオフセットゲート構造に比べ  $C_{gd}$  を約 25%低減することが出来、  $f_{max}$ =170GHz が得られた。

- ② シミュレーションにより求めた MAG は、周波数 77GHz においてノンオフセット構造 HEMT に比べ 3dB 高い 9.2dB が得られた。

- ③ 車載レーダ用ミリ波 MMIC への適用を目的とし、同 P-HEMT を用いた 3 段パワーアンプを試作した結果、周波数 77GHz において小信号利得 16.5dB が得られた。

- ④ 同パワーアンプについて簡易寿命試験を行ったところ、試料温度 175℃で 測定時間 160hr においても小信号利得の減少は見られず一定の値となった。 これは、活性化エネルギーを 1.5eV と仮定して寿命を計算すると、85℃で 30 年の寿命に相当する。

第3章のテーマはパワーデバイスのデバイスプロセスの研究である。現状のp-nダイオード作製プロセスにおいて明らかとなった問題点について、それらを改善する検討を行い以下の結論を得た。

- ① p型電極上に形成されるコンタクトホールに関し、従来のウエットエッチング法から新たにドライエッチング法の検討を行い、良好な Field Plate (FP) 電極形状が得られた。

- ② メサ形成時のドライエッチングダメージに関し、ドライエッチング時のマスクとして 3 層マスク構造を適用し、p-GaN 層表面のドライエッチングダメージ低減を図り、従来プロセスに比べ約 15%オン抵抗を低減した。

- ③ 3層マスク構造では対応できないメサ側面のドライエッチングダメージに 関しては、メサ側面を SiN 膜で保護した状態で 850℃ 30 分のアニールを 行い、耐圧の向上を果たした。

- ④ ドライエッチング時の加速バイアスのエネルギーを 150W から 50W に減少することで、メサ側面のリーク電流を抑制し逆方向電流を減少させることが出来た。

第4章のテーマはパワーデバイスの高耐圧化の研究である。自立 GaN 基板上 p·n ダイオードの結晶構造およびデバイス構造の検討を行い、以下の結論を得た。

- ① トリプルドリフト層構造を適用することでオン抵抗の増大を最小限に抑制しつつ高耐圧化を行い、耐圧 4.7kV を達成した。

- ② p-n ダイオードのメサ端付近での電界集中を緩和するため、ガードリング 構造 p-n ダイオードの検討を行った。メイン p-n ダイオード部分とガード リング部分の間に抵抗素子を挿入することで生じる両者の間の電圧降下 を利用して、ガードリング部分のメサ端付近の電界集中を緩和し、通常構 造 p-n ダイオードに比べ約 200V 高い耐圧 5kV が得られた。

- ③ p-n ダイオード降伏時の p-n ダイオードの破壊を防止し、可逆性を実現す

るためパンチスルー現象を利用した可逆性 p--n ダイオードの検討を行った。p-GaN 層のアクセプタ濃度が低い結晶を用い降伏電圧に近い逆方向電圧印加時に p-GaN 層を全空乏化することでパンチスルー現象を発生させ、p-n ダイオードの可逆性を実現した。15 回の繰り返し測定でも破壊が生じない約 4.8kV 耐圧の p-n ダイオードが得られた。

④ ガードリング構造 p-n ダイオードの改良版として p-GaN 層薄層化 p-n ダイオードの検討を行った。p 電極端-メサ端間の p-GaN 層を薄層化することで逆方向電圧印加時に p 電極端-メサ端間の p-GaN 層を全空乏化し、高抵抗化することで p 電極端-メサ端間に電圧降下を発生させメサ端付近の電界集中を緩和した。これにより通常構造 p-n ダイオードに比べ約 200Vの耐圧向上効果が得られた。これはガードリング構造 p-n ダイオードによる耐圧向上効果とほぼ同程度の効果であった。

第5章のテーマはパワーデバイスの大電流化の研究である。GaN 上 p-n ダイオードの特性に大きな影響のあるフォトンリサイクリング現象について検証し、同現象を利用した櫛形構造 p-n ダイオードの開発を行い以下の結論を得た。

① GaN 上 p-n ダイオードに見られる電流密度の電極面積依存性の原因について説明するため、4つの異なる電流密度領域を持つモデルにより実測値とのフィッティングを行った。その結果 p 形電極端から約  $10\,\mu$  m 幅で電流密度の大きな領域が存在することが確認できた。これは望月氏らにより提唱されたフォトンリサイクリング現象との整合性が取れた結果である。しかし電極径  $200\,\mu$  m 以上の p-n ダイオードではモデルに一致しない素子も見られ、フォトンリサイクリング現象のみでは説明が困難である事が

分かった。

- ② フォトンリサイクリング現象を利用して大電流化を図るため櫛形電極構造 p-n ダイオードの試作を行い評価した。その結果、同じ電極面積の円形電極構造 p-n ダイオードに比べオン抵抗が約 20%減少した。しかし、この結果も期待値に比べ低い電流となっており、やはりフォトンリサイクリング現象のみでは説明が困難である事が改めて確認された。

- ③ フォトンリサイクリング現象以外で電流密度の電極面積依存性が生じる原因を解析するため、p形電極の中心と電極端間での電圧降下を測定した。その結果、電極径  $800\,\mu$  m の素子で 1V 以上の電圧降下が生じている事が分かった。この事から電流密度の電極面積依存性が生じる原因は、少なくとも、

- (ア)フォトンリサイクリング現象

- (イ)p-n ダイオード面積増加に伴う電流増加による温度上昇が原因の抵抗 の増大

- (ウ)p 形電極電極端での電圧降下

- の3つの原因の複合であると考えられる。

#### 6.1 今後の課題

パワーデバイスの耐圧は現状 5kV が得られている。しかし、配電変電所における電圧は 6.6kV であり、その耐圧が得られれば街中の柱上変圧器等での需要も得られると考えられる。より高い耐圧に向けての検討が必要である。

一方順方向特性は電流 100A または電流密度 10kA/cm² (順方向電圧 4V) を目標として掲げており、耐圧 4kV を超える結晶仕様でそれを成し遂げるためには、フォトンリサイクリング現象を最大限活用した櫛形構造 p-n ダイオード等を多数配置したマルチセルダイオードの開発が必須であると思われる。加えて単体の櫛形構造 p-n ダイオードに関しても目論見通りの特性が得られているとは言えず、本研究で明らかになった問題点である電極の横方向抵抗の低減も含めマルチセルダイオード作製プロセスの検討が急務である。

また、例えば PCU のような回路では、p-n ダイオード等能動素子に加え、コイルやコンデンサ等の受動素子も搭載する必要がある。ミリ波レーダー用 MMIC 作製プロセスで培った集積化技術を応用し、PCU 回路等の開発も行っていく。

### 参考文献

- [1] "1947 Invention of the point-contact transistor," THE SILICON ENGINE.

- [2] "1948 Conception of the junction transistor," THE SILICON ENGINE.

- [3] Nick Holonyak Jr, "The Origins of Diffused-Silicon Technology at Bell Labs," The Electro-Chemical Society Interface, (1954-55).

- [4] D. M. Chapin, C. S. Fuller, G. L. Pearson, "A New Silicon p n Junction Photocell for Converting Solar Radiation into Electrical Power," Journal of Applied Physics 25, 676, (1954).

- [5] J. J. Ebers, J. L. Moll, "Large-Signal Behavior of Junction Transistors," Proc. I.R.E., 42, p. 1762, (1954).

- [6] J. L. Moll, M. Tanenbaum, J. M. Goldey, N. Holonyak, "P-N-P-N Transistor Switches," Proc. I.R.E, 44, 9, pp. 1174-1182, (1956).

- [7] 林哲史, "次世代パワー半導体," 日経 BP コンサルティング, (2012).

- [8] H. Welker, Z. f. Naturforschung, "Über neue halbleitende Verbindungen," 7a, (1952), S. 744-749 und 8a, (1953), S. 248-251.

- [9] 生駒俊明,生駒英明,"化合物半導体の基礎物性入門," 培風館 (1991).

- [10] T. Mimura, S. Hiyamizu, T. Fujii, K. Nanbu, "A new field-effect transistor with selectively doped GaAs/n-AlGaAs heterojunction," Japanese J. Appl. Phys. Vol. 19, L225, (1980).

- [11] P. M. Solimon, H. Morkoc, "Modulation-doped GaAs/AlGaAs heterojunction field effect transistors (MODFETs), ultra-high speed devices for supercomputers," IEEE Trans. Electron Devices, vol. ED-3, p. 1015, (1984).

- [12] C. S. Kang, P.E.Greene, "Preparation and Properties of High-purity Epitaxial GaAs Grown from Ga Solution," Appl. Phys. Letters, vol. 11 pp. 171-173, (1967).

- [13] L. Pfeiffer, K. W. West, H. L. Stormer, K. W. Baldwin, "Electron mobilities exceeding 107 cm<sup>2</sup>/V s in modulation - doped GaAs," Appl. Phys. Lett. Vol. 55, p. 1888, (1989).

- [14] K. Murata, K. Sano, H. Kitabayashi, S. Sugitani, H. Sugahara, T. Enoki, "100-Gb/s multiplexing and demultiplexing IC operations in InP HEMT technology," IEEE Journal of Solid-State Circuits, Vol. 39, Issue. 1, (2004).

- [15] R. Lai, X. B. Mei, W. R. Deal, W. Yoshida, Y. M. Kim, P. H. Liu, J. Lee, J. Uyeda, V. Radisic, M. Lange, T. Gaier, L. Samoska, A. Fung, "Sub 50 nm InP HEMT Device with F<sub>max</sub> Greater than 1 THz," 2007 IEEE International Electron Devices Meeting, p. 609, (2007).