# 法政大学学術機関リポジトリ

### HOSEI UNIVERSITY REPOSITORY

PDF issue: 2025-01-03

### 無線通信システム用A/D変換器の高性能化に 関する研究

伊藤, 朋彦 / ITO, Tomohiko

(出版者 / Publisher)

法政大学大学院理工学・工学研究科

(雑誌名 / Journal or Publication Title)

法政大学大学院紀要.理工学·工学研究科編/法政大学大学院紀要.理工学·工学研究科編

(巻 / Volume)

55

(発行年 / Year)

2014-03-24

(学位授与年月日 / Date of Granted)

2013-09-15

(学位名 / Degree Name)

博士(工学)

(学位授与機関 / Degree Grantor)

法政大学(Hosei University)

### 無線通信システム用 A/D 変換器の 高性能化に関する研究

## A RESEARCH ON HIGH-PERFORMANCE ANALOG-TO-DIGITAL CONVERTERS IN WIRELESS COMMUNICATION SYSTEMS

伊藤朋彦

Tomohiko ITO

指導教員 安田彰

法政大学大学院理工学研究科電気電子工学専攻博士後期課程

To realize next-generation high-throughput wireless communication systems, it is essential to develop analog-to-digital converters (ADC) with high conversion speed, high resolution, low power, and low operational supply voltage. In this work, the design methodologies and the new circuit architectures for these high-performance ADCs are researched.

First, the methods to optimize these performances for ADCs were confirmed. In a pipeline ADC which is promising to realize the high-throughput systems, the size of sampling capacitors and the power dissipation of the operational amplifiers tends to determine the performances for the ADCs. The proposed circuit to measure small relative mismatches between the sampling capacitors facilitates the size optimization of them. Moreover, the proposed nonlinear model allows to estimate the number of conversion stages to minimize the total dissipated power of the amplifiers used in a pipeline ADC more precisely than the conventional linear model. Besides, the theoretical and experimental analyses for two conventional low power techniques for a pipeline ADC manifest the effective method to reduce the power of the operational amplifiers in it.

Next, the higher-performance ADCs for various types of wireless systems were developed based on the confirmed methods. For next-generation cellular system such as LTE-advanced, a low-power, 12-bit and 100-MS/s pipeline ADC is developed. the 2.5bit/stage configuration, the I/Q amplifier sharing techniques and the proposed pseudo-differential operational amplifiers with two-gain-stage gain-boosting amplifiers achieve the lowest power in the reported pipeline ADCs with equivalent speeds and resolutions. In addition, a 12-bit and 40-MS/s pipeline ADC was prototyped for non-cellular system such as WLAN/WiMAX. The improved pseudo-differential amplifiers can stabilize the output common-mode voltage, operating from low power-supply voltage of 0.9V. Furthermore, a flash ADC with the high conversion speed of 3GS/s are developed for millimeter-wave wireless communication system. The proposed calibration technique efficiently suppresses the degradation of the resolution due to the DC offset voltage generated in preamps and comparators from low supply voltage of 1V, keeping the required resolution even at Nyquist input frequency.

Key Words: ADC, A/D, Analog-to-Digital Converter, Pipeline, Flash, Wireless, Receiver

#### 1. はじめに

携帯電話や無線 LAN などで採用されている無線通信システムにおいては、情報を媒介する無線アナログ信号に対して各種の信号処理を施すことにより、無線通信機器間での情報のやりとりを実現している。

半導体微細加工技術の進展に伴い、デジタル回路の低コスト化が進んだ結果、かつてはアナログ信号のまま行っていた信号処理を、デジタル信号に置換してから行う

ようになってきた。デジタル信号処理を実施するためには、アナログデジタル変換器(A/D 変換器)を用い、受信したアナログ信号をデジタル信号に置換する必要がある。近年、無線通信機器によるインターネット利用シーンの拡大などに伴い、扱う情報量は増大しており、それを支える無線通信システムには、高速大容量化が強く求められている。高速大容量化の主な方法は、無線周波数帯域幅の拡大と周波数利用効率の向上である。これを実現

するためには、A/D 変換器の高速化および高分解能化が 必須である。また、モバイル端末においては、電池駆動 が前提である場合が多く、待受時間の長時間化のため、 A/D 変換器にも低消費電力化が求められる。さらに、近 年は、回路の集積度が飛躍的に向上し、送受信に必要な 高周波回路からデジタル信号処理部までの全てを1チッ プ化するシステムオンチップ(SoC)が一般的になってき ている。これに伴い、微細化による MOS トランジスタの ゲート耐圧低下に対応して、ICの電源電圧が下がってき ている。一般に、デジタル回路の消費電力は、電源電圧 の低下による低消費電力化が期待できる。しかしながら、 オペアンプやコンパレータなどのアナログ回路で構成さ れる A/D 変換器では、電源電圧低下につれ、回路内で扱 いうる信号電力が小さくなることで信号雑音比の低下に 伴う分解能劣化や消費電力増加などのデメリットが発生 しやすくなる。よって、低電源電圧下においても所望の 性能を得られる A/D 変換器の設計手法確立が、無線通信 用 SoC 実現に欠かせない。

本研究では、こうした背景から、無線通信システム用 A/D 変換器の高速高分解能化、低消費電力化、低電源電 圧動作実現による性能向上を課題とする。まず、A/D 変 換器の性能を最適化するための手法に関する研究を実施 する。次に、確立した最適化手法をベースに用いつつ、無線通信用 A/D 変換器の性能をさらに向上するための各 種技術提案を行う。

#### 2. A/D 変換器の性能最適化手法

#### (1) 相対容量ミスマッチ測定回路[1]

無線通信用途に多用されるパイプライン型 A/D 変換器は、通常 1~4bit のアナログデジタル変換を実施する変換ステージを、縦列接続した回路アーキテクチャをもつ。各変換ステージは、スイッチトキャパシタ回路構成であり、オペアンプを利用し、負荷となる容量に信号を充放電することにより、前段の変換ステージから後段へ信号を伝達する。

パイプライン型 A/D 変換器の性能は、使用する容量のサイズとオペアンプの消費電力に大きく依存する。本節では、容量サイズの最適化に関する研究を実施した。

容量サイズは、パイプライン型 A/D 変換器の分解能と消費電力に影響する。容量サイズが大きいほど、kT/C ノイズや容量の相対ミスマッチが小さくなり、分解能が向上するが、同時に、充放電に必要なオペアンプの電流が増え、消費電力が増加するトレードオフが存在する。よって、開発する無線通信システムから要求される分解能を確保できる最小サイズの容量を用いることが、パイプライン型 A/D 変換器の性能最適化につながる。

上記に挙げた分解能劣化要因のうち、kT/C ノイズの大きさについては、計算により求められるが、容量の相対ミスマッチについては、使用するプロセスに起因するため、実測による把握が不可欠である。

本節では、容量の相対ミスマッチを容易に測定可能な 相対ミスマッチ測定回路を提案する。

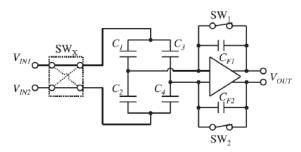

図1 提案する相対容量ミスマッチ測定回路

図1は、提案する相対容量ミスマッチ測定回路の回路図である。被測定対象の容量  $C_1 \sim C_4$  の相対ミスマッチがあると、その大きさに比例した差動出力電圧  $V_{out}$  が出力される。これをオシロスコープで測定することにより、容易に相対ミスマッチが測定可能となる。

実測される差動出力電圧  $V_{\text{out}}$  は、スイッチ  $S_{\text{w1}}$ 、 $S_{\text{w2}}$ を構成する MOS トランジスタから容量  $C_1 \sim C_4 \sim 0$  クロックフィードスルーのバラつきに起因したオフセット電圧  $V_{\text{off}}$  を誤差として含んでいる。そこで、提案する測定回路では、 $V_{\text{off}}$  のみを測定する動作モードを追加し、 $V_{\text{off}}$  を  $V_{\text{out}}$  から減算することで補正している。

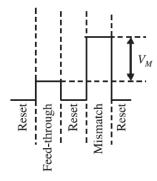

図 2 提案回路の出力差動電圧

図 2 は、提案回路の出力差動電圧を示している。 Feed-through モードでは、スイッチ  $S_{w1}$ 、 $S_{w2}$ だけが OFF し、オフセット電圧  $V_{\rm off}$ が測定される。 Mismatch モードでは、スイッチ  $S_{w1}$ 、 $S_{w2}$ だけが OFF すると同時に、スイッチ  $S_{wx}$ が切り替わり、電圧  $V_{\rm out}$ が測定される。  $V_{\rm out}$ と  $V_{\rm off}$ の差分である  $V_{\rm M}$ を容量相対ミスマッチに起因した電圧として扱うことで補正をかけることができる。

提案する相対ミスマッチ測定回路を 130 nmCMOS プロセスを用いて試作した。実測の結果、 $3\sigma=0.5 \text{LSB}$  となる容量値は 0.6 pF であった。0.6 pF は、10 bit の分解能を得るための kT/C ノイズから計算される必要な容量値より十分小さく、容量の相対ミスマッチは、分解能劣化の要因としては大きな問題ではないことが分かった。

(2) オペアンプシェアリングおよび疑似差動低消費電

力化回路技術の検討および 10bit 80MS/s パイプライン型 A/D 変換器への適用[2]

本節では、パイプライン型 A/D 変換器に使用するオペアンプ電力を削減する技術に関する理論検討と試作による検証を実施した。

パイプライン型 A/D 変換器では、電力の大半がオペアンプで消費される。そのため、オペアンプの電力効率を向上することが、低消費電力化のカギである。

パイプライン型 A/D 変換器のオペアンプ電力を削減する有力技術の1つは、報告例[3] で実施されている擬似差動構成オペアンプである。擬似差動オペアンプとは、2つのシングルエンド構成のソース接地型アンプを、従来利用されていた入力段に差動対をもつ全差動構成オペアンプの代わりに用いたものである。

もう一つのオペアンプ電力を削減できる有力技術は、報告例[4]のアンプシェアリング技術である。このアンプシェアリング技術では、1 つのオペアンプを、2 つの連続する変換ステージ間で共用化することで、利用するオペアンプ数を減らし、消費電力を削減する。

報告例[3]の擬似差動構成オペアンプと報告例[4]のアンプシェアリング技術との両立は困難である。アンプ共用化のためには、オフセットキャンセルの省略が必要だが、報告例[3]の擬似差動構成オペアンプを採用すると、それができないからである。

そこで本節では、まず、報告例[3]の擬似差動オペアンプ構成と報告例[4]のアンプシェアリング技術のどちらがより電力効率が高いかについて理論検討を実施した。検討の結果、オフセットキャンセルの省略によって、消費電力が50%削減できることが判明した。

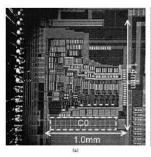

図 3 試作した 10bit 80MS/s パイプライン型 A/D 変換器のチップ写真 (a) アンプシェアリング無し (b) アンプシェアリング有り

報告例[3]の擬似差動オペアンプ構成の電力削減効果は最大50%である。一方、報告例[4]のアンプシェアリング技術では、オフセットキャンセルの省略とアンプ共用化に伴うオペアンプ数減少の2つが消費電力の削減に貢献する。オフセットキャンセルの省略と擬似差動オペアンプ構成採用による電力削減効果は同じであることから、報告例[4]のアンプシェアリング技術の採用が、報告例

[3]の擬似差動オペアンプ構成採用に比べ、低消費電力化に対して有利であることがわかった。

次に、アンプシェアリング技術の電力削減効果を検証するため、130nmCMOS プロセスを用いた試作を行った。 図 3 は、試作した 2 種類の 10bit 80MS/s パイプライン型 A/D 変換器のチップ写真である。実測の結果、消費電力は(a)が 70mW、(b)が 55mW であった。このことから、連続する変換ステージ間でのアンプシェアリング技術における電力削減効果は約 22%であり、報告例[4]で記載された 50%より低いことが判明した。

(3) スルーレートを考慮したパイプライン型 A/D 変換器の変換ステージ構成法の検討[5]

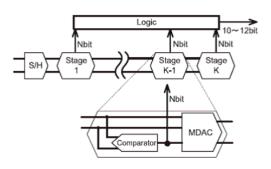

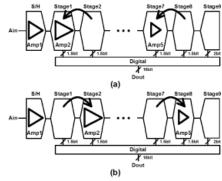

図4 パイプライン型 A/D 変換器のブロック図

本節では、パイプライン型 A/D 変換器で使用するオペアンプの電力を最小にできる変換ステージ構成を見出すための新たな手法について研究を実施した。

図 4 は、パイプライン型 A/D 変換器の回路ブロック図を示す。パイプライン型においては、1 つの変換ステージ(Stage) あたりでデジタル信号に変換されるビット数 N(bit/stage) の違いにより、オペアンプの電力が異なってくる事が知られている。

文献[6] においては、線形モデルに基づくオペアンプの電力見積もりがなされている。しかしながら、この報告では、オペアンプのスルーレートを考慮されていない。

そこで、本節では、オペアンプのスルーレートをも考慮した非線形モデルを用い、1.5bit/stage、2.5bit/stage、3.5bit/stage の3つの変換ステージ構成に関して、オペアンプの消費電力を見積もった。

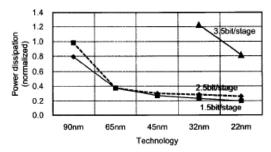

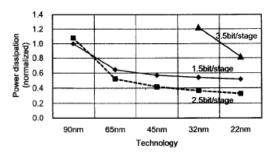

図 5 と図 6 は、200MS/s、10bit のパイプライン型 A/D 変換器について、オペアンプの合計消費電力を見積もった結果である。

図5は、従来手法の線形モデルで算出された結果を示す。線形モデルにおいては、プロセスによらず1.5bit/stage が有利である。一方、図6は、提案手法の非線形モデルで算出された結果である。90nmCMOSプロセスより微細化が進んだ場合、2.5bit/stage が最適であることがわかる。

図5 プロセスと消費電力の関係(線形モデル)

図6 プロセスと消費電力の関係(非線形モデル)

図5と図6の結果の違いは、以下のように説明できる。 プロセスの世代が進むと、トランジスタの単位電流当た りの電圧電流変換比が大きくなり、オペアンプが高速化 する。一方で、トランジスタのゲート耐圧低下に起因し て電源電圧が低下する。これに伴い、オペアンプの出力 信号範囲が狭まり、回路内で扱いうる信号電力が小さく なる。このとき、一定の信号雑音比を確保するためには、 オペアンプの負荷となる容量を増加し、kT/C ノイズを低 減する必要が生ずる。スルーレートを維持するためには、 負荷容量の増加に合わせて、オペアンプの電流を増加さ せなければならず消費電力が増加する。つまり、プロセ スの世代が進むほど、オペアンプのスルーレートが消費 電力に与える影響が大きくなる。パイプライン型では、 変換ステージ数が減少するにつれ、A/D 全体の合計負荷 容量が小さくなる傾向にある。よって、スルーレートが 考慮されていない従来手法を用いた図5の結果に比べ、 スルーレートが考慮された提案手法による図6の結果で は、プロセスの世代が進むと 2.5bit/stage の方が、 1.5bit/stage より有利になる。

図 6 の解析結果に基づき、90 nmCMOS プロセスで、200 MS/s、10 bit のパイプライン型 A/D 変換器をオペアンプの電力が最小になる 1.5 bit/stage 構成を採用し、試作した。試作した A/D 変換器の性能 (FoM) は、他の報告例に比べ良好であり、提案手法の有用性が確認できた。

### 3. 無線通信用 A/D 変換器の性能を向上するための各種技術提案

(1) 4G システム用消費電力 55mW, 電源電圧 1.2V, 分解能 12bit, 動作速度 100MS/s パイプライン型 A/D 変換器[7]

無線通信システム用途のパイプライン型 A/D 変換器では、待ち受け時間の長時間化などのため、低消費電力化が必須である。本節では、LTE-Advanced などの 4G システム用に好適な 100MS/s、12bit のパイプライン型 A/D 変換器の電力効率を向上するための技術提案を行う。

パイプライン型 A/D 変換器の電力効率向上のためには、 電力の大半を消費するオペアンプの低消費電力化が欠か せない。そこで、主に、3 つの技術を組み合わせること でオペアンプ電力の大幅な削減を実施する。

- 非線形モデルによる bit/stage 最適化 オペアンプ電力が最小になる変換ステージ構成を、2 章(3) で提案した非線形モデルを用いて検討し、

2.5bit/stage 構成を採用した。次に電力効率が高い

1.5bit/stage 構成に比べ、約15%削減。

- ② I/Q アンプシェアリング技術 2 つのパイプライン型 A/D 変換器の同じ変換ステージ間で、1 つのオペアンプを共用化する技術の実施により、A/D 全体のオペアンプの合計電力を 50%削減。

- ③ 低消費電力疑似差動構成オペアンプ

2.5bit/stage において、オペアンプの合計電力の約90%を消費する S/H 回路と初段変換ステージの MDAC で使用するオペアンプを、全差動構成から疑似差動構成に変更し、約45%削減。

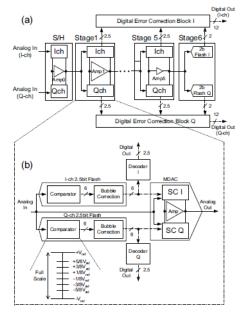

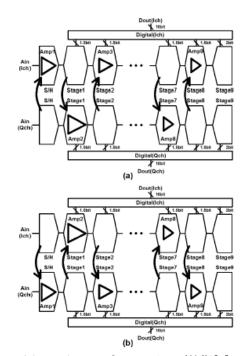

図 7(a)は、本研究で開発した 2.5bit/stage パイプライン型 A/D 変換器のブロック図を、図 7(b)は、その変換ステージ構成をそれぞれ示す。 2.5bit/stage では、S/H 回路と 6 つの変換ステージで構成される。

図8は、2章(2)で前述した従来例[4]のアンプシェアリング技術を示している。図8(a)では、オペアンプは、奇数の変換ステージで使用されている。一方、図8(b)では、各オペアンプは偶数の変換ステージで利用されている。従来例[4]のアンプシェリング技術では、この2つの動作を半クロック毎に繰り返すことで、隣り合う2つの変換ステージ間で1つのアンプを共用化する。これにより、必要なオペアンプ数を変換ステージ数の約半分にすることで、オペアンプの消費電力を低減できる。

しかしながら、パイプライン型 A/D 変換器では、前段のオペアンプほど分解能の要求が厳しく、必要な消費電力が大きい。ゆえに、図 8(a)の状態で所望分解能が得られるようにオペアンプの電流を設計せざるを得ず、結果として、図 8(b)のように、後段へオペアンプを移動させたとき、オペアンプがオーバースペックで使用されることになる。

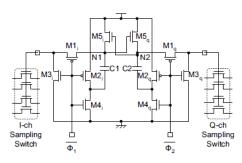

図 7(a) I/Q アンプシェアリング技術を用いた 2.5bit/stage パイプライン型 A/D 変換器 (b) 変換ステージ構成

このオーバースペックを解消するため、I/Q アンプシェアリング技術[8]を適用した。

近年の無線通信システムにおいては、直交復調を行うのが一般的である。直交復調を実施するためには、受信器には性能が等しい 2 つの A/D 変換器(Ich ADC と Qch ADC)が必要である。この Ich と Qch の間でオペアンプを共用化することで、1 つの A/D 変換器当たりのオペアンプ電力を半減できる。

図9は、I/Qアンプシェアリング技術を示している。図9(a)では、オペアンプは、上側のA/D変換器の偶数ステージと、下側のA/D変換器の奇数ステージで使用されている。一方、図9(b)では、オペアンプは、上側のA/D変換器の奇数ステージと、下側のA/D変換器の奇数ステージへ移動して使用されている。この2つの動作を半クロック毎に繰り返す。

I/Q アンプシェアリング技術では、全てのオペアンプが同じ変換ステージ間で使用されるため、全てのオペアンプの電力を最適に設計することが可能となる。そのため、オペアンプ数が半分になるのに比例し、その消費電力も50%削減できる。

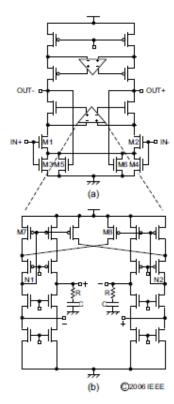

図 10 は、提案する疑似差動構成オペアンプの回路図を示す。図 10(a)のメインアンプに見られるように、疑似差動構成オペアンプでは、全てのトランジスタが縦積みになっており、入力段と出力段に同じ電流がながれる。一方、従来のパイプライン型で多用されていたフォールディッド構成のオペアンプでは、入力段の電流を折り返して出力段に流す回路構成であり、入力段と出力段のそれぞれに電流が必要である。ゆえに、全差動構成に代えて、疑似差動構成をパイプライン型 A/D 変換器に採用す

ることで、オペアンプ電力を半減できる。

図8 従来のアンプシェアリング技術[4]

図9 I/Qアンプシェアリング技術[8]

ただし、疑似差動構成オペアンプは、全差動構成に比べ、回路構成が簡素な分、オペアンプの出力同相電圧が所望のバイアス電圧から変動してしまう。パイプライン型では、この変動が後段の変換ステージへ伝達するたびに累積し、分解能の劣化を引き起こす問題がある。

この問題への対策として、疑似差動オペアンプは、S/H回路と初段の変換ステージの2つのみとし、2段目より後段の変換ステージでは、全て従来の全差動オペアンプのままとした。2.5bit/stageでは、オペアンプの全電力の90%はS/H回路と初段の変換ステージの2つで消費されるため、この変更により、消費電力が45%削減できる。同時に、2段目の変換ステージ以降では、出力同相電圧の変動の累積がなくなり、所望のバイアス電圧に安定化できるようになるため、分解能が確保できる。

疑似差動オペアンプの出力同相電圧が変動するのを抑制するため、図 10(a)の M5、M6 を追加した。 M5、M6 は、簡素な同相電圧安定化回路(CMFB)として機能し、出力同相電圧の変動を抑制する。 M5、M6 は、M1、M2 に縦積みさ

れているため、M5、M6の追加により、電流の増加はない。また、M1~M4の接続は、M5、M6が線形領域で動作することを保証している。線形領域トランジスタのドレイン-ソース間電圧は数十mVと小さくてよいので、M5、M6の縦積みによって、オペアンプの出力範囲が狭まることを回避できる。

また、図 10(b)のような、利得段が 2 段のゲインブーストアンプを提案することでオペアンプの電力を低減した。M7 と M8 のゲート電圧はそれぞれ逆相に動作するため、トランジスタ M7 と M8 に流れる電流が相殺し、ノード N1 でも大きな利得が得られるようになる。結果として、必要な DC ゲインを補助のゲインブーストアンプを追加することなく得られるようになり、その分、消費電力を低減できる。

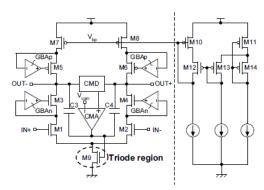

図 10 S/H 回路と初段 MDAC に用いられた疑似差動オペアンプ (a)メインアンプ (b) ゲインブーストアンプ

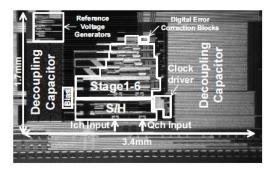

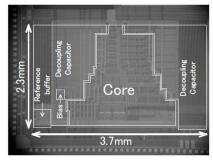

図 11 試作した 12bit、100MS/s パイプライン型 A/D 変換器のチップ写真

図 11 に、90nmCMOS プロセスで試作したパイプライン型 A/D 変換器のチップ写真を示す。

試作回路の消費電力は、1ch 当たり 55mW であった。この消費電力は、同等の動作速度と分解能を持つ他の試作例に比べ、約半分である。また、ナイキスト周波数まで9 有効ビット(ENOB)以上を確保でき、4G システム用途として、必要な分解能を得ることができた。

(2) 0.9V で動作する無線通信用 12bit、40MS/s パイプライン型 A/D 変換器[9]

本節では、WLAN/WiMAX 向け 12bit、40MS/s のパイプライン型 A/D 変換器を開発した。I/Q シェアリング技術や疑似差動構成オペアンプなど、前章までの成果を生かしつつ、0.9V の低電源電圧で実現する回路構成について提案することで、更なる性能向上の実現を図った。

パイプライン型 A/D 変換器の電源電圧低下による第一の課題は、サンプリングスイッチである。サンプリングスイッチとして一般に用いられる CMOS スイッチは、電源電圧低下に伴い、On 抵抗の線形性が確保できる範囲が狭くなる[6]。

解決のため、図 12 の I/Q で共用化されたクロックブースト回路を提案し、採用した。クロックブースト回路は、スイッチを駆動するクロック信号を 0.9V 以上に昇圧することで CMOS スイッチに比べ On 抵抗歪みを軽減できる。クロック昇圧回路の欠点としては、スイッチの On 抵抗を十分低くするために、スイッチトランジスタのゲート端子の寄生容量よりも十分大きなプリチャージ用容量を用いる必要があり、面積が増大する事である[10]。そこで、図 12 の回路では、1 つのクロック昇圧回路を、Ich とQch で共用化することで、小面積化を図った。

電源電圧低下による第二の課題は、オペアンプ出力段の信号振幅範囲が狭くなることである。2章の(3)で前述したように、信号振幅範囲の低下した条件下でS/N比を確保しようとすると、オペアンプの消費電力が増加する。よって、低電源電圧動作と低消費電力化の両立には、電力効率の高いオペアンプの採用が欠かせない。

3章の(1)で記述したように、疑似差動オペアンプを使用すると、電力効率は向上するが、出力同相電圧の変動に起因した分解能劣化が生ずる欠点がある。この欠点は、低電源電圧になるほど、オペアンプ出力電圧範囲に余裕がなくなるため、より深刻になる。

そこで本節では、2 段の利得段を持つ同相電圧安定化回路(CMFB)を追加することで、出力同相電圧が安定化できる疑似差動オペアンプを提案した。

図 13 は、提案する疑似差動オペアンプを示す。図 10 との違いは、M9 の前段にアンプ CMA が追加されており、CMFB としての利得段が 2 段になっていることである。図 10 のオペアンプでは、M5、M6 が線形領域で動作するため、CMFB のループ利得が十分得られず、出力同相電圧を所望

の電圧に安定化できない欠点があった。一方、図 13 では、CMA の追加により、必要な CMFB のループ利得が確保できるようになり、出力同相電圧が所望のバイアス電圧に安定化できるようになった。結果として、全ての変換ステージのオペアンプを疑似差動構成に置換できるようになる。これは、一部を全差動オペアンプのまま使用した 3 章(1)のパイプライン型 A/D 変換器よりも電力効率の向上につながる。

$\divideontimes\overline{\Phi_{1}}$   $(\overline{\Phi_{2}})$ : inversed clock signal of  $\Phi_{1}(\Phi_{2})$

図 12 I/Q で共用化されたクロックブースト回路

図13 提案する疑似差動オペアンプ

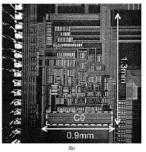

図 14 試作した 12bit、40MS/s パイプライン型 A/D 変換器のチップ写真

図 14 に、試作回路のチップ写真を示す。測定の結果、40MS/s 動作時に9.3ENOB以上の有効ビット数を得られた。消費電力は、A/D 変換器1 つあたり17.3mW であった。以上の結果は、0.9V の低電源電圧ながら、WLAN/WiMAX を実現する上で要求される性能を満足している

#### (3) 1V で動作する 3GS/s 5bit 低消費電力フラッシュ

#### 型 A/D 変換器[11]

本節では、ミリ波帯通信用に開発した36S/s、5bitのフラッシュ型 A/D 変換器を 1V の電源電圧で動作させる技術について提案した。現在、数 GHz という広いミリ波帯の無線周波数を用いた大容量無線通信システムの実現が期待されている。広帯域の無線信号を A/D 変換するためには、GS/s オーダーの高速動作実現が必要である。

高速動作実現には、微細化プロセス採用が有利であるが、低電源電圧化に伴う信号電力の低下により、トランジスタのミスマッチが信号の線形性に与える影響がより大きくなり、分解能が劣化しやすくなる欠点がある。

本研究のフラッシュ型 A/D 変換器では、このミスマッチにより発生したプリアンプやコンパレータの DC オフセット電圧を、フォアグラウンド補正技術により十分小さくすることで、分解能を向上させた。補正の順序を工夫した補正アルゴリズムを提案することで、簡単な回路構成ながら、低電源電圧下においても、分解能を維持することを可能にした。

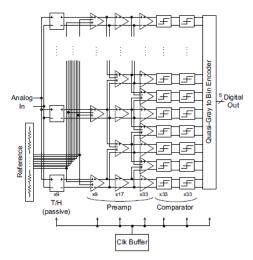

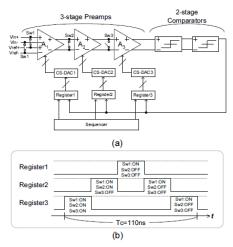

図 15 に、本研究のフラッシュ型 A/D 変換器の回路アーキテクチャを示す。主に、入力アナログ信号をサンプルする T/H(Track-and-Hold)回路、サンプルされた信号を増幅するプリアンプ、アナログ信号を量子化するコンパレータで構成される。プリアンプは、3 段縦列接続されており、1 段あたり 2 倍のインターポーレーションされている。

図 16(a) に、提案の DC オフセット補正回路のブロック 図を、図 16(b)に、そのタイミングチャートを示す。プ リアンプに電流出力型 D/A 変換器 (CS-DAC) を追加し、プ リアンプやコンパレータに発生する DC オフセット電圧 をキャンセルする方向に、CS-DAC の電流をプリアンプの 負荷抵抗に流すことで発生する電圧を発生して補正を行 う。従来は、前段のプリアンプから後段へ順番に CS-DAC を動作させることで補正をかけていた。しかし、この方 法では、インターポーレーションにより入力電圧が補完 されるプリアンプの DC オフセット誤差が増える可能性 を考慮し、CS-DAC の電流を増加させなければならず、低 電源電圧動作に不向きであるという問題があった。そこ で、提案回路では、図 16(b)にみられるように、まず、 後段のプリアンプから前段のプリアンプにかけて、1段 ずつ補正をかける。次に、2段目、3段目の順に前から後 ろへ補正をかける。この方法では、最初に後段から前段 へ補正をかけるため、インターポーレーションノードの DC オフセット誤差が増加しない。また、従来同様、前段 から後段への補正もかけるため、入力換算残留 DC オフセ ット電圧が小さくでき、分解能が向上できる。

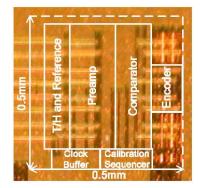

図 17 は、65nmCMOS プロセスで試作した 3GS/s、5bit フラッシュ型 A/D 変換器のチップ写真を示す。試作回路 は、電源電圧 1V ながら、ナイキスト周波数まで 4.2ENOB 以上の有効ビット数を確保でき、良好な分解能が得られ

た。また、消費電力は 32.6mW であり、世界トップレベル の性能を実現できた。

図 15 フラッシュ型 A/D 変換器ブロック図

図 16 提案する補正アルゴリズム

図 17 試作した 3GS/s、5bit フラッシュ型 A/D 変換器のチップ写真

#### 4. まとめ

無線通信システムの高速大容量化実現のために、A/D 変換器の高速化、高分解能化、低消費電力化、低電源電 圧動作実現による高性能化に関する研究を実施した。

まず、A/D変換器の性能を最適化する手法を研究した。

容量の相対ミスマッチ把握のための測定回路提案や、オペアンプの電力を削減できる技術の理論検討、非線形モデルを用いたオペアンプ電力が最小になる bit/stage の検討を通じて、最適化のための手法を確立した。

次に、確立した手法を用いつつ、さらなる高性能化のための研究を行った。I/Q アンプシェアリング技術の採用や、低消費電力疑似差動構成オペアンプや DC オフセット補正の新規アルゴリズムなどの提案により、各種性能の向上を図った。

研究の結果、パイプライン型やフラッシュ型の A/D 変換器において、世界トップレベルの電力効率を達成した。また、低電源電圧下においても、各種無線通信システムから要求される高速高分解能、消費電力を満足するような A/D 変換器を実現できた。

#### 参考文献

- T. Ito, et. al., "Capacitance Mismatch Evaluation for Low-power Pipeline ADC Design", IEICE ELEX, No.3, pp.63-68,May, 2004.

- 2) T. Ito, et. al., "Low-Power Design of 10-bit 80-MSPS Pipeline ADCs", IEICE Trans. Fund., vol.E89-A, No.7, pp.2003-2008, Jul. 2006.

- 3) D. Miyazaki et. al, "A 10-b 30-MS/s Low-Power Pipelined CMOS A/D converter Using a Pseudodifferential Architecture," IEEE JSSC, pp. 369–373, Feb. 2003.

- 4) B. M. Min et. al, "69-mW 10-bit 80-MSample/s pipelined CMOS ADC," IEEE JSSC, pp. 2031–2039, Dec. 2003.

- 5) T. Ito, et. al., "A 10-bit, 200-MSPS, 105-mW pipeline A-to-D converter", IEICE ELEX, vol.2, No.15, pp.429-433, Aug, 2005.

- 6) A. M. Abo et. al, "A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter," IEEE JSSC, pp. 599–606, May 1999.

- 7) T. Ito, et. al., "55-mW 1.2-V 12-bit 100-MSPS Pipeline ADCs for Wireless Receivers", IEICE Trans. Elec., vol.E91-C, No.6, pp.887-893, Jun. 2008.

- D. Kurose et. al, "55-mW 200-MSPS 10-bit Pipeline ADCs for Wireless Receivers," IEEE JSSC, pp.1589–1595, Jul. 2006.

- 9) T. Ito, et. al., "A 0.9-V 12-bit 40-MSPS Pipeline ADC for Wireless Receivers", IEICE Trans. Fund., vol.E93-A, No.2, pp.395-401, Feb. 2010.

- 10) T. B. Cho et. al, "A 10b, 20Msample/s, 35mW Pipeline A/D Converter," IEEE JSSC, pp. 166–172, Mar. 1995.

- 11) T. Ito et. al., "A 3-GS/s 5-bit 36-mW Flash ADC in 65-nm CMOS", in Proc. IEEE A-SSCC, Nov. 2010.