# 法政大学学術機関リポジトリ

### HOSEI UNIVERSITY REPOSITORY

PDF issue: 2025-07-01

# 高次ジッタシェーピング特性を有するサンプルホールドDACの研究

北原, 義大 / KITAHARA, Yoshihiro

(出版者 / Publisher) 法政大学大学院理工学・工学研究科

(雑誌名 / Journal or Publication Title)

法政大学大学院紀要.理工学·工学研究科編/法政大学大学院紀要.理工学·工学研究科編

(巻 / Volume) 55 (開始ページ / Start Page) 1 (終了ページ / End Page) 4 (発行年 / Year) 2014-03-24

(URL)

https://doi.org/10.15002/00010375

## 高次ジッタシェーピング特性を有する サンプルホールド DAC の研究

## STUDY OF SAMPLE AND HOLD DIGITAL-ANALOG CONVERTER WITH HIGH ORDER JITTER NOISE SHAPING

#### 北原義大 Yoshihiro KITAHARA 指導教員 安田彰

法政大学大学院工学研究科建設工学専攻修士課程

In this paper, present sample hold DAC with high order jitter noise shaping using 2<sup>nd</sup> order architecture or feed-forward 2nd order architecture. Performance improvements of sample hold DAC can be expected by using higher order jitter noise shaping. The effectiveness of presented architecture is confirmed by MATLAB simulation results and SPICE simulation results.

Key Words: sample hold, DAC, jitter noise shaping, high order

#### 1. はじめに

近年,技術発展により,デジタル回路はより高速・高精度化してきている. それに伴って,デジタルとアナログを結ぶ変換器,すなわち ADC(アナログデジタル変換器),DAC(デジタルアナログ変換器)もより高速化,高精度化することが求められるようになった.

DACでは、出力信号はクロック信号で制御されて、出力される。しかし、クロック信号はクロックジッタにより、周期をわずかに変動させられてしまう。DACの出力信号はクロックジッタによりパルス幅が増減させられる。デジタル信号であればパルス振幅が保てれば問題ないが、アナログ信号を出力する DAC ではパルス幅の変動が電力の変動を引き起こし、性能が劣化してしまう。

Δ Σ 型変換器は、オーバーサンプリング技術と比較器で発生する量子化器雑音に伝達特性を与えて信号帯域外に雑音を再配置するノイズシェーピングによって、低変換速度ではあるが高精度を実現できる[1]. この構造を利用し、比較器に代えサンプルホールド回路を用いることで、比較器で発生する雑音、すなわちジッタ雑音に伝達特性を与えて、信号帯域外に再配置させるジッタシェーピング特性を得、DAC の精度を改善することができる.

サンプルホールド DAC を高次化することで、より急峻なハイパス特性のジッタシェーピングをジッタ雑音に与えることで、精度の向上が期待できる。本稿では、ジッタシェーピングの 2 次化を実現する 2 種類の方法を提案し、1 次ジッタシェーピングよりも精度が向上したことを報告する.

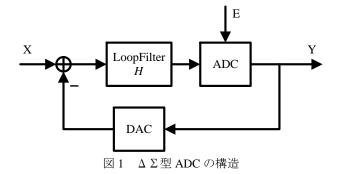

#### 2. ΔΣ型変換機

図 1 に  $\Delta$   $\Sigma$  型変換器の構成を示す.  $\Delta$   $\Sigma$  型変換器は、オーバーサンプリング技術とノイズシェーピングによって、変換速度を犠牲にして高い精度を実現する.

オーバーサンプリング技術とは、ナイキスト定理により定められたナイキスト周波数よりもさらに高い周波数でサンプリングを行う技術のことである. 量子化誤差はサンプリング周波数の 0.5 倍の周波数まで一様に広げられ、雑音強度が減少する.

ノイズシェーピングとは、 $\Delta \Sigma$ 型変換器の内部 ADC で生じる雑音に特定の周波数特性を与え、信号帯域外に雑音を再配置させることである. (1)式に、伝達特性を示す. なお、X は入力信号、Y は出力信号、E は量子化雑音、E はループフィルタの伝達関数である.

$$Y = \frac{H}{1+H}X + \frac{1}{1+H}E\tag{1}$$

例えば、図1の構成が離散時間の無遅延積分器を用いた1次 $\Delta$   $\Sigma$ 型変換器の場合、ループフィルタ L は(2)式のように表され、(1)式から(3)式が求められる.

$$H = \frac{1}{1 + z^{-1}} \tag{2}$$

$$Y = X + (1 - z^{-1})E. (3)$$

(3)式では入力信号 X の変化はないが、量子化誤差には ハイパス特性を持つ伝達関数が与えられている. 信号帯 域内での雑音強度は減少し、信号帯域外をフィルタリン グすることで高精度を実現している.

#### 3. サンプルホールド DAC

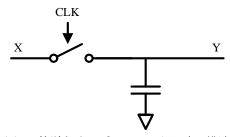

#### (1) サンプルホールド

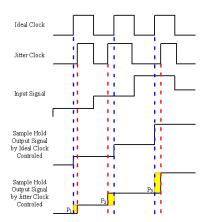

図2にサンプルホールド回路の構造を示す.サンプルホールド回路は、クロック信号を受けて、入力信号をサンプリングし、必要な時間までサンプリングした信号をホールドする回路である.図3に線形増加している入力信号を理想のクロック信号と、サンプルホールド回路でサンプリングした出力波形を青色で示す.

サンプルホールド回路は,ADC では積分型や逐次比較型などの A/D 変換に時間がかかる場合に,アナログ入力信号の保持に使用される.DAC でもデ・グリッチ回路に使用されている[2].

図2 簡単なサンプルホールド回路の構造

図3 クロックジッタによるクロック信号とサンプルホールド回路の出力波形の変化

#### (2) クロックジッタ

クロックジッタとは、回路の動作を制御するクロック 信号が、位相変調や振幅変調を引き起こし、回路の動作 点が想定しているクロックタイミングから変動してしま うことである.

図 3 に理想クロック信号とクロックジッタ含む信号である入力信号をサンプルホールド介して出力した時の波形を示す.

DAC の出力は、クロック信号で制御されたパルス波形である. したがって、クロックジッタが存在すると図 3 のように出力のパルス幅が変動してしまい、SNR の劣化を引き起こしてしまう.

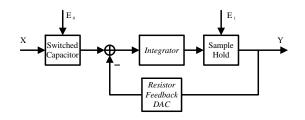

#### (3) ジッタシェーピング

ジッタシェーピングはノイズシェーピングと同様の手法を用いることで、ジッタ雑音に伝達関数を与え、信号帯域外に再配置する手法である.

その構造を図 4 に示す. また,入力信号を X,出力信号を Y,システムよりも前に入力信号に挿入されたジッタ 雑音を $E_0$ ,サンプルホールドによって生じるジッタ雑音を $E_1$ とした時の伝達特性を(4)式に記し,X の係数である信号伝達関数(STF)と $E_1$ の係数である雑音伝達関数(NTF)の周波数特性を図 5 に示す.

$$Y = \frac{z^{-1}}{s + z^{-1}} X + \frac{z^{-1}}{s + z^{-1}} E_0 + \frac{sz^{-1}}{s + z^{-1}} E_1$$

(4)

ジッタシェーピング特性を有する DAC の構成は  $\Delta \Sigma$ 型の構造に類似しており、比較器にサンプルホールド回路に変更した構造である。入力のみスイッチトキャパシタ回路を用いた離散時間型積分器を用いるが、その他の経路では抵抗で構成される DAC を用いた連続時間型積分器を使用する。

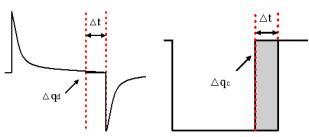

入力にスイッチトキャパシタを用いるのは入力自体に存在するジッタ雑音の影響を抑えるためである。(4)式からわかるように、システムの前に挿入される雑音に対してはジッタシェーピングの効果を与えられない。そのため、入力に挿入する雑音を抑える必要がある。図6に離散時間型積分器と連続時間積分器を用いた時、クロックジッタによって生じる電荷の損失を示す[3]。スイッチトキャパシタの場合、時間内に蓄えた電荷を放出すればよい。

図4 1次ジッタシェーピングサンプルホールド DAC

図 5 1 次ジッタシェーピングサンプルホールド DAC の STF(青)と NTF(赤)

図6 クロックジッタに対する電荷量の誤差

そのため、クロックジッタにより多少放電時間が変動した場合でも、放出する電荷量の変動は非常に小さくなる.

一方で入力以外の経路に連続時間型積分器を用いるのは、出力信号のジッタ雑音をフィードバックするためである. 抵抗で構成された連続時間積分器では、電荷が流れ続け、積分し続ける. すなわち、クロックジッタによるパルス幅の変動も積分される. したがって、サンプルホールドで挿入されるジッタ雑音 $E_1$  に(4)式の伝達特性を与えることができる.

なお,ジッタシェーピングと同様に後段で帯域外をフィルタリングする必要があるが,クロック制御が必要なデジタルフィルタでは新たにジッタ雑音が生じるため,後段フィルタはアナログ回路で構成しなければならない.

#### 4. 提案構成

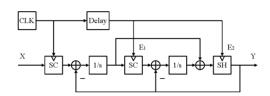

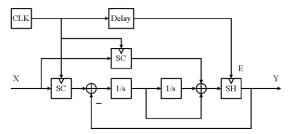

図7に2次ジッタシェーピングサンプルホールドDAC を,図8にフィードフォワード型2次ジッタシェーピングサンプルホールドDAC のブロックモデルをそれぞれ示す.

通常の2次ジッタシェーピング DAC では、二段目の積

図7 2次ジッタシェーピングサンプルホールド DAC

図 8 フィードフォワード型 2 次ジッタシェーピング サンプルホールド DAC

分器には、急峻な入力信号の変動による飽和を防ぐためにスイッチトキャパシタを用い、フィードフォワードパスを追加した. 内部の離散積分器においてもクロックジッタは生じるが、ジッタ雑音は 1 段目と同様ほとんど現れない. また、1 次のジッタシェーピング特性が与えられるため、さらにその影響は小さくなる.

フィードフォワード型2次ジッタシェーピングDACでは、初段入力以降はすべて連続時間型で構成されるため、システム内に余計な雑音が存在しない. DACで発生するジッタ雑音に純粋な2次ジッタシェーピング特性を与えることができる.

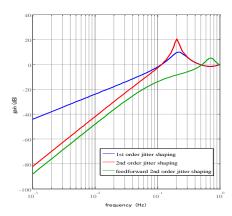

また、2次ジッタシェーピング DAC とフィードフォワード型ジッタシェーピング DAC の伝達関数を、入力信号をX、出力信号をY、サンプルホールドで発生するジッタ雑音をEとしてそれぞれ(5)式、(6)式に示す.

$$Y = \frac{(s^2 + 1.5s + 1)X + z^{-1}s^2E}{s^2 - 1.5sz^{-1} - z^{-1}}$$

(5)

$$Y = \frac{(3sz^{-1} + z^{-1})X + 4s^2z^{-1}E}{4s^2 + 3sz^{-1} + z^{-1} + 1}$$

(6)

(4)式, (5)式, (6)式よりそれぞれの NTF を図 8 にまとめて示す.図より, 1 次の構成の NTF が 20dB/dec であるのに対し、提案した構成の NTF は 40dB/dec に改善され、ジッタシェーピング特性が 2 次に高次化されていることがわかる.

図9 各 DAC の NTF 特性

#### 5. シミュレーション結果

表1にシミュレーション条件を示す.

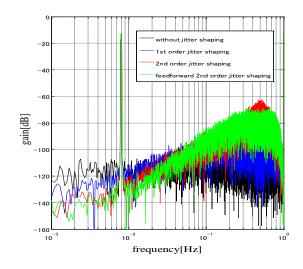

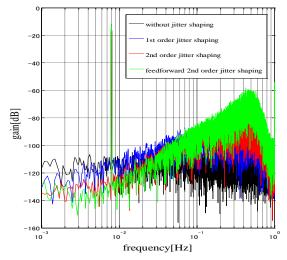

図 10 に MATLAB によるシミュレーションによる FFT 解析の結果を、図 11 に SPICE によるシミュレーションに よる FFT 解析の結果をそれぞれ示す.また,それぞれの FFT 解析で求められた SNR を表 2 にまとめた.

なお、出力信号はクロック間の平均値を取っているため、出力にはローパスフィルタがかけられている状態と 等しくなる.

| 表1 シミュレーション条 |

|--------------|

|--------------|

| 数1 * ( - , |           |           |  |

|------------|-----------|-----------|--|

|            | MATLAB    | SPICE     |  |

| INPUT      | -12[dBFs] |           |  |

| OSR        | 50        |           |  |

| Plot       | 10000     |           |  |

| jitter     | 1[%]      |           |  |

| Ts         | 1[sec]    | 100[nsec] |  |

図 10 MATLAB シミュレーションの FFT 解析結果

図 11 SPICE シミュレーションの FFT 解析結果

表2 シミュレーション結果

|                          | MATLAB    | SPICE      |  |

|--------------------------|-----------|------------|--|

| without jitter shaping   | 85.0[dB]  | 84.1[dB]   |  |

| 1st order jitter shaping | 96.4[dB]  | 90.0[dB]   |  |

| 2nd order jitter shaping | 105.8[dB] | 101.0[dB]  |  |

| FF 2nd order             | 10605101  | 105 05 101 |  |

| jitter shaping           | 106.9[dB] | 105.0[dB]  |  |

2 次のジッタシェーピングサンプルホールド DAC は、1次のジッタシェーピングサンプルホールド DAC よりも、FFT 解析結果からノイズフロアの傾きが倍になり、ジッタシェーピング特性が2次に高次化されたことがわかる.そして、SNR も9dB以上高くなり、ジッタシェーピング特性の高次化によって精度の向上が確認された.

また,2次化した二つのジッタシェーピングサンプルホールド DAC を比較すると、フィードフォワード型が精度が高く SPICE での劣化も少ない.この原因は、フィードバック型の経路内にスイッチトキャパシタを用いているため、余分なジッタ雑音の挿入と、NTF が変化してしまったためと考えられる.

SPICEによるシミュレーション結果のほうが MATLAB によるシミュレーション結果よりも性能が低いという結果となった. SPICE では、クロック信号で制御されるサンプルホールド回路と、スイッチトキャパシタ回路を verilogA によって作成した理想回路を使用している. しかし、それ以外はアナログ回路で作成を行っている. アナログ回路が MATLAB で作成した理想動作を再現できなかったために、雑音として表れて、精度を落としてしまったと考えられる.

#### 6. まとめ

本論文では、ジッタシェーピング特性を一次から二次に高次化したフィードバック型とフィードフォワード型の二つの構造を提案した。シミュレーションにより、提案した二次の構造は、従来の一次の構造よりも SNR が 10dB 程度向上し、手法の有効性が確認された。

謝辞:本研究を進めるに当たり、多くの指導・助言を頂いた法政大学理工学部安田彰教授に深く感謝申し上げます。また、この場をお借りしまして、様々な協力を頂いた同研究室の学生の皆様にも感謝申し上げます。

#### 参考文献

- 1) Richard Schreier, Gabor C. Temes 著 和保考夫, 安田彰 監訳: ΔΣ 型アナログ/デジタル変換器入門, 丸善, 2007

- 2)相良岩男:"A/D·D/A変換回路入門"日刊工業新聞社, 1991

- Cherry, J.A.; Snelgrove, W.M. "Clock jitter and quantizer metastability in continuous-time delta-sigma modulators" IEEE Trans. Circuits Syst. II, vol. 46, pp. 376– 389, Apr. 1999