# 法政大学学術機関リポジトリ

## HOSEI UNIVERSITY REPOSITORY

PDF issue: 2025-06-20

ノイズシェーピング構成とミスマッチシェーパーを用いた自己校正型パイプラインADCに 関する研究

小松, 直樹 / KOMATSU, Naoki

(発行年 / Year)

2012-03-24

(学位授与年月日 / Date of Granted)

2012-03-24

(学位名 / Degree Name)

修士(工学)

(学位授与機関 / Degree Grantor)

法政大学(Hosei University)

# 2011 年度 修士論文

ノイズシェーピング構成とミスマッチシェーパーを 用いた自己校正型パイプライン ADC に関する研究

A PIPELINED ADC USING BACKGROUND CALIBRATION

WITH MISMATCH SHAPER AND NOISE SHAPING ARCHITECTURE

指導教授 安田 彰 教授

法政大学大学院工学研究科 電気工学専攻修士課程 10R3121 小松 直樹

## Abstract

A novel background calibration technique for capacitor mismatches is proposed in this paper. The capacitor mismatch is one of the non-ideal factors in the pipelined ADC. This non-ideal factor deteriorates Signal to Noise Ratio (SNR) and Total Harmonic Distortion (THD). The conventional calibration method utilized both Noise Shaping Dynamic Element Matching (NSDEM) and a high-pass delta-sigma modulation. Recently, the architecture which is based on two step pipelined ADC and uses delayed quantization error to implement noise shaping function is studied. In this paper, we proposed a novel calibration method which uses NSDEM and this architecture. As a result, the SNR of the overall ADC can be improved.

Key Words: Capacitor mismatch, Digital Calibration, NSDEM, Pipelined ADC

# 目次

| 第 1 章 序論                                         | 4-     |

|--------------------------------------------------|--------|

| 第 2 章 AD,DA 変換器                                  | 5 -    |

| 2.1 AD 変換器                                       | 5 -    |

| 2.2 DA 変換器                                       | 9-     |

| 第 3 章 パイプライン型 ADC                                | - 12 - |

| 3.1 パイプライン型 ADC の基本構成                            | - 12 - |

| 3.2 MDAC の動作                                     | - 13 - |

| 第4章 従来の誤差検出法                                     | - 15 - |

| 4.1 ハイパス型 $\Delta$ $\Sigma$ 変調器について              | - 15 - |

| 4.1.1 ハイパス型 $1$ 次 $\Delta$ $\Sigma$ 変調器          | - 15 - |

| 4.1.2 ハイパス型 2 次 $\Delta$ $\Sigma$ 変調器            | - 17 - |

| 4.2 Noise Shaping Dynamic Element Matching       | - 19 - |

| 4.3 ハイパス型 Δ Σ変調器と NSDEM を用いた誤差検出法                | - 22 - |

| 4.3.1 ランダム信号を用いた相関演算による誤差検出法                     | - 22 - |

| 4.3.2 ハイパス型 $\Delta$ $\Sigma$ 変調器と NSDEM による検出方法 | - 26 - |

| 第5章 提案する誤差検出法                                    | - 28 - |

| 5.1 ノイズシェーピング型パイプライン ADC                         | - 28 - |

| 5.2 提案する誤差検出方法                                   | - 31 - |

| 第6章 シミュレーション結果                                   | - 33 - |

| 6.1 シミュレーション条件                                   | - 33 - |

| 6.2 ノイズシェーピング構成における補正結果の比較                       | - 36 - |

| 6.3 通常構成における補正結果の比較                              | - 38 - |

| 第7章 まとめと今後の課題                                    | - 44 - |

| 謝辞                                               | - 44 - |

| 参考文献                                             | - 45 - |

| 発表論文                                             | - 47 - |

|                                                  |        |

## 第1章 序論

超音波診断装置や MRI(核磁気共鳴)機器といった医療用画像処理アプリケーションは、 患者の病状の変化を的確に捉えることが重要であり、種々の高性能エレクトロニクス回路 で構成されている. 特にアナログディジタル変換器(ADC)に対しては、高コントラストイメ ージや高速動作を実現するために、"変換精度"と"変換速度"が最も重要な指標とされている.

パイプライン型 ADC は、この両面を満足する高速・高精度・低消費電力な ADC として、広く認知されている。最近では、医療用機器やディジタル・スチル・カメラだけでなく、3G/LTE ワイヤレス基地局やテスター・計測機器類の分野にも需要が増加している。

しかしながら、パイプライン型 ADC の内部 DAC を構成するキャパシタの製造上のばらつきにより、容量値にミスマッチが生じる. キャパシタは複数用いられるため、容量値のミスマッチに起因する変換精度の劣化は、避けられない問題である. 多くのシステムが要求する性能を満たすためには、キャリブレーション技術やトリミング技術が必要である[1-4].

そこで本論文では、パイプライン型 ADC の内部 DAC で生じるキャパシタミスマッチの 検出精度向上を狙い、ミスマッチシェーパーを用いた。また、内部 ADC で生じる量子化誤 差の影響を低減させるために、量子化誤差をフィードバックする構成を採用した。これら を組み合わせることで、高精度なバックグラウンドキャリブレーションを実現する構成を 提案する。

# 第 2 章 AD,DA 変換器

AD 変換とは、アナログ(A:analog)信号をディジタル(D:digital)信号に変換することである. アナログ信号とは光、音、映像など人間が五感で感じる事ができる現象であり、連続した信号の事である. ディジタル信号は音楽プレーヤーやコンピュータ等の電子機器の内部で用いられる信号であり、信号は離散値(0 と 1)の 2 値で表現される. この人間が理解する事ができるアナログ世界とコンピュータしか理解できないディジタル世界の橋渡しとしてAD 変換器が用いられている. 逆にディジタルの信号をアナログ信号に変換する場合にはDA 変換器を用いる. また AD 変換の事を符号化(Coder)、DA 変換の事を復号化(Decoder)ともいう. ディジタル化するメリットは情報の劣化が極めて少なく、たくさんの情報を保存するのに適している. また編集・加工・複製が容易に可能であり、2 次利用がしやすい点がある. ディジタル化されたデータを圧縮・セキュリティ技術と組み合わせることにより、信頼性・安全性の向上が可能であり、今日数多くの分野で ADC,DAC は用いられている. 近年の傾向として通信や映像分野のディジタル信号処理化と高集積化により今までにも増して性能の向上が求められている.

図 2.1 アナログーディジタル信号の変換イメージ図

#### 2.1 AD 変換器

アナログ入力を A,ディジタル出力を D とすると AD 変換は以下の関係式で表す事ができる.

$$D = f(A) \tag{2.1}$$

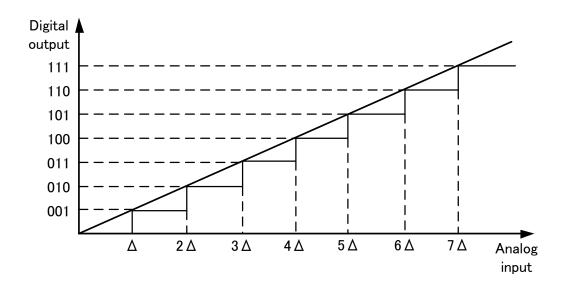

入力が連続の値であるとすると、出力は ADC の分解能に応じた有限の値のコードから選択される.このように ADC は入力信号をそれぞれ入力レベルに応じたコードに近似している.この近似は各コードに対応した参照電圧の生成、アナログ入力と各参照電圧を比較、入力値に近い参照電圧を選択する事により実現される.ほとんどの ADC において、アナログ入力は電圧である.図 2.2 は ADC の入出力特性である.アナログ入力は最も近い基準値に近似されている.アナログ入力は連続している信号であるが、この段階で離散値(基準値)になる.もしディジタル出力が m-bit バイナリであるとすると、出力は次式のようになる.

$$D = \left[2^m \frac{A}{V_{ref}}\right] \tag{2.2}$$

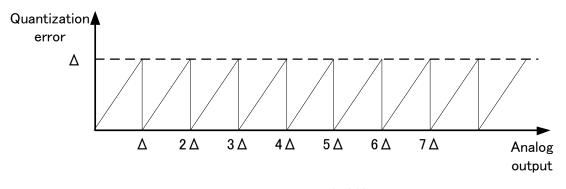

[]は整数の置き換えを、Vrefは入力のフルスケール電圧を示している.出力への変換で生じる入力の最大変化は $\Delta = V_{ref}/2^m$ となる.これはディジタル表現の最小 bit に相当する.ADC では必ず基準値に近似する過程が存在する.アナログ信号に対して,より細かく基準値を設ければディジタル信号に変換した際に,元のアナログ信号に近い値になる.例えば8ビットの場合,フルスケール(FSR)は $2^8 = 256$ 分割される.これを物差しとしてインパルスのアナログ振幅値を測定し,アナログ振幅値は 256 分割のどこかの離散値に四捨五入によって当てはめていく.このとき,連続量であるアナログ振幅値が不連続なディジタルとなるため,四捨五入による誤差が生じる.これを量子化誤差といい,ここではQと示す.これは  $\Delta D$  変換において本質的な誤差となり,これを回避することは不可避である.図 2.2(a)の入出力特性からQは図 2.2(b)のようになり,各コードが遷移する時に最大となる.この量子化誤差は分解能が増えるに従って減少する.また,この量子化誤差は出力においては量子化ノイズとなって現れる.このように"理想"のm-bitADCであっても量子化の段階でノイズが発生する.

図 2.2 ADC の入出力特性

(a) Input/Output characteristic (b) quantization error of an A/D converter

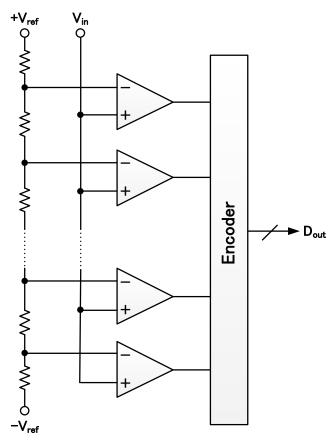

ADC によく用いられる全並列変換(フラッシュ型)方式の回路図を図 2.3 に示す.フラッシュ型 ADC の基本回路は基準電圧を分割する抵抗器群と,比較する比較器群と,n ビットの出力コードに変換するエンコーダから成り立っている. N ビット分解能のフラッシュ型 ADC を構成するためには, $2^n$  の直列に繋がった同じ抵抗値を持つ抵抗器と  $2^{n-1}$  のコンパレータが必要である.この両端に Vref を印加する.この結果,基準電圧が一定の電圧幅を持って分割され,各抵抗器端から階段状の分割電圧になって取り出す事ができる.この分割された電圧と入力アナログ電圧とを同時に  $2^{n-1}$  個のコンパレータで比較していく.比較した結果が「1」と「0」のディジタル値となって出力される.このディジタル値をデコードして,一般的なディジタルコードに変換して利用する.このフラッシュ型の変換精度は抵抗器の抵抗値精度で決まる.また変換速度は,コンパレータの判定速度やその後のディジタル回路がどれくらい速く反応できるかにかかっていて,この性能は最大変換速度として表現される.一瞬にしてコンパレータで全ての基準電圧において比較をするため,フラッ

シュ型は超高速動作が可能である. しかし、コンパレータが  $2^{n-1}$  個必要であり、また基準電圧を分割する抵抗も  $2^n$  個必要となり回路規模が膨大となる. 例えば 12bit 精度をフラッシュ型で実現しようと考えた場合には、コンパレータは 2047 個、抵抗器は 4096 個も必要となる. 得られる性能に対して、あまりにもハードウェアサイズが大きくなるため 10bit 以下の変換精度でしか用いられない.

図 2.3 フラッシュ型 ADC のブロック図

#### 2.2 DA 変換器

DA 変換とは、ディジタル(D:digital)信号をアナログ(A:analog)信号に変換する事である. DA 変換では3つのステップがあり、第1ステップでディジタル処理の完了した自然2進コード SBC によるディジタル信号を再生化(復号化)し、第2ステップで段階的なアナログ振幅値を持つインパルスをつくってここから振幅一定のパルスをつくり、再生フィルタ処理を行い、第3ステップでパルス列を滑らかにする後置フィルタを通しアナログ信号に変換していく.

ディジタル入力を D, アナログ出力を A とすると DA 変換は以下の関係式で表すことが出来る.

$$A = \alpha D \tag{2.3}$$

$\alpha$ は比例因数である. D は次元を持たないので $\alpha$ は次元と A のフルスケールを併せ持つ. 例えば、もし $\alpha$ がIrefという電流量であるとき出力は次式となる.

$$A = I_{ref} D (2.4)$$

分解能を m-bit としたとき D をフルスケールの  $2^n$ 分割する事によって標準化することがより標準的である. 例えば、 $\alpha$ が電圧量Vrefとすると

$$A = V_{ref} \frac{D}{2^m}$$

(2.5)

(2.4)式と(2.5)式から、DA変換はディジタル入力の各コードはアナログの出力を参照値の倍数や比から生成している.言い換えると、DA変換は電圧、電流、電荷で表される参照値からの乗算、除算であることがわかる.DA変換の精度はDACの線形性で決まり、速度は基準電圧の倍数や分数から出力を選択、生成するDACの変換速度で決まる.

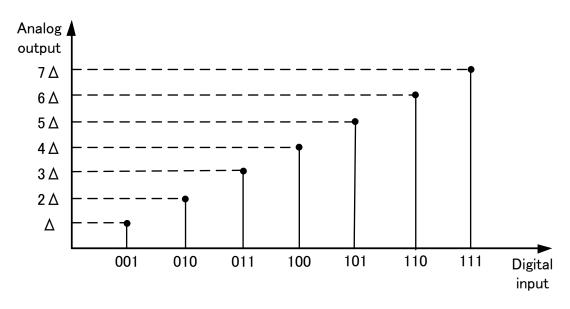

図 2.4 は理想の 3bit の DAC の入出力特性である. 出力として生成されるアナログ値は原点とフルスケールポイントを通る直線となっている.

図 2.4 DAC の入出力特性

DAC のディジタル入力にはいくつかのフォーマットがある. 表2.1 はDAC でよく使われるフォーマットで,Binary, Thermometer, 1-of-n コードを表した表である. Binary では, m-bit バイナリ $D_{m-1}D_{m-2}\cdots D_o$ は10 進数で $D_{m-1}2_{m-1}+D_{m-2}2_{m-2}+\cdots+D_o$ 20の値を表現する.

Thermometer は、列の下から連続した「1」と上からの連続した「0」で表現する. 1-of-n コードでは、列中の「0」の中から一つの「1」を選ぶ表現をする. 「1」が選ばれたポジションが値を示す.

表 2.1 Binary, Thermometer, 1-of-n コード

| Decimal                               | 0  | 1  | 2  | 3  |

|---------------------------------------|----|----|----|----|

| Binary                                | 00 | 01 | 10 | 11 |

| Thermometer                           | 0  | 0  | 0  | 0  |

|                                       | 0  | 0  | 0  | 1  |

|                                       | 0  | 0  | 1  | 1  |

|                                       | 0  | 1  | 1  | 1  |

| 1-of-n                                | 0  | 0  | 0  | 0  |

|                                       | 0  | 0  | 0  | 1  |

|                                       | 0  | 0  | 1  | 0  |

|                                       | 0  | 1  | 0  | 0  |

| · · · · · · · · · · · · · · · · · · · |    |    |    |    |

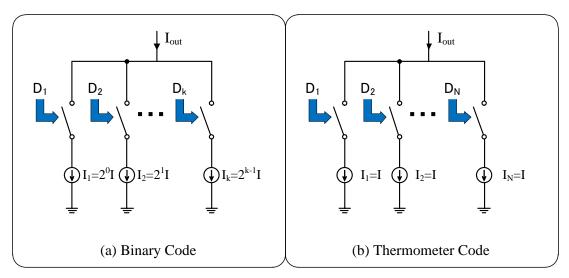

図 2.5 に一般的な電流分割型 DAC の構成を示す. (a)はディジタル入力が Binary コード の場合であり, すべての電流源にバイナリ重みがつけられている. ディジタル入力が上位 bit へ桁が推移するにつれ, 出力は 2 倍になる. (b)はディジタル入力が Thermometer コード の場合であり, すべての電流源は等価である. この場合, ディジタル入力が 1LSB 増加する と, 電流源が 1 つ出力側に接続される.

図 2.5 一般的な電流分割型 DAC

# 第3章 パイプライン型 ADC

パイプライン型 ADC は、高品質な医療用画像アプリケーションや高性能な無線基地局など、多くのエンド・アプリケーションが要求する"高精度""高速動作""低消費電力"に適した構成である。フラッシュ型等の低分解能 ADC が多段接続され、パイプライン動作を行うことで、複数の処理を 1 クロック内で進める ADC である.

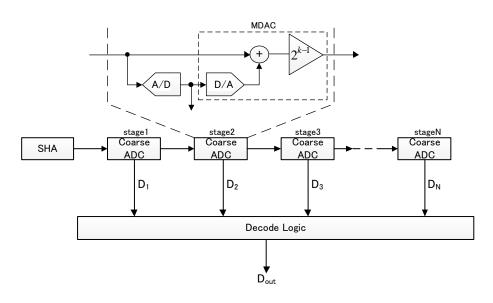

#### 3.1 パイプライン型 ADC の基本構成

一般的なパイプライン型 ADC の構成を図に示す. ADC は通常,複数のステージが縦続接続されて構成される. 各ステージはそれぞれ,"内部 ADC""内部 DAC""減算器""係数アンプ"によって成り立つ. 特に"内部 DAC""減算器""係数アンプ"は,乗算型 DAC(MDAC) として扱われる.

アナログ信号が入力されると、まず S/H 回路の働きによりサンプリングされる. このサンプル値は内部 ADC によって量子化され、ディジタル信号として出力される. さらにこのディジタル信号は内部 DAC によってアナログ値化され、減算器で入力信号との差分が取られる. この残差が係数アンプによってスケーリングされ、下段のステージでも同様に変換が行われる. このようにパイプライン動作が進められ、システム全体の出力は各ステージの ADC の出力をディジタル回路で補正し、統合することで得られる.

図 3.1 パイプライン型 ADC

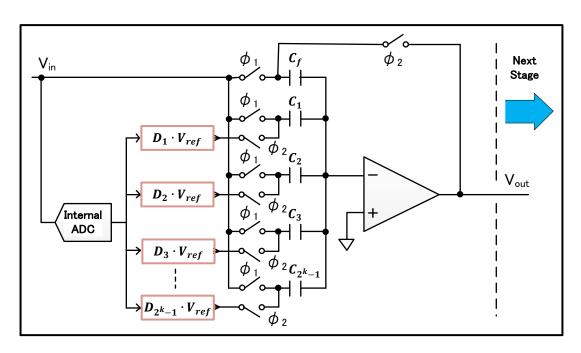

#### 3.2 MDAC の動作

図 3.2 MDAC の構成と動作信号

図 3.2 に MDAC を示す. k-bit の分解能を持つ内部 ADC によって変換されたディジタル値は、MDAC にある  $2^k$ -1 乗のキャパシタを選択する. 例えば 3 ビットの場合キャパシタ数は 7 つとなり、全ての容量は等しい.

まず $\phi$ 1がオンとなり、入力信号が各キャパシタにサンプリングされた状態を考える.この時、蓄えられる電荷は次のようになる.

$$Q = (C_1 + C_2 + C_3 + \dots + C_{2^{k}-1})V_{in}$$

(3.1)

$$Q_f = C_f V_{in} (3.2)$$

次に $\phi$ 1 をオフし、DAC 側の $\phi$ 2 をオンした状態を考える.ここで D は内部 ADC の出力によって選択されるコードであり、該当するキャパシタが選択された場合は 1 を、そうでなければ 0 を出力する.

$$Q' = (D_1C_1 + D_2C_2 + D_3C_3 + \dots + D_{2^k-1}C_{2^k-1})V_{\text{ref}}$$

(3.3)

$$Q'_f = C_f V_{out} (3.4)$$

以上 2 つの状態に対し、オペアンプのマイナス入力部で電荷保存則が成り立つことを考慮すると、以下の式が得られる.

$$-(Q + Q_f) = -(Q' + Q'_f)$$

(3.5)

全キャパシタの容量値が等しい場合、(3.5)式から次式が得られる.

$$V_{out} = 2^k V_{in} - (D_1 + D_2 + D_3 + \dots + D_{2^{k}-1}) V_{ref}$$

(3.6)

(3.6) 式は全ての容量値が等しく製造され、且つ環境変化による値の変動が無い理想的な場合である. しかし実際は、製造上のばらつきや環境変化による値の変動が無視できず、 次式のようになる.

$$\begin{split} \mathbf{V}_{out} &= \left(1 + \frac{C_1 + C_2 + C_3 + \dots + C_{2^k - 1}}{C_f}\right) V_{in} \\ &- \left(D_1 \frac{C_1}{C_f} + D_2 \frac{C_2}{C_f} + D_3 \frac{C_3}{C_f} + \dots + D_{2^k - 1} \frac{C_{2^k - 1}}{C_f}\right) V_{ref} \end{split} \tag{3.7}$$

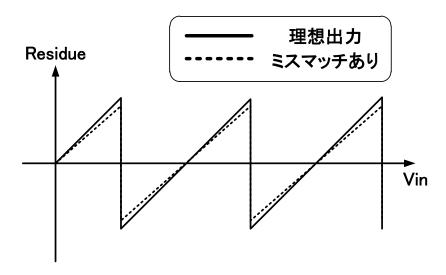

この理想的な場合とキャパシタに誤差がある場合の比較を図 3.3 に示す。(3.7)式から, $C_f$  とその他キャパシタの相対誤差が DAC 誤差になる。誤差は後段で同様に変換されるが,誤った変換値を出力することになり,これが精度劣化の一因となる。

図 3.3 キャパシタミスマッチが与える DAC 誤差

## 第4章 従来の誤差検出法

本章では、従来の誤差検出方法を三要素に分けて紹介する。まず、通常 flash 型 ADC が用いられる内部 ADC に、量子化誤差の影響を抑えるために置換した "ハイパス型  $\Delta$   $\Sigma$  変調器" について説明する。次にキャパシタミスマッチの周波数特性に、シェーピングを持たせることができる "Noise Shaping Dynamic Element Matching(NSDEM)" について説明する。最後に、相関演算によるバックグラウンド検出法[5]と、これらを組み合わせた誤差検出構成について説明する。

### 4.1 ハイパス型 Δ∑変調器について

#### 4.1.1 ハイパス型 1 次 △ ∑ 変調器

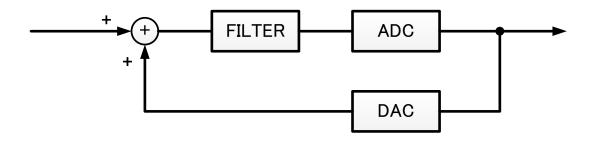

図 4.1 に 1 次ハイパス型  $\Delta$   $\Sigma$  変調器のブロック図を示す.  $\Delta$   $\Sigma$  変調器は Filter, ADC, DAC, 加算器から構成される. [6]

図 4.1 1次ハイパス型  $\Delta \Sigma$  変調器のブロック図

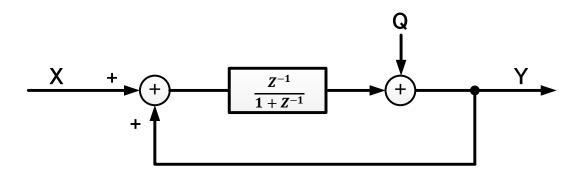

図 4.2 z 領域で表現した 1 次 Δ Σ 変調器

図 4.2 に z 領域で表した 1 次ハイパス型  $\Delta$   $\Sigma$  変調器のブロック図を示す. 図からこのシステムの伝達関数は以下のようになる.

$$Y(z) = z^{-1}X(z) + (1+z^{-1})Q(z)$$

(4.1)

ここで O(z)は量子化誤差であり、上式より Noise Transfer Function(NTF)は

$$NTF = (1 + z^{-1}) (4.2)$$

となり、NTFのゼロ点を z=-1 の点で重解として得る. これは、サンプリング周波数の半分、すなわちナイキスト周波数において、量子化誤差が最小となることを意味する. この特性を持つ  $\Delta$   $\Sigma$  変調器はハイパス型  $\Delta$   $\Sigma$  変調器と呼ばれている. DC オフセットや 1/f ノイズの影響は、ハイパス型  $\Delta$   $\Sigma$  変調器では本質的に抑制する事が可能である. 加えて、ゼロ点が重解であるため、2 次のノイズシェーピング[7]を得る事ができる点でローパス型  $\Delta$   $\Delta$  変調器より優れている.

次に、数式上でナイキスト周波数付近の量子化誤差が抑圧されるか確認する. NTF は(4.3) 式のように記述できる. この NTF が 0 となるような状態の時に、量子化誤差が一番抑圧されるので、その時の周波数を考える.

$$1 + z^{-1} = 1 + \exp(-j\omega T)$$

(4.3)

(4.3)式はz領域から周波数領域に式変換されたものであり、右辺が0となるためにはexp  $(-j\omega T) = -1$  となるような $\omega$  を求めれば良い.

$$\exp(-j\omega T) = \cos(\omega T) - j\sin(\omega T)$$

$$= \cos(2\pi f \cdot T) - j\sin(2\pi f \cdot T)$$

$$= \cos\left(2\pi \frac{f}{f_s}\right) - j\sin(2\pi \frac{f}{f_s}) \tag{4.4}$$

fsはサンプリング周波数である.ここでf=0.5fs(ナイキスト周波数)とすると以下のようになる.

$$=\cos(\pi) - j\sin(\pi) = -1 \tag{4.5}$$

ナイキスト周波数でNTFが0になる事が式より証明された。ナイキスト周波数付近で量子 化誤差が低減される特性はノイズシェーピングと呼ばれている。このノイズシェーピング の特性を定量的にみると, $\Delta$   $\Sigma$  変調器の次数が1増加するごとに20dB/decade利得減衰特性 が増え、1次では20dB/decadeの特性を示す。

#### 4.1.2 ハイパス型 2 次 Δ Σ 変調器

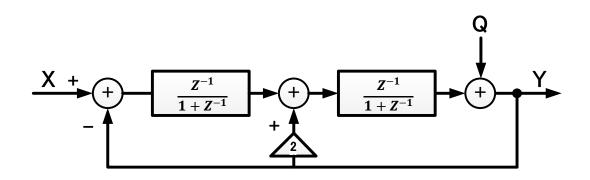

図 4.3 に z 領域で表した 2 次ハイパス型  $\Delta$   $\Sigma$ 変調器を示した. 従来方法では十分量子化 誤差を低減した上で相関を取りたいので 2 次  $\Delta$   $\Sigma$ 変調器を用いた. ノイズシェーピング特性は量子化誤差 Q(z)の係数 $(1+z^{-1})$ の次数で決まる. この次数を 2 次にすれば,ノイズシェーピング特性を 40dB/decade にする事ができる. これにより,1 次  $\Delta$   $\Sigma$ 変調器よりもナイキスト周波数付近の量子化誤差を低減する事ができる.

図 4.3 z 領域で表現した 2 次 Δ Σ 変調器

図 4.3 からこのシステムの伝達関数は以下のようになる.

$$\left(X(z) - Y(z)\right) \frac{z^{-2}}{(1+z^{-1})^2} + 2Y(z) \frac{z^{-1}}{1+z^{-1}} + Q(z) = Y(z) \tag{4.6}$$

$$\left(\frac{z^{-2}}{(1+z^{-1})^2} - \frac{2z^{-1}}{1+z^{-1}} + 1\right)Y(z) = \frac{z^{-2}}{(1+z^{-1})^2}X(z) + Q(z)$$

(4.7)

$$Y(z) = z^{-2}X(z) + (1+z^{-1})^2Q(z)$$

(4.8)

Q(z)に $(1+z^{-1})^2$ という係数が掛かっているため、ナイキスト周波数付近で急峻なシェーピングがかかる。3 次以上の  $\Delta$   $\Sigma$  変調器も考えられるが、回路規模、安定性の問題があるた

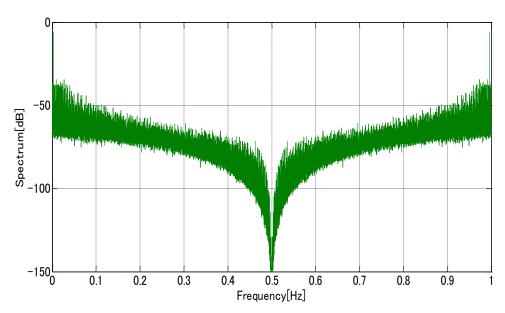

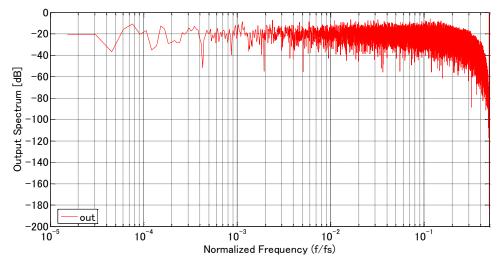

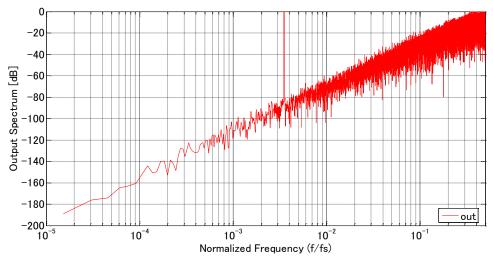

め今回は 2 次の  $\Delta$   $\Sigma$ 変調器を用いる。図 4.4 に MATLAB/Simulink により設計した 2 次ハイパス型  $\Delta$   $\Sigma$ 変調器のシミュレーション結果を示す。この出力スペクトラムから高域(ナイキスト周波数付近)の量子化誤差に対してシェーピングが掛かっていて、抑圧されている事がわかる。

図 4.4 2 次ハイパス型  $\Delta$   $\Sigma$  変調器の FFT スペクトラム

### 4.2 Noise Shaping Dynamic Element Matching

前項で紹介したハイパス型 Δ Σ 変調器は、ナイキスト周波数付近の量子化誤差を帯域外 ヘシフトすることで、高域でキャパシタミスマッチを検出できるようにした。この状態で も検出はできるが、さらに正確に検出できるように、キャパシタミスマッチを高域へシフ トする手法を紹介する。

キャパシタの選択に対しては、これまでにランダマイザを用いた方法が研究されてきた. ランダマイザではキャパシタミスマッチの均一化をする事はできるが、ミスマッチをある 領域へシフトさせる事はできなかった.そこでキャパシタミスマッチにシェーピング特性 を与えられる NSDEM( Noise Shaping Dynamic Element Matching)を用いる[8-9]. この NSDEM を用いた場合、1 次のシェーピング特性が得られる DWA(Data Weighted Averaging)アルゴリ ズムよりも高域へミスマッチによる雑音をシフトできる[10].

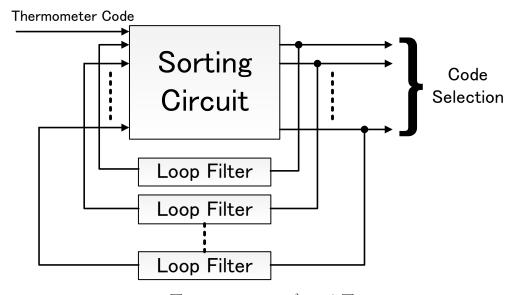

図 4.5 NSDEM のブロック図

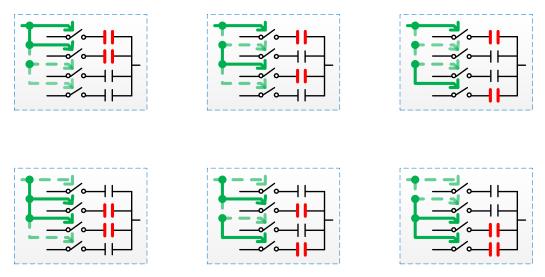

図 4.5 に NSDEM のブロック図を示す. 出力は入力数だけ加算するタイプの DAC と考えられる. 3bit の場合にはコード選択としては8本となる. NSDEM ではセル各々の選択の0,1を複数回積分し、その結果の小さい順に入力数だけセルを選択する. すなわち各セルの使用の有無の積分値が一定値になるように制御をかける形となっている. これにより、誤差成分は出力において2次のノイズシェーピングを受ける. このため、従来使用されている1次シェーピング効果を持つDWAよりもミスマッチを押し上げる事ができる. ループフィルタはミスマッチを高域に押し上げるためにミスマッチに対してハイパスフィルタになっている.

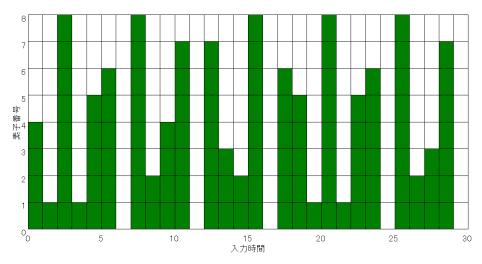

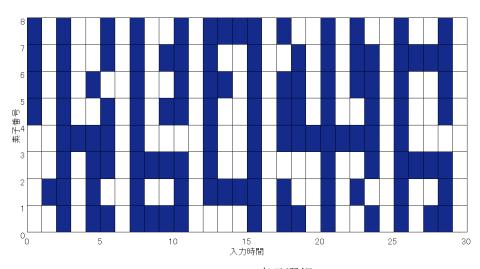

図 4.6 は通常のキャパシタの素子選択と NSDEM を用いた素子選択を比較した図である. NSDEM による選択方法ではランダム状に選択が行われる.

(a) 通常の素子選択

(b) NSDEM の素子選択

図 4.6 NSDEM によるキャパシタ選択の様子

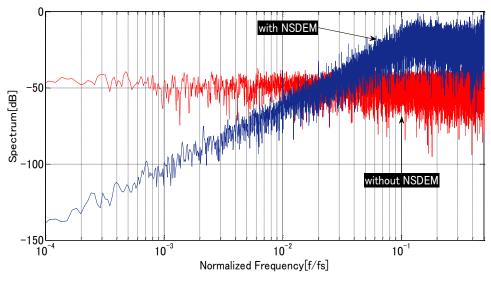

図 4.7 に 1%のキャパシタミスマッチのシェーピングの様子を示した. 3bit の DAC に用いるキャパシタに±1%の誤差を与えた. 8 つのキャパシタを選択する時にランダマイザを用いた場合と NSDEM を用いた場合で比較検討した. 図 4.7 の緑色で示したスペクトラムがランダマイザを用いた時のキャパシタミスマッチの分布である. 全周波数帯域に対して均一に分布している様子がわかる. これに対して青色で示したスペクトラムが NSDEM をかけたものである. NSDEM をかけた方は高域(ナイキスト周波数)にミスマッチがシフトされて

いる様子がわかる.このようにミスマッチがシフトされることで、高域での検出精度が高められる.

図 4.7 キャパシタミスマッチのスペクトラム

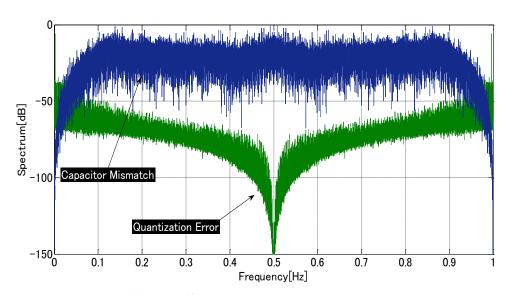

図 4.8 は前項で説明したハイパス型  $\Delta$   $\Sigma$ 変調器と NSDEM を用いた時の,量子化誤差とミスマッチに対する出力スペクトラムである.ナイキスト周波数付近(横軸 0.5)では量子化誤差がハイパス型  $\Delta$   $\Sigma$ 変調器により抑圧され,NSDEM によりキャパシタミスマッチが押し上げられている様子が確認できる.

図 4.8 量子化誤差とキャパシタミスマッチのスペクトラム

#### 4.3 ハイパス型ΔΣ変調器と NSDEM を用いた誤差検出法

本項では、相関演算を用いたバックグラウンドによる誤差検出法を紹介する. さらにこの誤差検出法に、"ハイパス型  $\Delta$   $\Sigma$  変調器" と "NSDEM" を組み合わせた手法について説明する. [11]

#### 4.3.1 ランダム信号を用いた相関演算による誤差検出法

ランダマイザのセレクトコードと後段に出力された誤差の相関を取るという事はどういうことなのか説明する. 例えば、1つのステージで 2bit の変換を行うとすると内部 DAC ではキャパシタの数が  $2^2$  = 4 となり、4 つ必要となる. 入力信号がフルスケールの場合には全てのキャパシタ(4つ)が選択される. しかし、ハーフスケールの場合には 2 つしか選択されない. ここでランダマイザを用いて 2 つのキャパシタを選択する場合について考えてみる. 4 つのキャパシタの中から 2 つのキャパシタを選択する時に、選択されうる可能性は 6 通りである. それぞれのキャパシタの誤差が違うので、6 通りの誤差が後段に出力される事になる. つまり、ここで選択したセレクトコードに対応した誤差が得られるので、セレクトコードと後段の出力には相関があると言える.

図 4.9 4 つのキャパシタから 2 つを選択する組み合わせ

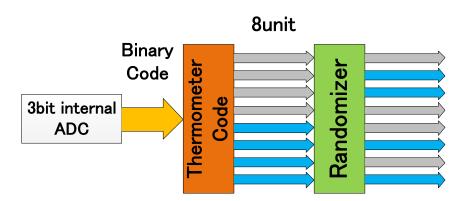

次に式を用いて相関演算について考えてみる. まず内部 ADC のバイナリ出力を温度計コードに変換して、その後ランダマイザに通してから、 $2^k$  個のキャパシタそれぞれを制御する  $2^k$ 系列の Pseudo Noise(PN)信号を作る. 時刻 t におけるステージ1 の内部 ADC 出力 ADC<sub>1</sub>が(4.9)を満足するようにとる.

$$\sum_{m=1}^{2^k} PN_m(t) = ADC_1(t) \tag{4.9}$$

(4.9)は、時刻 t における PN 信号 M 系列の総和が時刻 t におけるステージ 1 の内部 ADC 出力 ADC<sub>1</sub> となることを示している。MDAC を構成するキャパシタ誤差を $\varepsilon_m$  とする。時刻 t におけるステージ 1 の残差 $Res_1$  は(4.10)となる。

$$Res_{1}(t) = V_{in}(t) - \sum_{m=1}^{2^{k}} PN_{m}(t)(1 + \varepsilon_{m})$$

(4.10)

時刻 t におけるステージ 1 の量子化誤差 $Q_1$  は(4.11)となる.

$$Q_1(t) = V_{in}(t) - \sum_{m=1}^{2^k} PN_m(t)$$

(4.11)

ステージ 1 から出力された残差は後段ステージの ADC で変換される. 時刻 t における後段ステージの ADC 出力 ADC $_2$  は,後段ステージの量子化誤差を $Q_2$  とすると(4.12)となる.

$$ADC_2(t) = Q_1(t) + Q_2(t) - \sum_{m=1}^{2^k} PN_m(t)\varepsilon_m$$

(4.12)

ここで(4.9)のランダマイザ出力と、(4.12)の後ステージ ADC 出力に相関をとる. 演算結果は(4.13)となる.

$$PN_{m}(t) \otimes ADC_{2}(t)$$

$$= PN_{m}(t) \otimes \left( (Q_{1}(t) + Q_{2}(t)) - \sum_{m=1}^{2^{k}} PN_{m}(t)\varepsilon_{m} \right)$$

(4.13)

(4.13)において、 $\otimes$ は相関を示す記号である。また PN 信号と量子化誤差  $Q_1$ 、PN 信号と量子化誤差  $Q_2$  の相関は  $Q_3$  の相関は  $Q_3$  の相関は  $Q_3$  の相関は  $Q_3$  の相関は  $Q_3$  の相関は  $Q_4$  のおるとすると、相関演算を行った結果、PN 信号に相関のあるキャパシタ誤差が導出される。キャパシタ誤差は(4.14)として検出される。

$$\varepsilon_m = -\frac{1}{N} \sum_{t=1}^{2^k} PN_m(t) \otimes ADC_2(t)$$

(4.14)

(4.14)からランダム信号と後段の ADC の結果の相関を取り足し合わせたものが誤差となっている事がわかる. つまり,図 4.11 のランダマイザのセレクトコードと,後段の ADC の結果の相関を取るという事である. またこの式に PN 信号がある事から,セレクトコードが検出される誤差に関係している事も読み取れる. この演算を誤差検出時間中に繰り返し行い,各キャパシタの誤差値にわけて積分を行う. 個々のキャパシタ誤差積分値を,それに対応したキャパシタの誤差検出演算回数で除算する事でキャパシタ 1 つ当たりに対する誤差が検出される.

図 4.10 内部 ADC とランダマイザの出力の関係

図 4.11 相関演算を用いた誤差検出ブロック

#### 4.3.2 ハイパス型 Δ Σ 変調器と NSDEM による検出方法

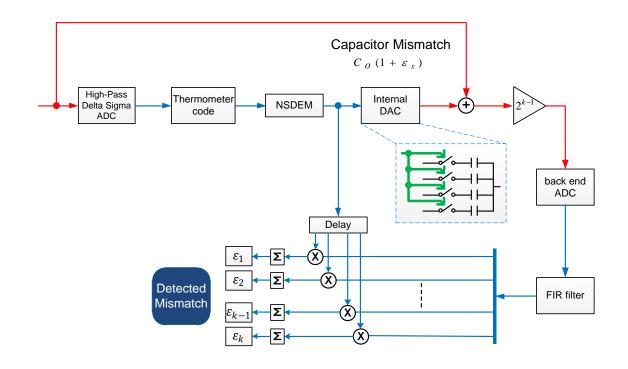

図 4.12 従来の誤差検出回路

内部 ADC に "ハイパス型  $\Delta$   $\Sigma$  変調器" を適用し、キャパシタの選択に NSDEM を用いる構成を、図 4.12 に示す.

まず入力はハイパス型  $\Delta$   $\Sigma$ 変調器によってディジタル値に変換される. これを温度計コードに変換したものが NSDEM に入力され, NSDEM による選択コードがキャパシタをスイッチングする. この時の量子化誤差とミスマッチは図 4.8 のようになり高域においてスペクトルは分離される. 入力信号からこの内部 DAC 出力をサブトラクタで減算演算し,係数倍した後に後段に出力される. そして検出対象成分(ナイキスト周波数付近)のみを FIR フィルタで選択し、NSDEM で選択したコードとの相関を取り、誤差成分を積分する. 最終的には誤差検出を繰り返した回数で除算する事により、1 つあたりのキャパシタのミスマッチが算出できる.

しかし、FIR フィルタでは量子化誤差だけでなく、拡散しているキャパシタミスマッチも取り除いてしまう。そうすると本体の誤差より値が小さくなってしまう。そこで、通過帯域とナイキスト周波数の比から計算されるゲインを掛ける。FIR フィルタの伝達関数は次のようになる。

$$H(z) = a_0 + a_1 z^{-1} + a_2 z^{-2} + \dots + a_{n-1} z^{-(n-1)} + a_n z^{-n}$$

(4.15)

ここで、 $a_n$ はフィルタ係数である。フィルタの通過帯域とナイキスト周波数から算出される比を $g_r$ と定義すると、以下のようになる。

$$g_r = \frac{\sum_{i=0}^n a_i^2}{n} \tag{4.16}$$

ミスマッチは前述の通りノイズシェーピング特性を有しており、補正後のスペクトラムも同様に $g_s$ と定義すると、ミスマッチの補正式は以下のようになる.

$$\varepsilon_{x}^{*} = \varepsilon_{x} \times \frac{g_{s}}{g_{r}} \tag{4.17}$$

## 第5章 提案する誤差検出法

前章では "ハイパス型  $\Delta$   $\Sigma$  変調器" と "NSDEM" を用いた誤差検出法について紹介した. それぞれの役割は

- ① ハイパス型 Δ Σ変調器・・・内部 ADC で発生する量子化誤差の影響を抑える

- ② NSDEM・・・ミスマッチの周波数特性を変え、検出精度を高める

であった.このことから、この二点がキャリブレーションにおいて重要な役割を担っていることがわかった.

そこで本章では①の役割に注目し、ハイパス型  $\Delta$   $\Sigma$  変調器に替わる、量子化誤差の影響を抑えることができる構成を紹介する。そしてこの構成と②NSDEM を組み合わせた誤差検出法について説明する。

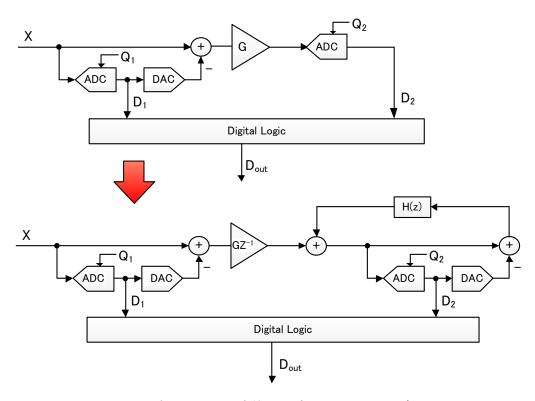

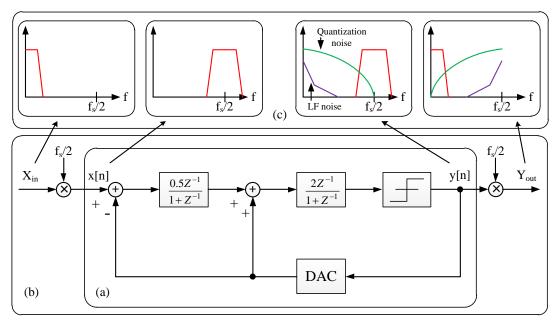

### 5.1 ノイズシェーピング型パイプライン ADC

図 5.1 ノイズシェーピング型パイプライン ADC のブロック図

図 5.1 にノイズシェーピング型パイプライン ADC を示す[12]. 通常の変換と同様, サンプルされた信号は内部 ADC で量子化され, そのステージの出力となる. この出力は内部 DAC でアナログ信号に変換され,入力信号との差分が取られる.

ノイズシェーピング型パイプライン ADC では、この差分を係数倍し、遅延を加えて次段へ送る.次段でも前段と同様に変換が進められるが、このステージでは得られた差分を、フィルタを介してステージの入力部分にフィードバックする.

図から、各ステージの出力 D<sub>1</sub>, D<sub>2</sub> は次のようになる.

$$D_1 = X + Q_1 (5.1)$$

$$D_2 = -z^{-1}GQ_1 + (1 - H(z))Q_2 \tag{5.2}$$

Digital Logic で、遅延補正とスケーリングを行うことで、最終的な出力は以下のようになる

$$D_{\text{out}} = D_1 \cdot z^{-1} + \frac{D_2}{G} = z^{-1}X + (1 - H(z))\frac{Q_2}{G}$$

(5.3)

(5.3)式から、1 次遅れを伴った入力信号と、(1-H(z))倍された量子化誤差の 2 項の和で出力されることがわかる。このことから、H(z)の値次第で量子化誤差に任意のシェーピング特性を与えることが可能となる。例えば、 $H(z)=z^{-1}$ とした場合 1 次のローパス特性を持つことになる。

しかし、キャパシタにミスマッチを与えた場合、以下のようになる.

$$D_{out} = z^{-1} \left( X - \sum_{m=1}^{2^k} \varepsilon_m \right) + (1 - H(z)) \frac{Q_2}{G}$$

(5.4)

(5.4)式から、キャパシタミスマッチが入力信号と同様に、遅延を伴ってそのまま出力されることがわかる。故にノイズシェーピング構成においても、キャパシタのミスマッチはシステムの性能を劣化させる最大原因の一つであると言える。

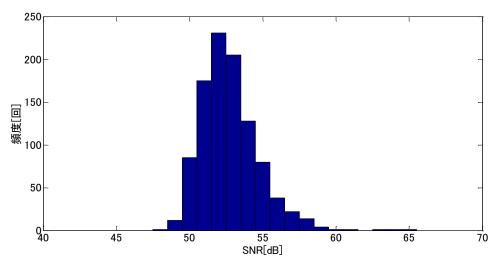

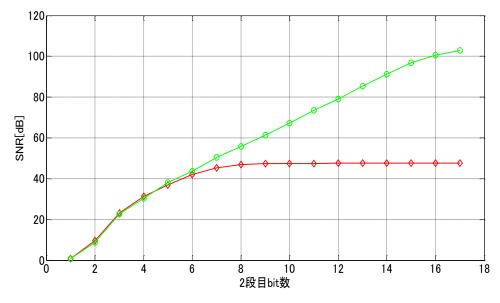

ミスマッチが及ぼす性能劣化をモンテカルロ解析した結果を図 5.2 に示す. 前段を 3bit, 後段を 11bit とし、全体を 14bit とした 2 段構成とする. さらに、正規乱数により付与したキャパシタミスマッチの $\sigma$  値は 1%とし、シミュレーション回数は 1000 回とした. この場合、ミスマッチの無い理想的な状態であれば、SNR は約 80[dB]となる. しかしながら、図

からわかるように、ミスマッチを与えた場合 SNR は 52[dB]程度まで劣化することがわかった.

同様の条件で 2 段目のビット数を変化させた時の, SNR の変化をプロットしたものを図5.3 に示す. 2 段目の分解能が 6bit を超えた頃から,システムの性能劣化が始まっている. そのため,2 段目を 6bit 以上のシステムとする場合,何らかのキャリブレーションが必要と考えられる.

図 5.2 ミスマッチによる SNR のヒストグラム

図 5.3 ミスマッチが及ぼす影響

#### 5.2 提案する誤差検出方法

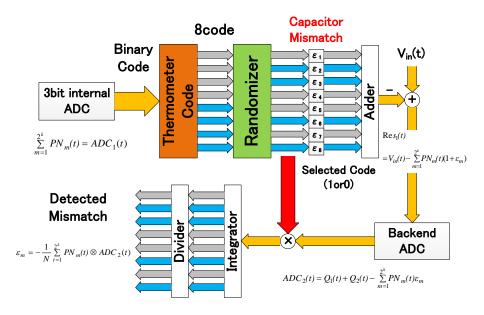

図 5.4 提案する誤差検出ブロック図

図 5.4 にノイズシェーピング構成と相関演算を組み合わせた誤差検出ブロックを示す. 前節から, 初段の DAC にキャパシタミスマッチが発生した場合, ADC の出力は(5.4)式となることがわかった. 提案手法では, この出力と NSDEM で選択したコードとの相関を取り, 誤差成分を積分する. 最終的には誤差検出を繰り返した回数で除算することで, それぞれのキャパシタのミスマッチが算出できる. NSDEM による選択信号は(4.9)式で表すことができる. そのため, 提案手法による誤差検出は(4.9)式と(5.4)式から

$$PN_{m}(t) \otimes D_{out}$$

$$= PN_{m}(t)$$

$$\otimes \left(z^{-1}\left(X - \sum_{m=1}^{2^{k}} PN_{m}(t)\varepsilon_{m}\right) + (1 - H(z))\frac{Q_{2}}{G}\right)$$

(5.5)

(5.5)式で表現できる. 式から選択信号は,入力信号・ミスマッチ・量子化誤差のそれぞれと相関を取ることになるが,入力信号は FIR フィルタにより除去され,量子化誤差と選択信号は無相関であるため,(5.5)式は最終的に次のようになる.

$$\varepsilon_{\rm m} = -\frac{1}{N} \sum_{m=1}^{2^k} PN_m(t) \otimes D_{out}$$

(5.6)

よって、各キャパシタのミスマッチを検出することができる. 4.3.2 項で説明した通り、本 提案手法でも FIR フィルタによって切り取った部分に対する補正が必要である.

## 第6章 シミュレーション結果

## 6.1 シミュレーション条件

MATLAB/Simulink を用いて、今回提案した誤差検出方法の検証を行った. 本提案手法の応用例として以下の二例が考えられる.

- ① 2段のノイズシェーピング構成のパイプライン型 ADC のミスマッチの検出・補正

- ② 複数段で構成されるパイプライン型 ADC の特定段のミスマッチの検出・補正

よって本論文でも、この応用例に即した検証を行った.

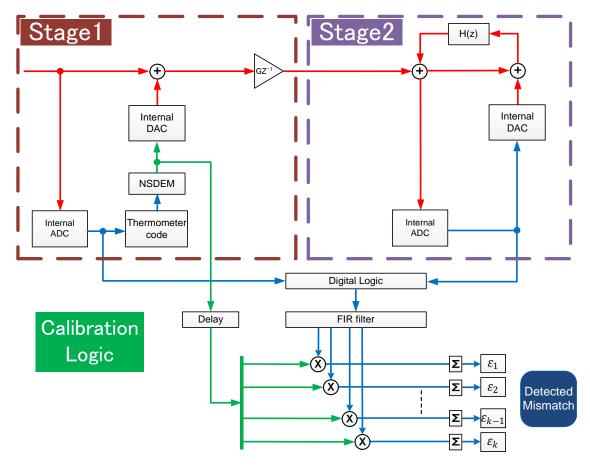

図 6.1 シミュレーションで用いる誤差検出ブロック

図 6.1 に今回のシミュレーションで誤差を検出するブロック図を示す. 検出ブロックは "Stage1" "Stage2" "Calibration Logic"の三要素で構成される. Stage1 と Stage2 はパイプライン型 ADC を形成し, Stage2 に対しては前述のノイズシェーピング構成を用いるため,

フィルタを介して出力をフィードバックしている.フィルタは,2次のノイズシェーピングが得られるように設計した.また初段は3bit構成,後段は11bit構成とし,全体の分解能を14bit構成とした.初段は2bit構成でも,NSDEMによるシェーピングの効果を確認することができるが,2bitの場合の選択される組み合わせは16通り,3bitの場合は256通りであるため,選択数を増やすために今回は3bit構成とした.

また初段の誤差が最も変換精度に影響する事や、検出回路の特性を確認するため初段のMDACにキャパシタミスマッチを±1%与えた。

"Calibration Logic"では、パイプライン型 ADC から得られた出力と、NSDEM の選択信号で相関演算を行うことで、キャパシタミスマッチを検出する.

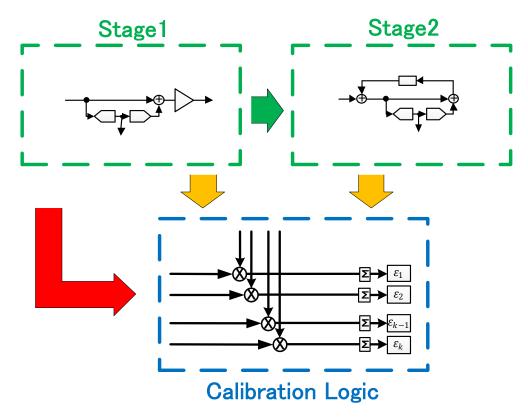

図 6.2 (a)ハイパス型 2 次  $\Delta$   $\Sigma$  変調器(b)ミキサーによる周波数変換ブロック (c)各点における周波数スペクトラム

次にハイパス型システムの評価方法について説明する. 図 6.2 はミキサーを用いてハイパス型 2 次  $\Delta$   $\Sigma$  変調器を評価するためのブロック図である[13]. 通常の片対数グラフを用いる場合,ハイパス型システムでは周波数スペクトラムに占める入力帯域の割合が狭いため,結果の判断が難しい場合がある. そこでミキサーを用いて,周波数変換を行い,ローパス型システムと同様の評価をできるようにする. ミキサーは周波数変換をすることが目的であり,本論文ではミキサーを含めたシステムの評価は検証対象外であるため,ミキサーは全て理想状態とした.

図 6.3(a)にハイパス型  $\Delta \Sigma$ 変調器の出力スペクトラム(出力: y[n])を, (b)にミキサーによって周波数変換を行ったシステムの出力スペクトラム(出力:  $Y_{out}$ )を示す.

(a)ハイパス型 2 次  $\Delta$   $\Sigma$ 変調器の出力スペクトラム

(b)ミキサーによって周波数変換を行ったシステムの出力スペクトラム 図 6.3 ミキサーの有無による出力スペクトラムの比較

### 6.2 ノイズシェーピング構成における補正結果の比較

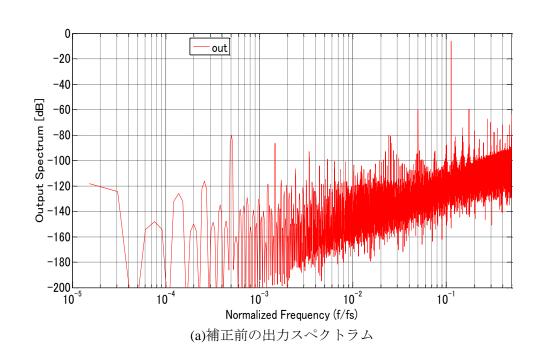

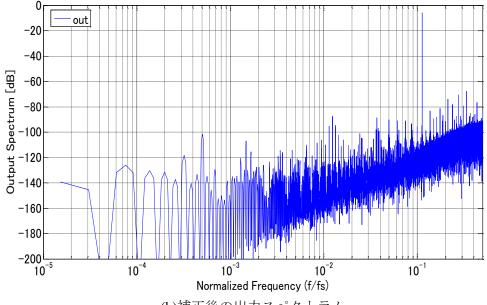

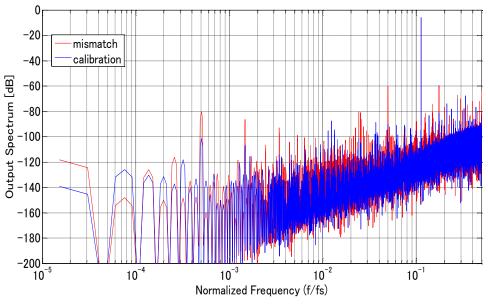

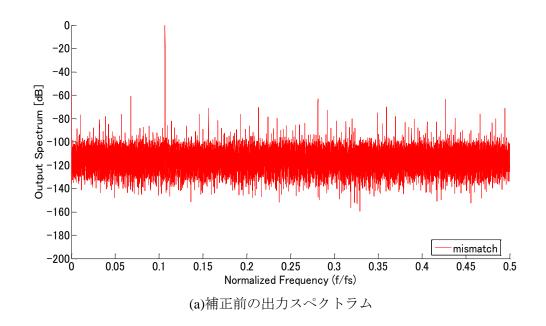

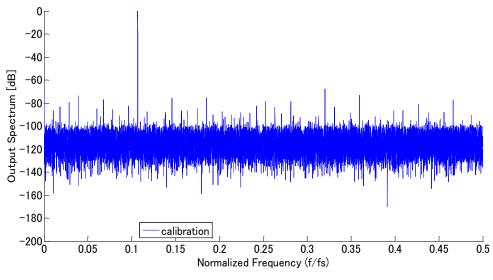

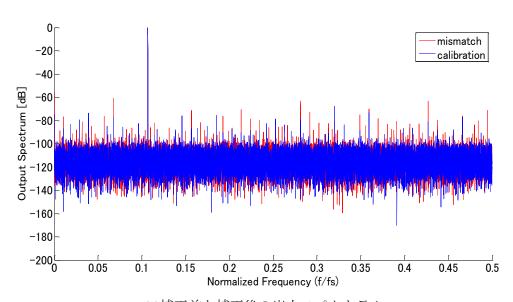

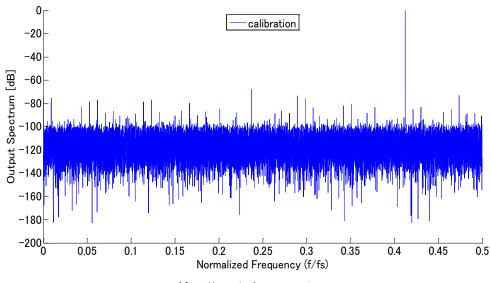

誤差検出によって得られた補正信号を使い,ノイズシェーピング構成のパイプライン型 ADC で補正効果の確認を行った.入力信号は 0.3875fs,信号帯域は 0.375fs~0.5fs,OSR は 4 とした.図 6.4(a)に補正前の出力スペクトラム,(b)に補正後の出力スペクトラム,(c)に補 正前と補正後の出力スペクトラムを示した.なお前節で説明した通り,出力スペクトラム は周波数変換後のスペクトラムを示している.

補正前は入力信号付近に-60dB の高調波があるが、補正後はこの高調波も含め全体的にレベルが下がっており、 提案手法の効果を確認することができる. また、表 6.1 に理想状態と補正前後の SNR の比較を示す. 補正後は補正前に比べ、約 18dB 改善している. 故に本手法を用いることで、パイプライン型 ADC にシェーピング特性を与え、 且つ高精度変換を実現することが可能となる.

Ideal Mismatch Calibration

SNR 79.2 54.2 72.9

表 6.1 シミュレーション結果(ノイズシェーピング構成)

(b)補正後の出力スペクトラム

(c)補正前と補正後の出力スペクトラム

図 6.4 ノイズシェーピング構成の出力スペクトラム

#### 6.3 通常構成における補正結果の比較

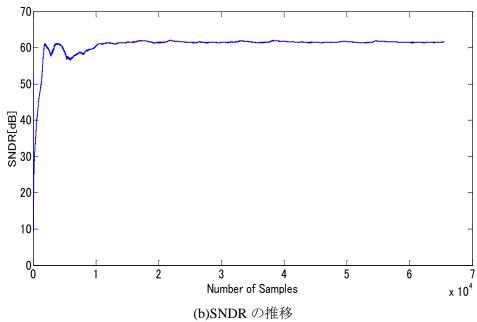

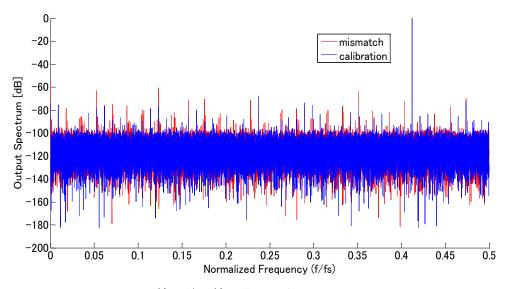

前節同様得られた補正信号を使い、通常の2段構成のパイプライン型ADCでシミュレーションを行った. 入力信号は 0.1068fs とした. 図 6.5(a)に補正前の出力スペクトラム, (b)に補正後の出力スペクトラム, (c)に補正前と補正後の出力スペクトラムを示した. 補正前のスペクトラムは全帯域に歪みがかなり発生していて、大きいもので-60dBもある. しかし補正後の出力スペクトラムは全体的に歪みが減少していて、一番大きい歪みでも-80dBである. 補正前後で比較した図から, 補正後は高調波歪が約20dB下がっている事が読み取れる.

また,表 6.2 に理想状態と補正前後の SNR, SNDR, SNDR, THD を比較したものを示す. 補正前は SNR が 53.28dB であるが,補正を行った結果 63.16dB となり,約 10dB 改善している事がわかる. その他の指標についても全て改善している.

|      | , ,     | 1 11 1/14(01-000-0) |             |

|------|---------|---------------------|-------------|

|      | Ideal   | Mismatch            | Calibration |

| SNR  | 68.02   | 53.28               | 63.16       |

| SNDR | 68.02   | 52.79               | 61.64       |

| ENOB | 11.01   | 8.48                | 9.95        |

| THD  | -106.64 | -62.49              | -66.95      |

表 6.2 シミュレーション結果(0.1068fs)

- 38 -

(b)補正後の出力スペクトラム

(c)補正前と補正後の出力スペクトラム

図 6.5 パイプライン型 ADC の出力スペクトラム(0.1068fs)

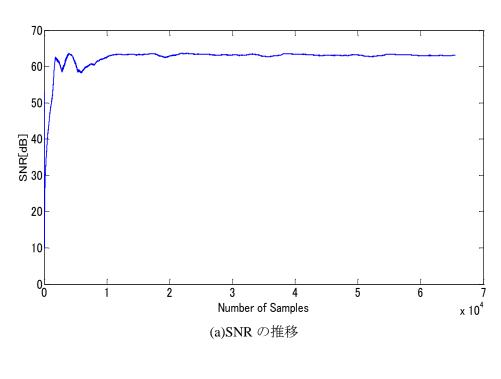

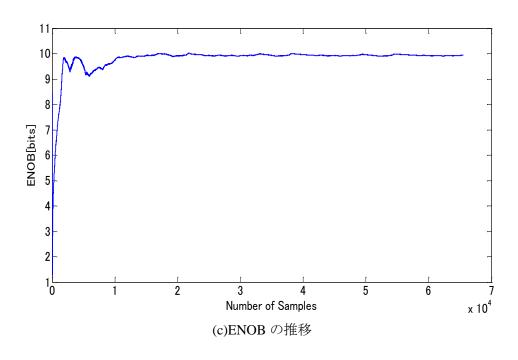

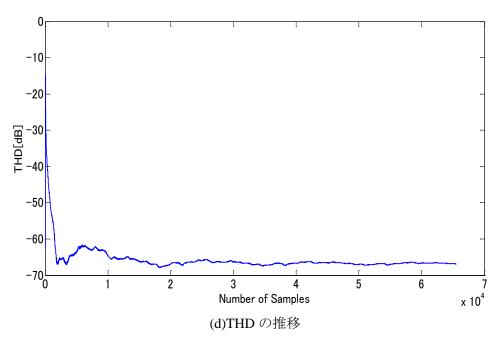

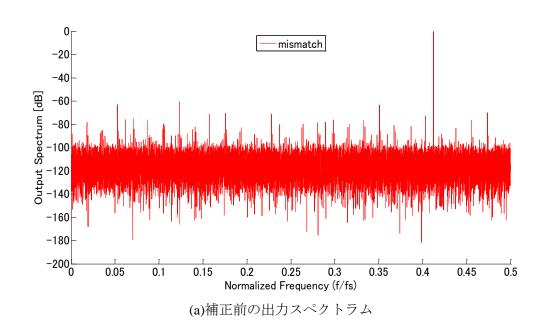

次に、誤差検出回数に対する SNR、SNDR、ENOB、THD の変化の様子を図 6.6 に示す. 誤差検出回数が  $2^{14}(16384)$ 回 $\sim 2^{15}(32768)$ 回までは、各結果は不安定である. しかし、 $2^{14}(16384)$ 回 $\sim 2^{15}(32768)$ 回を超えると、収束している様子がわかる. このことから、本提案手法では、相関演算による誤差検出を  $2^{15}$ 回繰り返す必要があると考えられる.

図 6.6 検出回数に対する各指標の変化

入力信号を高い周波数 (0.4123fs) として、同様のシミュレーションを行った。図6.7(a) に補正をする前の出力スペクトラム、(b)に補正後の出力スペクトラムを示し、(c)に補正前と補正後のスペクトラムを示した。補正前のスペクトラムは、低い周波数の時と同様に全帯域に歪みがかなり発生していて、大きいもので-60dBもある。しかし補正後の出力スペクトラムは全体的に歪みが減少している。補正前後で比較した図から、低い周波数と同様に補正後は、高調波歪が約20dB下がっている事が読み取れる。

また、SNR、SNDR、SNDR、THDを理想状態と補正前後で比較したものを表6.3に示す. 補正前はSNRが52.80 dBであるが、キャリブレーションを行った結果63.07dBとなり、低い 周波数と同様に約10dB改善している事がわかる.

低い周波数と高い周波数を入力信号としてシミュレーションを行ったが、いずれの結果 もミスマッチの影響を低減することができた.このことから、本提案手法がミスマッチの 検出に効果的であると考えられる.

|      | <b> </b> | ショッパ(0.412515) |             |

|------|----------|----------------|-------------|

|      | Ideal    | Mismatch       | Calibration |

| SNR  | 68.00    | 52.80          | 63.07       |

| SNDR | 68.00    | 52.77          | 61.65       |

| ENOB | 11.00    | 8.47           | 9.95        |

| THD  | -111.40  | -74.60         | -67.19      |

表 6.3 シミュレーション結果(0.4123fs)

- 42 -

(b)補正後の出力スペクトラム

(c)補正前と補正後の出力スペクトラム パイプライン型 ADC の出力スペクトラム(0.4123fs)

## 第7章 まとめと今後の課題

本論文では、"ノイズシェーピング構成"と"NSDEM"を用いて、キャパシタミスマッチを高い精度で検出して補正する方法を提案した。

MATLAB/Simulink によるシミュレーションの結果,提案手法の有効性を確認する事ができた.提案回路では,量子化雑音の影響を受けずバックグラウンドでミスマッチを高精度に検出する事が可能である.これにより,キャパシタミスマッチに対して影響を受けないパイプライン型 ADC を構成できる事を明らかにした.

MATLAB レベルでの今後の課題として、さらなる誤差検出精度向上が考えられる.シミュレーション結果より、ミスマッチの影響から Effective Number Of Bit(ENOB)を約 10bits へ改善することができた.しかし理想状態では 11bits であるため、まだ誤差検出精度が低いと考えられる. そのため、フィルタで除外した部分に対する補正式の再検証が必要である.

回路レベルの課題としては、Cadence/SpectreVerilog、Synopsys によるトランジスタレベルで回路設計をする必要がある。また、回路を IC に実装後、測定結果とシミュレーション結果を比較する事で、本提案手法の実用性を確認する必要がある。

## 謝辞

本研究を遂行するにあたり、懇切なるご指導を頂きました安田彰教授に深く感謝いたします.また、半導体システム工学研究室の皆様にも数々のご協力、助言を頂き、本稿が作成出来た事にも感謝申し上げます.

### 参考文献

- (1) A. Karanicolas, H. Lee, and K. Bacrania, "A 15-b 1-Msample/s DigitallySelf-Calibrated Pipeline ADC", IEEE J. Solid-State Circuits, Vol. 28, No. 12, pp. 1207-15, Dec. 1993.

- (2) J. Ming and S. H. Lewis, "An 8 b 80 MSample/s pipelined ADC with background calibration", in IEEE ISSCC Dig. Tech. Papers, pp. 42-43, Feb. 2000.

- (3) A. Panigada, I. Galton, "A 130 mW 100 MS/s Pipelined ADC with 69 dB SNDR Enabled by Digital Harmonic Distortion Correction", IEEE Journal of Solid-State Circuits, vol. 44, no. 12, pp. 3314-3328, Dec. 2009.

- (4) L. Li, X. Huang, Z. Yu, M. Xu, C. Zhu, Y. Han, "A 12-Bit 125MSPS ADC with capacitor mismatch trimming", 2010 10<sup>th</sup> IEEE International Conference Solid-State and Integrated Circuit Technology (ICSICT), Shanghai, China, pp. 216-218, Nov. 2010.

- (5) Y. Serizawa, A. Yasuda, J. Tayama, "A New Background Calibration Method Using Noise Shaping for Precise Mismatch Detection of a Pipeline", IEEJ AVLSI2006, ADCI, No. 2, pp1-5, Nov. 2006.

- (6) 安田 彰, 和保 孝夫 監訳, "ΔΣ型アナログ/ディジタル変換器入門" 丸善出版.

- (7) Y-H. Chang, C-Y. Wu, T-C. Yu "Chopper-stabilized Sigma-Delta Modulator", In Proc. ISCAS, Vol.2, pp. 1286-1289, May 1993.

- (8) A. Yasuda, H. Tanimoto, T. Iida, "A Third-order ΔΣ modulator using second-order noise-shaping dynamic element matching", IEEE J. Solid-State Circuits, Vol.33, pp. 1879-1886, Dec. 1998.

- (9) T. Shui, R. Screier, F. Hudson, "Mismatch shaping for a current-mode multibit delta-sigma DAC", IEEE Journal of Solid-State Circuits, vol.34, pp. 331-338, Mar. 1999.

- (10) H. San, H. Kobayashi, S. Kawakami, N. Kuroiwa, "An element rotation algorithm for multi-bit DAC nonlinearities in complex bandpass delta-sigma AD modulators", IEEE 17<sup>th</sup> International Conference on VLSI Design, Mumbai, India, pp. 151-156, Jan. 2004.

- (11) 宮崎 勝毅, 二岡 祐一, 安田 彰, "ミスマッチシェーパーを用いた自己補正型パイプラインADC,"電子回路研究会, ECT-09-004, pp. 17-20, 2009年1月.

- (12) Z. Chen, et al., "Noise Shaping Implementation inTwo-Step/SAR ADC Architectures Based on Delayed Quantization Error", 2011 IEEE 54<sup>th</sup> International Midwest Symposium on Circuits and Systems (MWSCAS 2011), pp. 1-4, Aug. 2011.

- (13) V. T. Nguyen, P. Desgreys, P. Loumeau, J. F. Naviner, "Noise Analysis in High-Pass  $\Delta\Sigma$  Modulator", 2006. IMTC 2006. Proceeding of the IEEE, Instrumentation and Measurement Technology Conference, pp. 255-260, Apr. 2006.

# 発表論文

- (1) 二岡 祐一, 小松 直樹, 高橋 翔太郎, 安田 彰, " $\Delta\Sigma$ 変調器とハイパスミスマッチシェーパーを用いた自己校正型パイプラインADC", 電子回路研究会, ECT-10-005, 2010年1月.

- (2) N. Komatsu, A. Yasuda, S. Takahashi, K. Yamaguchi "A Pipelined ADC Using a Background Calibration with a High-Pass Mismatch Shaper and Delta-Sigma Modulation", Proceedings of The 2010 IEEJ Analog VLSI Workshop, No. 1, pp. 81-86, Pavia, Italy, Sep. 2010.

- (3) 山口 圭, 横田 和幸, 小松 直樹, 安田 彰, 森山 誠二郎, "Webツールを用いた アナログ回路設計の検討,"電子回路研究会, ECT-10-096, 2010年10月.