# 法政大学学術機関リポジトリ

## HOSEI UNIVERSITY REPOSITORY

PDF issue: 2025-12-13

### ファジィフリップフロップを用いたファジィ レジスタ

NANBA, Masaaki / HIROTA, Kaoru / 難波, 雅明 / 小沢, 和浩

/ OZAWA, Kazuhiro / 廣田, 薫

---

(出版者 / Publisher)

法政大学工学部

(雑誌名 / Journal or Publication Title)

Bulletin of the Faculty of Engineering, Hosei University / 法政大学工学部

研究集報

(巻 / Volume)

26

(開始ページ / Start Page)

111

(終了ページ / End Page)

124

(発行年 / Year)

1990-02

(URL)

<https://doi.org/10.15002/00003921>

# ファジィフリップフロップを用いたファジィレジスタ

小沢和浩\*・廣田薰\*\*・難波雅明\*\*\*

## Fuzzy Register Based on Fuzzy Flip-Flop

Kazuhiro OZAWA\*, Kaoru HIROTA\*\* and Masaaki NANBA\*\*\*

### Abstract

Concept of fuzzy flip-flop has been proposed based on 2 valued J-K flip-flop which is a fundamental element of ordinary computer memory module. By using the same number of fuzzy flip-flop's as the cardinal of the universe of discourse, a notion of fuzzy register has been proposed. It is able to memorize any shaped membership function, to output a complement function and to operate a various kind of compositional rule of fuzzy inference. A notion of fuzzy shift register is also proposed, where the right/left shift operation of the membership function is possible on the universe of discourse. Moreover the fuzzy register circuit is designed and is realized by using ordinary ROM's.

### §1. はじめに

ファジィ情報の高速処理を目的としたファジィコンピュータの実現に向けて、各種ファジィ演算を直接ハードウェアレベルで実行する推論マシン<sup>1-4)</sup>やファジィ推論ハードウェアの開発環境<sup>4)</sup>が発表されている。また、ファジィ情報の記憶素子に関する研究も行われている。メンバーシップ関数を記憶するデバイスとしては山川、佐々木らのファジィメモリデバイス<sup>5)</sup>があり、これはファジィプロダクションルールで用いられる有限個の（文献5の場合は8個の）メンバーシップ関数（ファジィワード）の記憶が可能である。

著者らは、現在の電子計算機の記憶素子の基本単位である J-K フリップフロップをファジィ否定、 $t$ ノルム、 $s$ ノルムを用いてファジィ拡張を行いファジィフリップフロップとしての定義を行った<sup>6)</sup>。このファジィフリップフロップの入出力特性に関しては、min、max 演算を用いた min max 型ファジィフリップフロップ、代数積、代数和演算を用いた、代数積代数和型のファジィフリップフロップ、限界積、限界和の演算を用いた限界積限界和型ファジィフリップフロッ

\* 法政大学大学院工学研究科電気工学専攻

\*\* 法政大学工学部電気工学科計測制御専攻

\*\*\* 日本アイ・ピー・エム株式会社

ブ, 激烈積, 激烈和演算を用いた激烈積激烈和型ファジィフリップフロップの四つについてすでに明らかにしている<sup>6~7)</sup>。さらに, 以上の各種ファジィ演算系で定義されたファジィフィリップフロップの内で実用上最も有用と思われる, min max 型ファジィフリップフロップと代数積代数和型ファジィフリップフロップに関しては, 離散近似型と連続電圧値モードによる回路化をすでに終えている<sup>8~11)</sup>。

本論文ではこのファジィフリップフロップを基にして, 任意形状のメンバーシップ関数が記憶可能でかつその反転出力や各種のファジィ演算が可能なファジィレジスタの提案を行う。このファジィレジスタを用いると代表的なファジィ推論で用いられている max-min 合成や, max-代数積合成, max-限界積合成が可能となる。また, 記憶したメンバーシップ関数が台集合上で左右にシフト可能なファジィシフトレジスタの提案も行う。最後にファジィレジスタを市販の汎用メモリ素子を用いて試作設計し, 動作確認をした。

## §2. ファジィレジスタの定義

ファジィフリップフロップは, 二値 J-K フリップフロップの特性をすべて包含してファジィ拡張されているため, 任意のファジィ値(1エレメント)の記憶, 反転出力(ファジィ否定), これにファジィフリップフロップ特有の諸機能を持つ。以下に後の議論で必要なため min max 型(式(2-1))<sup>6,7)</sup>, 代数積代数和型(式(2-2))<sup>10)</sup>, 限界積限界和型(リセット型, 式(2-3), セット型, 式(2-4))<sup>6,7)</sup> ファジィフリップフロップの定義式を示す。

$$Q(t+1) = [J(t) \vee \{1-K(t)\}] \wedge [J(t) \vee Q(t)] \wedge [\{1-K(t)\} \vee \{1-Q(t)\}] \quad (2-1)$$

$$Q(t+1) = J(t) + Q(t) - \{J(t) + K(t)\} Q(t) \quad (2-2)$$

$$Q(t+1) = 1 \wedge [0 \vee \{J(t) - Q(t)\} + 0 \vee \{Q(t) - K(t)\}] \quad (2-3)$$

$$Q(t+1) = 0 \vee [1 \wedge \{J(t) + Q(t)\} + 1 \wedge \{2 - K(t) - Q(t)\} - 1] \quad (2-4)$$

以上の四つのファジィフリップフロップの諸機能を用いて任意形状のメンバーシップ関数の記憶モジュールの実現が可能である。この記憶モジュールを以下ではファジィレジスタと呼ぶことにする。ファジィフリップフロップが二値 J-K フリップフロップのファジィ拡張となっていることから, 当然, ここで定義したファジィレジスタは二値のレジスタのファジィ拡張となっている。つまり, ファジィレジスタはメンバーシップ関数のメモリモジュールとなっていることが分かる。限界積限界和型ファジィフリップフロップでリセット型(式(2-3)), セット型(式(2-4))の両方を独立に扱った理由としては, リセット型, セット型がそれぞれ二値 J-K フリップフロップの持つ四つの基本特性(記憶, リセット, セット, 反転出力)のすべてを満たしてファジィへの拡張がなされていること<sup>9)</sup>に起因している。また, 限界積限界和型ファジィフリップフロップのリセット型, セット型の統一も可能であるがその入出力特性が min max 型や代数積代数和型に比べ複雑であり, 本論文で提案するファジィレジスタの様々な機能を実現するには限界積限

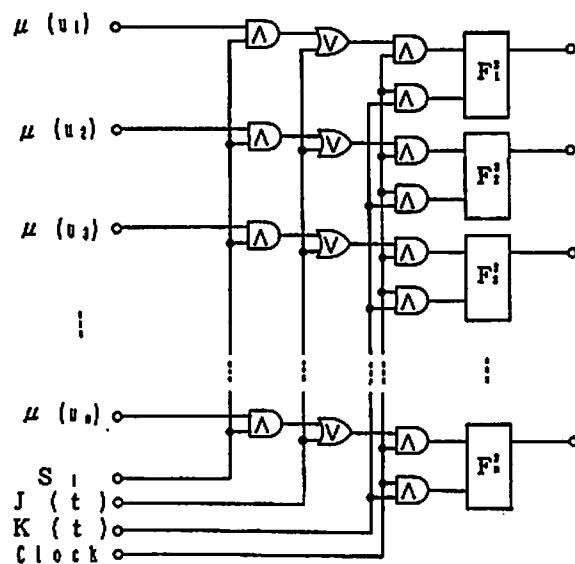

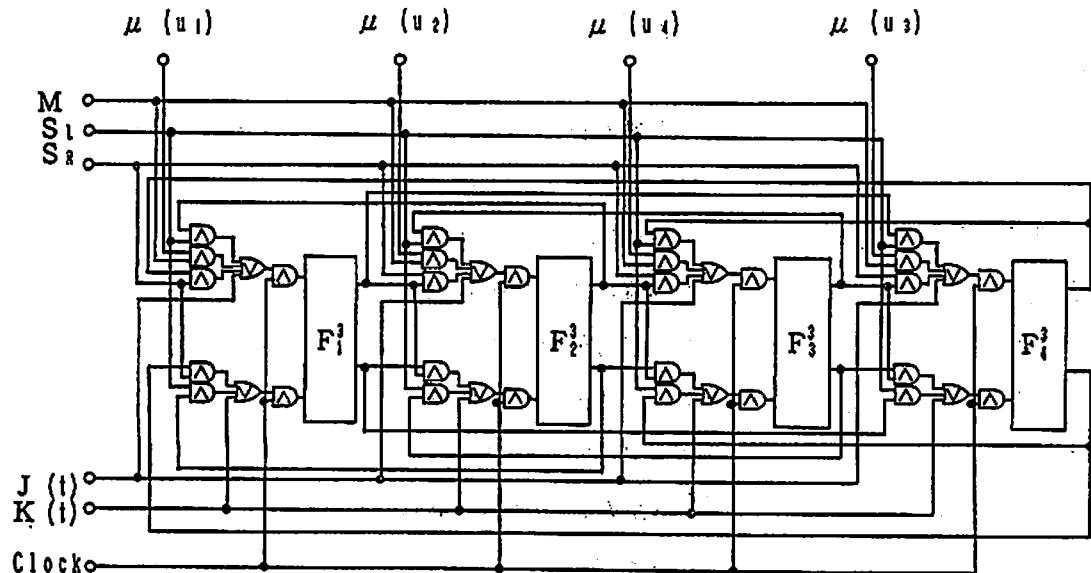

Fig. 2.1 ファジィレジスタ

界和型の統一式を用いる必要はない。そこで、本論文では以上の四つのファジィフリップフロップを基本に用いたファジィレジスタの諸機能について議論する。ファジィレジスタは Fig. 2.1 に示すようにファジィフリップフロップを  $n$  個（台集合のカージナル数）を用いて任意形状のメンバーシップ関数の記憶、反転出力、ファジィ合成を可能にしている。ここで、 $S_1$  はメンバーシップ関数をファジィレジスタにセットするための制御信号である。このファジィレジスタ回路に数個のファジィゲート素子を加えると台集合上のメンバーシップ関数の左右シフト動作が可能なファジィシフトレジスタが構成可能となる。

### § 3. ファジィレジスタの機能

#### 3.1 任意形状のメンバーシップ関数のセット

ファジィレジスタを用いると任意形状のメンバーシップ関数のセットが可能である。これは、メンバーシップ関数を記述する台集合のカージナル数 ( $n$  個) だけ配置したすべてのファジィフリップフロップをリセット後 ( $J_i(t)=0, K_i(t)=1$  を入力)、 $J_i(t)$  入力端子に任意のファジィ値を入力し、 $K_i(t)$  入力端子に 0 を並列的に入力することにより実現される。つまり、ファジィフリップフロップのセット機能を用いる。以下に min max 型ファジィレジスタと代数積代数和型ファジィレジスタについて解析を行う。ここで、添字  $i$  は台集合上の  $i$  番目のファジィフリップフロップを示す ( $1 \leq i \leq n$ )。

$a_i$  を任意のファジィ値とし、

$J_i(t)=a_i, K_i(t)=0, Q_i(t)=0$  とすると、

1) min max 型

$$\begin{aligned}

Q_i(t+1) &= (a_i \vee 1) \wedge (a_i \vee 0) \wedge (1 \vee 1) \\

&= 1 \wedge a_i \wedge 1 \\

&= a_i

\end{aligned} \tag{3-1}$$

## 2) 代数積代数和型

$$\begin{aligned}

Q_i(t+1) &= a_i + 0 - (a_i + 0) \cdot 0 \\

&= a_i

\end{aligned} \tag{3-2}$$

## 3) 限界積限界和型(リセット型)

$$\begin{aligned}

Q_i(t+1) &= 1 \wedge \{0 \vee (a_i - 0) + 0 \vee (0 - 0)\} \\

&= 1 \wedge a_i \\

&= a_i

\end{aligned} \tag{3-3}$$

## 4) 限界積限界和型(セット型)

$$\begin{aligned}

Q_i(t+1) &= 0 \vee \{1 \wedge (a_i + 0) + 1 \wedge (2 - 0 - 0) - 1\} \\

&= 0 \vee (a_i + 1 - 1) \\

&= 0 \vee a_i \\

&= a_i

\end{aligned} \tag{3-4}$$

となる。

以上で任意のファジィ値が全ての場合にセットされることになる。つまり、ファジィレジスタ全体として任意形状のメンバーシップ関数のセットが可能である。

## 3.2 メンバーシップ関数の反転(否定)出力

ファジィレジスタに一度セットされた任意形状のメンバーシップ関数の反転(否定)出力も可能である。これはファジィレジスタの基本セルとなるファジィフリップフロップにセットされた任意のファジィ値の反転出力をとればよい。つまり、 $J_i(t)$  入力端子、 $K_i(t)$  入力端子共に1を入力すれば良いことになる。この動作を以下に解析的に述べることにする。

$J_i(t) = 1, K_i(t) = 1, Q_i(t) = a_i$  とすると、

1) min max型

$$\begin{aligned}

Q_i(t+1) &= (1 \vee 0) \wedge (1 \vee a_i) \wedge \{0 \vee (1 - a_i)\} \\

&= 1 \wedge 1 \wedge (1 - a_i) \\

&= 1 - a_i

\end{aligned} \tag{3-5}$$

## 2) 代数積代数和型

$$\begin{aligned}

Q_i(t+1) &= 1 + a_i - 2a_i \\

&= 1 - a_i

\end{aligned} \tag{3-6}$$

## 3) 限界積限界和型(リセット型)

$$Q_i(t+1) = 1 \wedge \{0 \vee (1 - a_i) + 0 \vee (a_i - 1)\}$$

$$\begin{aligned}

&= 1 \wedge (1 - a_i) \\

&= 1 - a_i

\end{aligned} \tag{3-7}$$

## 4) 限界積限界和型（セット型）

$$\begin{aligned}

Q_i(t+1) &= 0 \vee \{1 \wedge ((1 + a_i) + 1 \wedge (2 - 1 - a_i) - 1\} \\

&= 0 \vee \{1 + 1 \wedge (1 - a_i) - 1\} \\

&= 0 \vee (1 - a_i) \\

&= 1 - a_i

\end{aligned} \tag{3-8}$$

となる。

以上ですべての場合に任意のファジィ値  $a_i$  の反転出力  $1 - a_i$  が得られる。つまり、ファジィレジスタ全体としては任意形状のメンバーシップ関数の反転(否定)出力が得られることになる。

## § 4. ファジィレジスタを用いた各種ファジィ合成

### 4.1 ファジィレジスタによる max-min 合成

ファジィ推論で最も多く用いられている方法に max-min 合成がある。これは、ファジィプロダクションルールの前件部命題に記述されたメンバーシップ関数と入力情報との min 演算を行い、照合度を求め、その照合度の値と後件部のメンバーシップ関数との min 演算を行い、得られた後件部メンバーシップ関数の max 統合を全てのルールについて行い、最終的に得られたメンバーシップ関数の非ファジィ化の後出力値を求める方法である。ここで提案するファジィレジスタは、この max-min 合成にも用いることができる。

後件部メンバーシップ関数がファジィレジスタにすでにセットされているものとし、ファジィプロダクションルールに記述されている前件部メンバーシップ関数と入力情報との min 演算を行った結果の照合度を  $\alpha$  とする。ファジィレジスタの基本セルであるファジィフリップフロップの  $J_i(t)$ ,  $K_i(t)$  入力端子にそれぞれ 0,  $1 - \alpha$  を入力することにより後件部メンバーシップ関数との min 演算が可能となる。これはファジィフリップフロップのリセット機能を利用したものである。以下に、解析的に計算を行った結果を示す。

$J_i(t) = 0, K_i(t) = 1 - \alpha, Q_i(t)$  を既に記憶されているメンバーシップ値とすると、min max 型ファジィフリップフロップの定義式より、

$$\begin{aligned}

Q_i(t+1) &= \alpha \wedge Q_i(t) \wedge [\alpha \vee \{1 - Q_i(t)\}] \\

&= Q_i(t) \wedge [(\alpha \wedge \alpha) \vee (\alpha \wedge \{1 - Q_i(t)\})] \\

&= Q_i(t) \wedge [\alpha \vee \{\alpha \wedge 1 - Q_i(t)\}] \\

&= \{Q_i(t) \wedge \alpha\} \vee [Q_i(t) \wedge \{\alpha \wedge (1 - Q_i(t))\}] \\

&= \{Q_i(t) \wedge \alpha\} \vee [\{Q_i(t) \wedge \alpha\} \wedge \{Q_i(t) \wedge (1 - Q_i(t))\}] \\

&= Q_i(t) \wedge \alpha

\end{aligned} \tag{4-1}$$

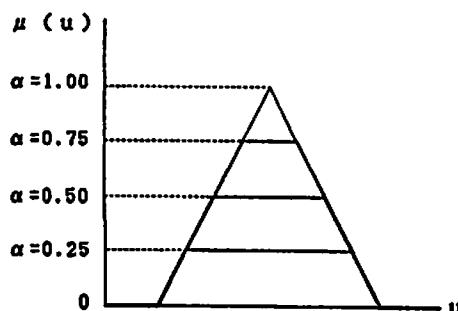

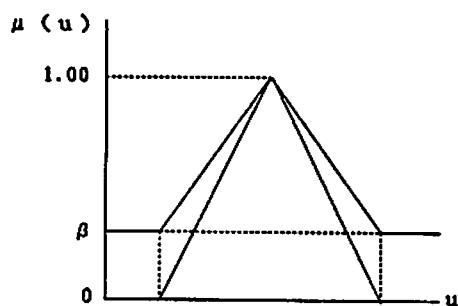

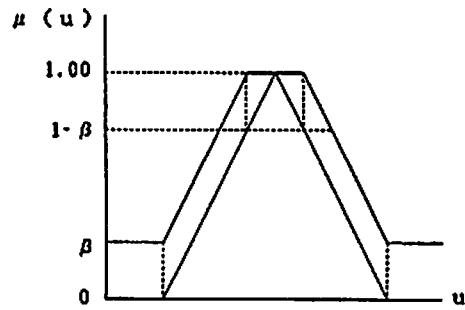

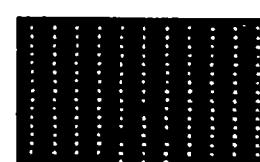

となって、 $\min$  演算が実行されることになる。任意形状としてベル形のメンバーシップ関数をとった場合についての一例を Fig. 4.1 に示す。

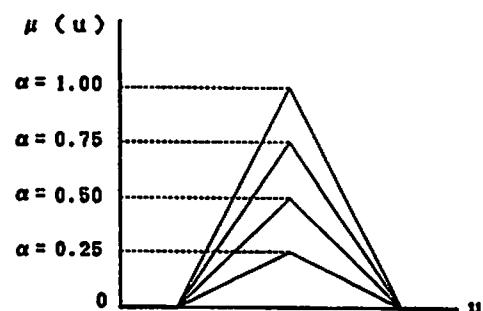

#### 4.2 ファジィレジスタによる max-代数積合成

ファジィレジスタの基本セルであるファジィフリップフロップに代数積代数和型を用いると、max-代数積合成で用いられるメンバーシップ関数の代数積的な縮小が可能である。ここでも、4-1. と同様、ファジィフリップフロップのリセット機能を用いることとする。以下に計算結果を示す。

$J_i(t) = 0, K_i(t) = 1 - \alpha, Q_i(t)$  を既に記憶されているメンバーシップ値とすると、代数積代数和型ファジィフリップフロップの定義式より、

$$\begin{aligned} Q_i(t+1) &= Q_i(t) - (1 - \alpha) Q_i(t) \\ &= Q_i(t) - Q_i(t) + \alpha Q_i(t) \\ &= \alpha Q_i(t) \end{aligned} \quad (4-2)$$

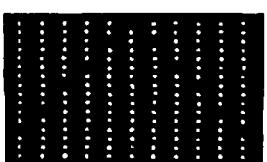

となり、簡単に示すことができる。ここでも、任意形状としてベル形のメンバーシップ関数をとった場合についての計算結果を Fig. 4.2 に示す。

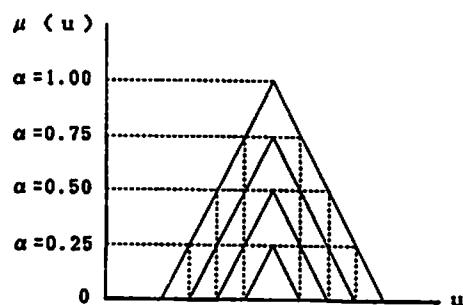

#### 4.3 ファジィレジスタによる max-限界積合成

ここでは、ファジィフリップフロップとして限界積限界和型（リセット型）を用いるとメンバーシップ関数の限界積縮小が可能となる。ここでも、ファジィレジスタに任意形状のメンバーシップ関数がすでに記憶されているものとして、議論を進める。

Fig. 4.1 ファジィレジスタによる max-min 合成

Fig. 4.2 ファジィレジスタによる max-代数積合成

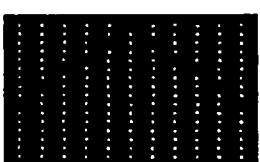

Fig. 4.3 ファジィレジスタによる max-限界積合成

$J_i(t)=0, K_i(t)=1-\alpha, Q_i(t)$  をすでに記憶されているメンバーシップ値とすると、限界積限界和型（リセット型）ファジィフリップフロップの定義式より、

$$\begin{aligned} Q_i(t+1) &= 1 \wedge [0 \vee \{-Q_i(t)\} + 0 \vee \{Q_i(t) - (1-\alpha)\}] \\ &= 1 \wedge [0 \vee \{Q_i(t) - (1-\alpha)\}] \end{aligned}$$

1)  $Q_i(t) \leq 1-\alpha$  のとき、

$$Q_i(t+1) = 0$$

2)  $Q_i(t) > 1-\alpha$  のとき

$$Q_i(t+1) = 0 \vee \{Q_i(t) - (1-\alpha)\} \quad (4-3)$$

この計算結果を Fig. 4.3 に示す。

## § 5. その他の機能

ファジィレジスタには § 4. で述べた機能の他に代数積代数和型、限界積限界和型（セット型）のファジィフリップフロップのセット機能を用いるとファジィプロダクションルールの前件部変数の重みを軽くすることが可能である。

### 5.1 代数積代数和型ファジィレジスタのセット機能

代数積代数和型ファジィフリップフロップのセット機能を用い、ファジィプロダクションルールの前件部変数の重みを軽くするには、各ファジィフリップフロップの  $J_i(t)$  入力端子に重みの度合  $\beta$  を、 $K_i(t)$  入力端子に 0 を入力することにより実現される。

$J_i(t)=\beta, K_i(t)=0, Q_i(t)$  を既に記憶されている任意のファジィ値として、代数積代数和型ファジィフリップフロップの定義式より、

$$\begin{aligned} Q_i(t+1) &= \beta + Q_i(t) - \beta Q_i(t) \\ &= \beta + (1-\beta)Q_i(t) \end{aligned} \quad (5-1)$$

となる。

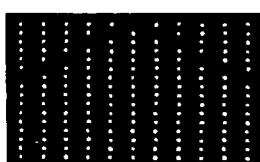

ここでも、ベル形のメンバーシップ関数を例にとった場合についての計算結果を Fig. 5.1 に示す。

### 5.2 限界積限界和型（セット型）ファジィレジスタのセット機能

代数積代数和型ファジィレジスタと同様に限界積限界和型（セット型）ファジィレジスタを用いても前件部変数の重みを軽くすることが可能である。

$J_i(t)=\beta, K_i(t)=0, Q_i(t)$  をすでに記憶されている任意のファジィ値とすると、限界積限界和型（セット型）ファジィフリップフロップの定義式より、

$$\begin{aligned} Q_i(t+1) &= 0 \vee [1 \wedge \{\beta + Q_i(t)\} + 1 \wedge \{2 - Q_i(t)\} - 1] \\ &= 0 \vee [1 \wedge \{\beta + Q_i(t)\}] \\ &= 1 \wedge \{\beta + Q_i(t)\} \end{aligned} \quad (5-2)$$

Fig. 5.1 代数積代数和型ファジィレジスタのセット機能

Fig. 5.2 セット型限界積限界和型ファジィレジスタのセット機能

となる。

以上の計算結果を Fig. 5.2 に示す。

## § 6. ファジィシフトレジスタの構成

ここでは、§2.で提案したファジィレジスタに左右のシフト機能も組み込んだファジィシフトレジスタの回路構成について提案を行う。このファジィシフトレジスタを用いると記憶したファジィプロダクションルールのメンバーシップ関数のラベルやグレードの変更が可能となる。回路構成を Fig. 6.1 に、回路のファンクションテーブルを Table 6.1 に示す。ここで、 $S_L, S_R$  はそれぞれ台集合上のメンバーシップ関数の左シフトと右シフト動作を制御するための信号入力端子である。また、Table 6.1 の Reset, Set の欄の「\*」は Don't Care を意味している。以下に、台集合上の  $i-1$  番目のファジィフリップフロップに記憶されている内容を  $i$  番目のファジィフリップフロップへの右シフトが可能なことを示す。

$J_i(t) = Q_{i-1}(t), K_i(t) = 1 - Q_{i-1}(t)$  とする。

Fig. 6.1 ファジィシフトレジスタ

Table 6.1 ファジィシフトレジスタのファンクションテーブル

|                | Im1 | Im2 | St | Im3 | Diff1 | Diff2 |

|----------------|-----|-----|----|-----|-------|-------|

| M              | 1   | 0   | 0  | 0   | 0     | 0     |

| S <sub>1</sub> | 0   | 0   | 0  | 0   | 1     | 0     |

| S <sub>2</sub> | 0   | 0   | 0  | 0   | 0     | 1     |

| J(t)           | 0   | 0   | *  | 1   | 0     | 0     |

| K(t)           | 0   | *   | 0  | 1   | 0     | 0     |

## 1) min max 型ファジィシフトレジスタ

min max 型ファジィフリップフロップの定義式より,

$$\begin{aligned}

Q_i(t+1) &= [Q_{i-1}(t) \vee \{1 - (1 - Q_{i-1}(t))\}] \wedge \{Q_{i-1}(t) \vee Q_i(t)\} \\

&\quad \wedge [\{1 - (1 - Q_{i-1}(t))\} \vee \{1 - Q_i(t)\}] \\

&= \{Q_{i-1}(t) \vee Q_{i-1}(t)\} \wedge \{Q_{i-1}(t) \vee Q_i(t)\} \wedge [Q_{i-1}(t) \vee \{1 - Q_i(t)\}] \\

&= Q_{i-1}(t) \wedge \{Q_{i-1}(t) \vee Q_i(t)\} \wedge [Q_{i-1}(t) \vee \{1 - Q_i(t)\}] \\

&= Q_{i-1}(t) \wedge [Q_{i-1}(t) \vee \{1 - Q_i(t)\}] \\

&= Q_{i-1}(t)

\end{aligned} \tag{6-1}$$

となり右シフト動作が確認される。

## 2) 代数積代数和型ファジィシフトレジスタ

代数積代数和型ファジィフリップフロップの定義式より,

$$\begin{aligned}

Q_i(t+1) &= Q_{i-1}(t) + Q_i(t) - [Q_{i-1}(t) + \{1 - Q_{i-1}(t)\}] Q_i(t) \\

&= Q_{i-1}(t) + Q_i(t) - Q_{i-1}(t) Q_i(t) - \{1 - Q_{i-1}(t)\} Q_i(t) \\

&= Q_{i-1}(t) + \{1 - Q_{i-1}(t)\} Q_i(t) - \{1 - Q_{i-1}(t)\} Q_i(t) \\

&= Q_{i-1}(t)

\end{aligned} \tag{6-2}$$

となって、ここでも右シフト動作が確認できた。

同様にして、左シフト動作も確認できるが、ここでは説明を省略する。

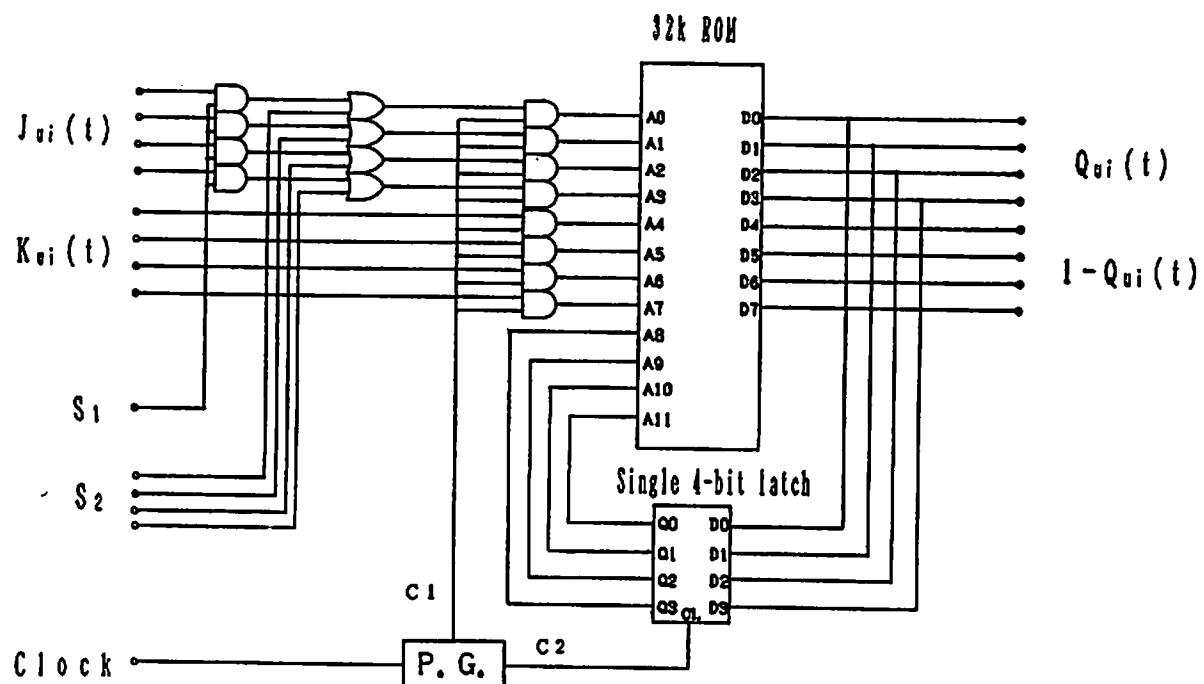

## § 7. ファジィレジスタの基本セル

ファジィレジスタの基本セルであるファジィフリップフロップの回路図 Fig. 7.1 をに示す。ここで  $J_{ui}(t)$ ,  $K_{ui}(t)$ ,  $S_2$ ,  $Q_{ui}(t)$ ,  $1 - Q_{ui}(t)$  の入出力信号は  $[0, 1]$  のファジィ値を 4 bit つまり  $\{0000, 0001, \dots, 1111\}$  の16値に離散近似表現している。

ファジィレジスタの基本セルとなるファジィフリップフロップは回路構成を簡素にするため32 Kbit EP ROM を基本として用いた。ここで ROM の内容には min max 型、代数積代数和型、限界積限界和型（リセット型とセット型の2つ）のファジィフリップフロップのすべての入出力状態の計算結果が各種ファジィフリップフロップの定義式に従って納められている。ROM のアドレスは上位から 4 bit ずつ  $J_{ui}(t)$ ,  $K_{ui}(t)$ ,  $Q_{ui}(t)$  を示し、またデータは上位から 4 bit ずつそれぞれ  $Q_{ui}(t)$ ,  $1 - Q_{ui}(t)$  の順で配置している。

本研究で構築した各種ファジィフリップフロップ回路のファンクションテーブルを Table 7.1 に示す。各種ファジィフリップフロップの機能である記憶, リセット, セット, 反転出力が実現可能である。

4 bit の D-Type Flip-Flop はファジィフリップフロップの出力信号  $Q_{ui}(t-1)$  を入力信号  $Q_{ui}(t)$  として遅延するための素子として用いた。また前段の 2 input AND Gate 4 個と 2 input OR Gate 4 個は任意形状のメンバーシップ関数の記憶, 反転出力, 各種ファジィ合成などの各種ファジィフリップフロップの持つ諸機能を実現するための入力信号制御ゲート素子である。残りの 8 個の 2 input AND Gate は, クロック同期用のゲート素子である。つまり基本的には ROM と D ラッチとクロック同期用のゲート素子で順序回路としてのファジィフリップフロップを構築した。

Fig. 7.1 ファジィレジスタの基本セル

Table 7.1 ファジィレジスタのファンクションテーブル

|        | Memory | Reset | Set  | Inverse |

|--------|--------|-------|------|---------|

| $S_1$  | $H$    | $L$   | $L$  | $L$     |

| $S_2$  | 0000   | 0000  | 1111 | 1111    |

| $K(t)$ | 0000   | 1111  | 0000 | 1111    |

### §8. ファジィレジスタの設計

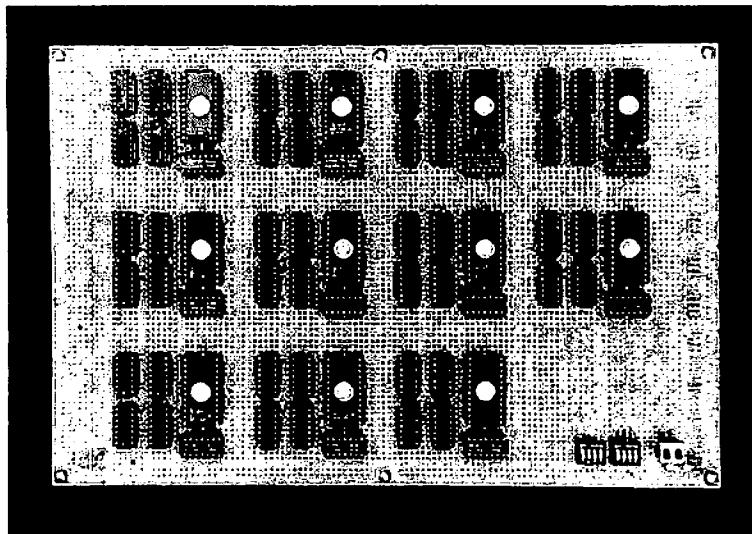

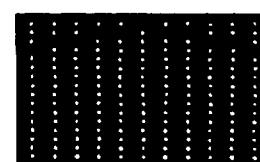

§7.で述べたファジィフリップフロップ回路を基にファジィレジスタ回路の設計を行う。今回試作したファジィレジスタ回路を Photo 8.1 に示す。

メンバーシップ関数を記述する台集合上のカージナル数は理論的には何点でもとれるが、ここでは11点とした。つまりファジィフリップフロップを11個並列的に配置し、ファジィレジスタを構成した。

付属回路についてはファジィレジスタ入力部とファジィレジスタ出力部とパルスジェネレータを含むファジィレジスタ制御部とする。

ファジィレジスタ入力部は4 bit つまり16値で離散近似表現したファジィ情報  $J_{ui}(t)$  を入力するもので4 bit スイッチ11個で構成した。ファジィレジスタ出力部は4 bit つまり16値で離散近似表現したファジィ情報  $Q_{ui}(t)$  を出力するもので、4 bit データを 4 to 16 Line Decoder によってメンバーシップ関数を  $11 * 16$  個の LED ディスプレイで視覚化した。

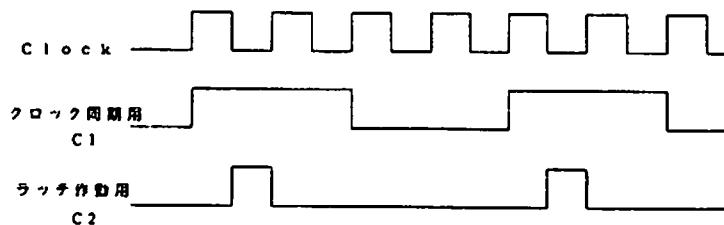

ファジィレジスタ制御部は  $S_1$ ,  $S_2$ ,  $K_{ui}(t)$ , Clock を入力するものでそれぞれスイッチで構成した。制御信号  $S_1$ ,  $S_2$ ,  $K_{ui}(t)$  によって各種ファジィフリップフロップの定義から Table 7.1 と同様にして任意形状のメンバーシップ関数の記憶、リセット、セット、反転出力が可能である。パルスジェネレータ(P.G.) は外部から与えるクロックパルスをクロック同期用パルス  $C_1$  と D ラッチ

Photo. 8.1 ファジィレジスタ回路

Fig. 8.1 ファジィレジスタのタイムチャート

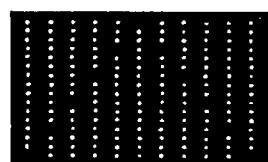

Photo. 9.1 ファジィレジスタの

セット機能

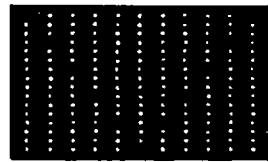

Photo. 9.2 ファジィレジスタの

反転出力機能

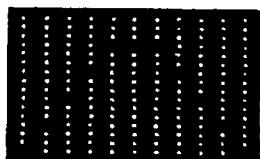

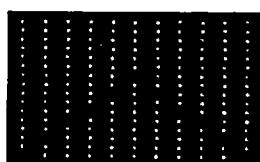

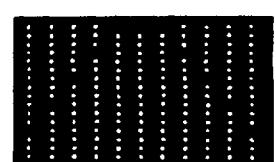

Photo. 9.3.1  $\alpha=0.8$ の場合

Photo. 9.3.2  $\alpha=0.6$ の場合

Photo. 9.3.3  $\alpha=0.4$ の場合

Photo. 9.3.4  $\alpha=0.2$ の場合

Photo. 9.3 min-max 型ファジィレジスタを用いた max-min 合成

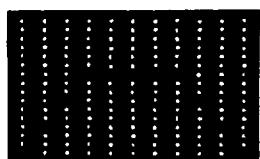

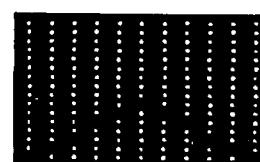

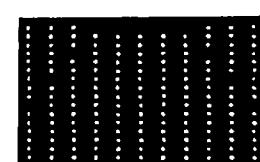

Photo. 9.4.1  $\alpha=0.8$ の場合

Photo. 9.4.2  $\alpha=0.6$ の場合

Photo. 9.4.3  $\alpha=0.4$ の場合

Photo. 9.4.4  $\alpha=0.2$ の場合

Photo. 9.4 代数積代数和型ファジィレジスタを用いた max-代数積合成

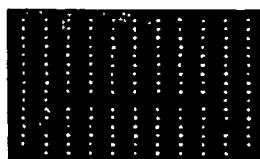

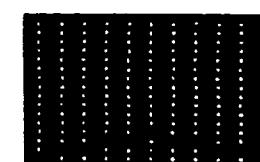

Photo. 9.5.1  $\alpha=0.8$ の場合

Photo. 9.5.2  $\alpha=0.6$ の場合

Photo. 9.5.3  $\alpha=0.4$ の場合

Photo. 9.5.4  $\alpha=0.2$ の場合

Photo. 9.5 リセット型限界積限界和型ファジィレジスタを用いた max-限界積合成

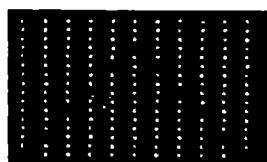

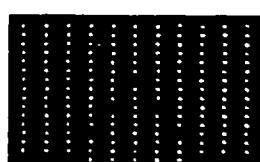

Photo. 9.6.1  $\beta=0.2$ の場合

Photo. 9.6.2  $\beta=0.4$ の場合

Photo. 9.6.3  $\beta=0.6$ の場合

Photo. 9.6.4  $\beta=0.8$ の場合

Photo. 9.6 代数積代数和型ファジィレジスタのセット機能

Photo. 9.7.1  $\beta=0.2$ の場合

Photo. 9.7.2  $\beta=0.4$ の場合

Photo. 9.7.3  $\beta=0.6$ の場合

Photo. 9.7.4  $\beta=0.8$ の場合

Photo. 9.7 セット型限界積限界和型ファジィレジスタのセット機能

チのタイミングパルス  $C_2$  に分離することによって回路全体を制御している。このクロック同期用パルス  $C_1$  と  $D$  ラッチが作動用パルス  $C_2$  のタイムチャートを Fig. 8.1 に示す。

### § 9. ファジィレジスタ回路の動作

ここではメンバーシップ関数として一般的に最も多く用いられているベル形（三角形）のものを用いた場合について、本論文で提案した各種ファジィレジスタの諸動作の例を Photo 9.1～9.7 によって示す。

メンバーシップ関数のセット機能を Photo. 9.1 に示す。これは Table. 7.1 に示すように制御信号である  $S_1$  を Low,  $S_2$  を 1111,  $K_{ui}(t)$  を 0000 とし、また  $J_{ui}(t)$  入力端子に任意のファジィ値を入力することにより実現可能である。

またメンバーシップ関数の反転出力機能を Photo. 9.2 に示す。これは Table. 7.1 に示すように制御信号である  $S_1$  を Low,  $S_2$  を 1111,  $K_{ui}(t)$  を 1111 とし、また  $Q_{ui}(t)$  入力端子に任意のファジィ値が入力されることにより実現可能である。ここでは一例として min max 型ファジィレジスタを用いたがこの機能は本論文で用いたすべてのファジィレジスタにおいて実現可能な基本的な機能である。

次にファジィ推論で一般的に知られている max-min 合成, max-代数積合成, max-限界積合成をファジィレジスタによって実現した結果をそれぞれ Photo. 9.3, Photo. 9.4, Photo. 9.5, に示す。これらはそれぞれ min max 型ファジィレジスタ, 代数積代数和型ファジィレジスタ, リセット型限界積限界和型ファジィレジスタにおいて行うことのできる機能である。これらは全てファジィプロダクションルールに記述された前件部メンバーシップ関数と入力情報との  $t$  ノルム演算を行った結果の照合度を  $\alpha$  とし、後件部メンバーシップ関数が既にファジィレジスタに記憶されているものとしてファジィレジスタの基本セルに  $J_{ui}(t)=0, K_{ui}(t)=1-\alpha$  を入力することで後件部メンバーシップとの  $t$  ノルム演算を実現している。

また代数積代数和型ファジィレジスタのセット機能, セット型限界和型ファジィレジスタのセット機能による前件部メンバーシップ関数の軽みづけの例をそれぞれ Photo. 9.6, Photo. 9.7 に示す。結果はすべての場合に理論どおりの動作を実現している。

### § 10. おわりに

二値  $J-K$  フリップフロップのファジィへの拡張として定義されたファジィフリップフロップを、台集合のカージナル数だけ用いてメンバーシップ関数の記憶モジュールとしてのファジィレジスタを提案した。ファジィフリップフロップは二値のレジスタや計数器の基本単位である  $J-K$  フリップフロップのファジィ拡張として定義されているため、ファジィ情報の一時記憶素子的要素が強いものとなる。従って、ファジィ情報のメモリ機能のみを有するエレメント（ディジタル

メモリやアナログ方式のファジィメモリ)とは多少異なる。

本論文で提案したファジィレジスタはファジィフリップフロップを基本として用いているため、メンバーシップ関数等の記憶や各種ファジィ演算機能を有するメモリモジュールとして利用できる。このファジィレジスタを用いるとメンバーシップ関数の記憶、反転出力、その他各種ファジィ合成演算が可能であることを示した。また、記憶したメンバーシップ関数を台集合上で左右にシフト可能なファジィシフトレジスタの提案も行った。このファジィシフトレジスタを用いるとファジィプロダクションルールに記述されたメンバーシップ関数のラベルやグレードの変更も可能となる。

現在のファジィ推論アルゴリズムが非常に多様化している等(特にファジィエキスパートシステム等の分野で)、将来的にみて各種ファジィ演算機能を有する汎用ファジィメモリモジュールの実用化が望まれるところである。また、ここで提案したファジィレジスタは多段階でより奥の深いファジィ推論等に用いると有用であるといえる。最後にファジィレジスタを市販の汎用メモリ素子を用いて試作設計し、動作確認をした。

### 参考文献

- 1) M. Togai and H. Watanabe: A VLSI Implementation of A Fuzzy Inference Engine Toward an Expert System on a Chip, *Information Science*, 38, pp.147/163, 1986.

- 2) T. Yamakawa: Fuzzy Microprocessor—Rule Chip and Defuzzifier Chip, *Proc. of International Workshop on Fuzzy System Applications*, Iizuka Japan, pp.51/52, 1988.

- 3) H. Watanabe and Wayne Dettloff: Reconfigurable Fuzzy Logic Processor A Full Custom Digital VLSI, *Proc. of International Workshop on Fuzzy System Applications*, Iizuka Japan, pp.49/50, 1988.

- 4) 有川、廣田、坂和: 仮想ページング方式ファジィチップとファジィ開発ステーション、第5回ファジィシステムシンポジウム講演論文集, pp.53/58, 1989.

- 5) T. Yamakawa and K. Sasaki: Fuzzy Memory Device, Preprints of 2nd IFSA Congress, pp.551/555, 1987.

- 6) K. Hirota and K. Ozawa: The Concept of Fuzzy Flip-Flop, *IEEE Transactions on Systems, Man and Cybernetics*, Vol. 19, No. 5 (to appear 1989).

- 7) K. Hirota and K. Ozawa: Fuzzification of Flip-Flop Based on Various Fuzzy Logical Operation, *Bulletin of the college of Eng. Hosei Univ.*, No. 23, March, 1987, pp.69/94.

- 8) K. Hirota and K. Ozawa, Fuzzy Flip-Flop as a Basis of Fuzzy Memory modules, *Fuzzy Computing (Theory, Hardware and Applications)*, North-Holland, 1988, pp.173/183.

- 9) 小沢、廣田: 離散値型ファジィフリップフロップ、電気学会論文誌C, Vol. 109-C, No. 5, May, 1989, pp.383/389.

- 10) K. Hirota, K. Ozawa, Laszlo T. Koczy, K. Omori: Discrete Mode Algebraic Fuzzy Flip-Flop Circuit, *Proc. of International Workshop on Fuzzy System Applications*, (August, 1988, Iizuka Japan), pp.39/40.

- 11) K. Ozawa, K. Hirota, Laszlo T. Koczy, K. Omori: Discrete and Continuous Mode Algebraic Type Fuzzy Flip-Flop Circuits, *Bulletin of the college of Eng. Hosei Univ.*, No. 25, February, 1989, pp.55/63.