# 法政大学学術機関リポジトリ

## HOSEI UNIVERSITY REPOSITORY

PDF issue: 2025-07-06

# n-well CMOS構造におけるラッチアップ特性 の過渡解析

CHOI, Won-Cheol / HIGASHI, Yosuke / YATAKA, Shin-ichi / 崔, 愿哲 / 東, 洋介 / 谷高, 真一 / Dang, Ryo / 檀, 良

```

(出版者 / Publisher)

法政大学工学部

(雑誌名 / Journal or Publication Title)

法政大学工学部研究集報 / 法政大学工学部研究集報

(巻 / Volume)

36

(開始ページ / Start Page)

1

(終了ページ / End Page)

5

(発行年 / Year)

2000-03

(URL)

https://doi.org/10.15002/00003791

```

## n-well CMOS 構造におけるラッチアップ特性の過渡解析

### 東洋介 崔愿哲 谷高真一 檀良

Transient Analysis of Latchup Characteristics in n-well CMOS Structure

Yosuke HIGASHI, Won-choel CHOI, Shin-ichi YATAKA and Ryo DANG

#### Abstract

The latchup phenomenon is a difficult issue in CMOS structure. The purpose of this study is a better understanding of latchup mechanism, and a minute observation of a device behavior until latchup using a device simulator. We simulate latchup characteristics in n-well CMOS device using a trapezoidal or a triangular trigger pulse or a multiple of them. As a result, we found that the latchup characteristics are different in each case. Also, the internal distribution is shown as a function of time to clearly the latchup mechanism.

#### 1. はじめに

近年、計算機などの能力の向上から半導体デバイスシミュレーション技術を用いた研究が盛んに行われている。その中でも、一つの基板に nMOS デバイスと pMOS デバイスを設けた CMOS 回路は、MOSFET が入力に対し、交互に ON, OFF の状態になり、それぞれのトランジスタが相補的にスイッチングする構造のため消費電力が小さく、ノイズに強いなど優れた特徴があり集積度の向上とともに重要度を増してきた素子である。

しかし、案子寸法の微細化が進むに連れ案子分離に十分なスペースの確保が困難であるために、 寄生サイリスタ回路が構成され、ラッチアップと呼ばれる破壊現象が起こりやすくなる。このラッ チアップは CMOS 構造にとって唯一の弱点で、ラッチアップを起こりにくくするための研究が活発 である。

従って今回, ラッチアップメカニズムのより深い理解, そしてラッチアップに至るまでのデバイス内部における挙動を把握するため, デバイスシミュレータを用いてラッチアップ特性の解析を行った.

#### 2. 解析方法

### 2.1. 支配方程式と解析対象

解析に用いたモデルはポアソン方程式,時間項を考慮した電子および正孔についての電流連続式からなるドリフト拡散モデルである.

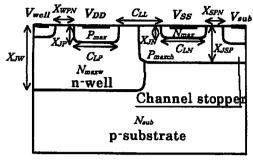

次に, 今回解析を行ったラッチアップ解析用 CMOS 構造を図 1 に示す. また. 構造パラメータは 以下の値を用いた.

図 1. 解析構造

$(X_{JP}=0.3[\mu m], X_{JN}=0.2[\mu m], C_{LP}=1.0[\mu m],$   $C_{LN}=1.0[\mu m], C_{LL}=6.0[\mu m], X_{JW}=3.0[\mu m],$   $X_{JSP}=0.45[\mu m], X_{WPN}=3.0[\mu m], X_{SPN}=3.0[\mu m],$   $P_{maxch}=4.0\times10^{16}[cm^{.3}],$   $N_{sub}=1.0\times10^{15}[cm^{.3}], N_{maxw}=1.5\times10^{16}[cm^{.3}],$  $P_{max}=1.0\times10^{20}[cm^{.3}], N_{max}=1.0\times10^{20}[cm^{.3}])$

#### 2.2. 解析手法

今回行った, 二種類の解析手法を以下に示す.

#### 2.2.1. 解析手法(1)

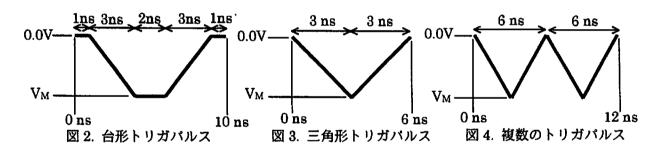

第一の解析手法としては、まず始めに  $V_{\text{sub}}$  電極を接地し、次に  $V_{\text{well}}$ ,  $V_{DD}$  電極をそれぞれ定常で 5.0[V]まで上げて、最後にトリガパルスを  $V_{\text{SS}}$  電極に入れる。そこで、今回使用した台形、三角形そして複数のトリガパルスをそれぞれ図 2.3.4 に示す。

#### 2.2.2. 解析手法(2)

ラッチアップ特性を解析するに当たり、従来電極に対して与えてきた境界条件である電圧固定境界条件では解析が困難であるため VDD 電極の外部に抵抗を設け、VDD 電極を浮遊にして解析を行う電流境界条件を用いた.

解析手順としてはまず始めに  $V_{\text{sub}}$ ,  $V_{\text{ss}}$  電極を接地し, 次に  $V_{\text{well}}$  電極を定常で 5.0[V]まで上げて, そして外部抵抗を設けた  $V_{\text{DD}}$  電極にパルスを入れる.

#### 3. シミュレーション結果

#### 3.1. 様々なパルスを用いた解析結果

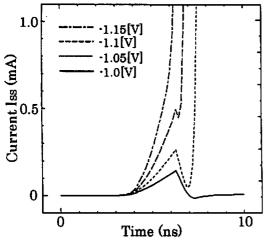

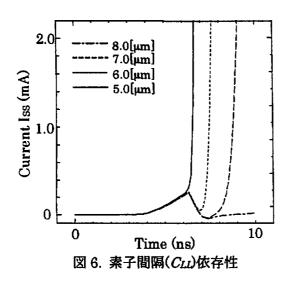

図 5 及び図 6 は台形トリガバルスを入れた時のシミュレーション結果である. トリガバルス高さ  $V_M$ が-1.05[V]より大きい時, トリガにより発生した電流はトリガを offにしても流れ続けていること が分かる. つまりラッチアップが起こっているためであり, この時のラッチアップ電圧は-1.05[V]と 言える. また,  $V_M$ を-1.05[V]にした時の素子間隔依存性(図 6)から素子間隔  $C_{LL}$ が 7.0[ $\mu$ m]以下になるとラッチアップに達している.

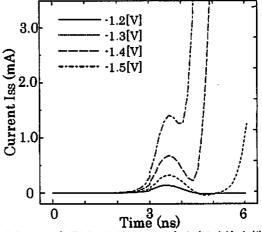

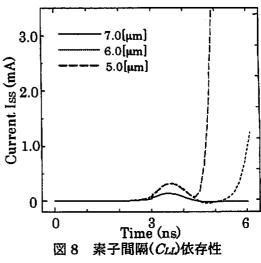

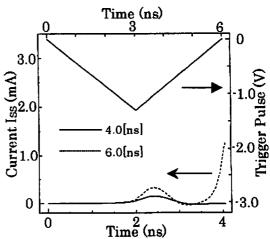

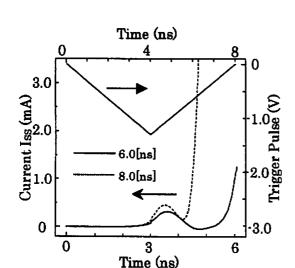

次に、三角形トリガパルスにおいてトリガパルス高さ、素子間隔、パルススピードを変化させたときの解析結果をそれぞれ図 7, 8, 9, 10 に示す。これらの結果は図 5, 6 に示した台形トリガパルスと比較すると、トリガ維持時間が極端に短いため、ラッチアップが発生しづらくなることが分かる。また、図 9, 10 から  $V_M$ が・1.3[V]の時、パルススピードが 4.0[ns]より大きくなるとラッチアップ現象が

観察できる.

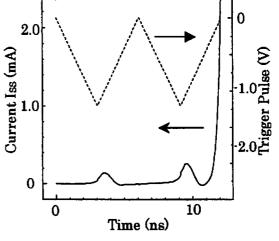

さらに、時間推移においてラッチアップ現象がどのようにして発生するのかを調査 するために、図 7 における V<sub>M</sub>が·1.2[V]の三角形トリガパルスを続けてもう一回入力し解析したのが図 11 である. この解析結果から、一回目のトリガパルスによって素子間に蓄積されたキャリアが二回目のトリガパルスに影響し、ラッチアップが起こることが分かる.

図 5. 台形トリガパルス高さ(VM)依存性

図 7. 三角形トリガパルス高さ(V<sub>M</sub>)依存性

図 9. 三角形トリガパルス時間依存性

図 10. 三角形トリガパルス時間依存性

図 11. トリガパルスを複数入れた時の特性

#### 3.2. 電流境界条件を用いた解析結果

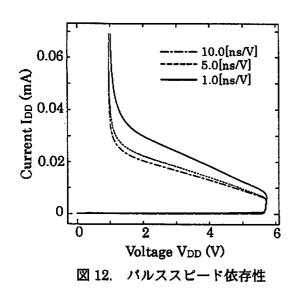

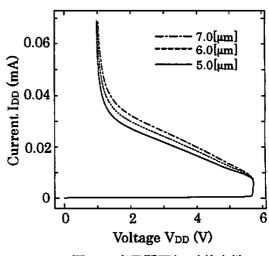

図 12, 13 は VDD 電極に境界条件として、電流境界条件を用いたシミュレーション結果である。これら全ての解析結果において、VDD 電極電圧が約 5.5[V]でラッチアップが発生し、その後、電圧降下現象、そして電流値が急激に増加するという特性が観察できる。 この電圧降下現象は高電界による空乏層の広がりから、寄生バイポーラトランジスタが導通したことに起因する.

そこで、様々なパルススピードによりこの特性を調査したのが図 12 である. この解析結果からパルススピードが遅くなると、電圧降下現象が急激になることが確認できる. 従ってトリガ時間が長くなるに連れて、 寄生パイポーラトランジスタの導通が速くなると言える.

また、図 13 はパルススピード 1.0[ns/V]において素子間隔を変化させた解析結果である。この結果も同様に、素子間隔が小さくなると寄生バイポーラトランジスタの導通が速くなるために、電圧降下が急激になっていることが確認できる。

図 13. 素子間隔(CLL)依存性

#### 4. まとめ

今回, 二種類の解析手法を用いてn-well CMOS 構造におけるラッチアップ解析を行った. 第一に, 三パターン(台形, 三角形, 複数)のトリガバルスを使用した解析. 第二に, 電極部条件として電流境界条件を用いた解析である.

結果として、ラッチアップ電圧はそれぞれのトリガバルスにおいて、多少の違いはあるが(台形:-1.05[V]、三角形:-1.3[V])、ラッチアップ現象の特徴である、電流値がいったん減少しそれから増加してラッチアップに至るという特性については三パターンのトリガバルスが共にこの特性を示した。

さらに、電流境界条件を用いた解析より、電圧降下現象のメカニズムを確認し、パルススピードは 遅く、素子間隔は小さくなるに連れ、電圧降下が急激になることを示した.

### 参考文献

- [1] Ohzone and Iwata, "Transient Latchup Characteristics in n-Well CMOS," *IEEE Trans. Electron Devices*, vol. ED-39, pp.1870-1875, 1992

- [2] William M. Coughran, Jr., Mark R. Pinto, R. Kent Smith, "Computation of Steady-State CMOS Latchup Characteristics," *IEEE Trans. Computer-Aided Design*, vol. 7, NO. 2, pp.307-323, FEBRUARY 1988

- [3] 小田中 紳二, 若林 睦子, 大曽根 隆志, 竹本 豊樹, "CMOS 構造の2次元デバイス過渡解析," 電子通信学会論文誌, vol. J67·C, No. 11, 1984

- [4] G.J.Hu, "A Better Understanding of CMOS Latch-up, " *IEEE Trans. Electron Devices*, vol. ED-31, pp.62-67, 1984