# 法政大学学術機関リポジトリ

#### HOSEI UNIVERSITY REPOSITORY

PDF issue: 2024-10-28

# 並列化DC/DCコンバータの呈する現象解析と その安定化

石川, 裕己 / ISHIKAWA, Yuuki

(発行年 / Year)

2008-03-24

(学位授与年月日 / Date of Granted)

2008-03-24

(学位名 / Degree Name)

修士(工学)

(学位授与機関 / Degree Grantor)

法政大学 (Hosei University)

## 2007年度修士論文

# <sub>論文題名</sub> 並列化 DC/DC コンバータの 呈する現象解析とその安定化

Analysis and Stabilization of Paralleled DC/DC Converters

指導教授 斎藤 利通 教授

法政大学大学院工学研究科 電気工学専攻修士課程

学生証番号: 06R3101

イシカワ ユウキ 氏名: 石川 裕己

## あらまし

本論文では並列化 DC/DC コンバータ (PDCs) の呈する現象とその安定化について述べる。はじめに多入力系 PDCs の簡略化モデルの非線形なダイナミクスについて考察する。位相制御に Winner-Take-All (WTA) Switching を適用する。これは自動的に多相同期を実現できるが、パラメータを変化させると様々な周期的/カオス現象を呈する。系のダイナミクスを解析するために区分定数モデルを用い、無次元化されたパラメータを導出する。また解析手法として Hybrid Return Map (HRM) を導出する。そして典型的な分岐現象を示し、多相同期、Hyperchaos、複雑な超安定現象といった多彩な現象を HRM により解析する。

次に単体の DC/DC コンバータと PDCs について 2 つのスイッチングルールを適用する。まず単体の系において区分線形の位相マップを導出し、周期的/カオス的な現象を解析する。そしてパラメータに対する不動点の安定性を明らかにする。次に並列化の系においてパラメータに対する安定な多相同期の領域を明らかにし、スイッチングルールを切り替えることで幅広いパラメータ領域において安定な動作を実現できることを示す。

最後に回路実験により、単体/並列化において系の呈する典型的な現象を確認する。

## Abstract

This paper studies the analysis and stabilization of the paralleled dc-dc converters (PDCs). First, we consider the nonlinear dynamics of a simplified model of multiple-input PDCs. We apply winner-take-all (WTA) switching for phase control method. WTA switching can realize multi-phase synchronization automatically. However, as parameters vary, this system exhibits a variety of periodic/chaotic phenomena. In order to analyze system dynamics, we adopt a piecewise constant modeling, extract essential parameters in a dimensionless circuit equation and derive a hybrid return map (HRM). We then investigate typical bifurcation phenomena and analyze multi-phase synchronization, hyperchaos, complicated superstable behavior by HRM.

Next, we apply two kinds of switching rules for single/parallel dc-dc converters. In the single system, we derive a piecewise linear phase map and analyze precisely for periodic/chaotic behavior. We then clarify the stabilization of a fixed point for the parameter. In the parallel system, we clarify the region of stable multi-phase synchronization for the parameter. We can realize that the stable operation is always possible by the proper use of switching rules for the wide parameter region.

Finally, we present a simple test circuit, typical operations are confirmed experimentally in the single/parallel system.

# 目次

| <b>お</b> Ⅰ早         | まえが <del>さ</del>                                                                                        | 7                          |

|---------------------|---------------------------------------------------------------------------------------------------------|----------------------------|

| 第2章                 | 並列化 DC/DC コンバータ (PDCs) の呈する現象                                                                           | 12                         |

| 2.1                 | まえがき                                                                                                    | 12                         |

| 2.2                 | 多入力系並列化 Buck コンバータの基本動作                                                                                 | 13                         |

| 2.3                 | Hybrid Return Map                                                                                       | 18                         |

| 2.4                 | PDCs <b>の呈する分岐現象</b>                                                                                    | 25                         |

|                     | $2.4.1$ 一入力系 $a_j=a$ の分岐 (CCM)                                                                          | 25                         |

|                     | $2.4.2$ 多入力系 $a_j \neq a$ の分岐 (CCM)                                                                     | 25                         |

|                     | $2.4.3$ DCM を含む多入力系 $a_j \neq a$ の分岐 $\dots \dots$                                                      | 26                         |

| 2.5                 | むすび                                                                                                     | 34                         |

|                     |                                                                                                         |                            |

| 第3章                 | 2 スイッチングルールを用いた系の安定動作化                                                                                  | 35                         |

| 第 <b>3</b> 章<br>3.1 | 2 スイッチングルールを用いた系の安定動作化<br>まえがき                                                                          |                            |

| 3.1                 |                                                                                                         | 35                         |

| 3.1                 | まえがき                                                                                                    | 35<br>36                   |

| 3.1                 | まえがき                                                                                                    | 35<br>36<br>36             |

| 3.1                 | まえがき          単体の DC/DC コンバータ          3.2.1 回路モデルと基本動作                                                 | 35<br>36<br>36<br>41       |

| 3.1                 | まえがき          単体の DC/DC コンバータ          3.2.1 回路モデルと基本動作          3.2.2 位相マップと系の安定性                      | 35<br>36<br>36<br>41<br>49 |

| 3.1                 | まえがき       単体の DC/DC コンバータ         3.2.1 回路モデルと基本動作          3.2.2 位相マップと系の安定性          並列化 DC/DC コンバータ | 35<br>36<br>36<br>41<br>49 |

| 3.1                 | まえがき単体の DC/DC コンバータ3.2.1 回路モデルと基本動作3.2.2 位相マップと系の安定性並列化 DC/DC コンバータ3.3.1 回路モデルと基本動作                     | 35<br>36<br>36<br>41<br>49 |

|      | 3.4.2 | 並列化 | Buck | コン | バー | タ |       | <br> |       | <br>• | <br> |  | <br>61     |

|------|-------|-----|------|----|----|---|-------|------|-------|-------|------|--|------------|

| 3.5  | むすび   |     |      |    |    |   | <br>• | <br> | <br>• |       | <br> |  | <br>65     |

| 第4章  | 結論    |     |      |    |    |   |       |      |       |       |      |  | 66         |

| 参考文南 | ‡     |     |      |    |    |   |       |      |       |       |      |  | 68         |

| 研究業績 | 生     |     |      |    |    |   |       |      |       |       |      |  | <b>7</b> 3 |

| 謝辞   |       |     |      |    |    |   |       |      |       |       |      |  | 75         |

# 図目次

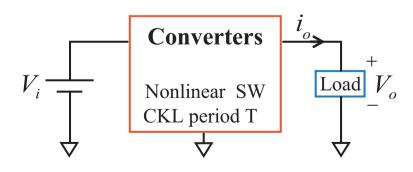

| 1.1  | DC/DC <b>コンバータの</b> 概略図                                                        | 8  |

|------|--------------------------------------------------------------------------------|----|

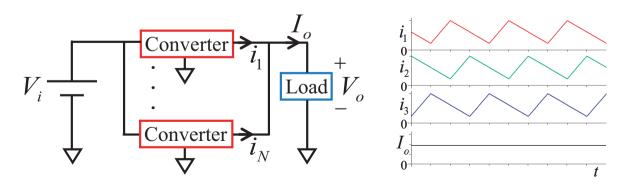

| 1.2  | 並列化 DC/DC <b>コンバータの</b> 概略図                                                    | 10 |

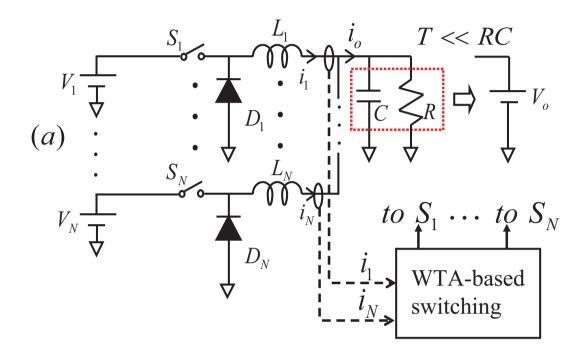

| 2.1  | 多入力系並列化 DC/DC <b>コンバータ</b>                                                     | 16 |

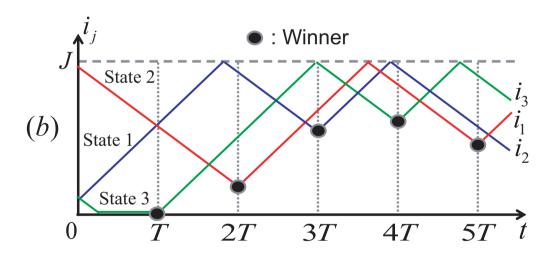

| 2.2  | 3相同期の典型的な波形                                                                    | 17 |

| 2.3  | 5 種類の基本的な軌道                                                                    | 21 |

| 2.4  | Hybrid return maps $\succeq$ 3D plots $(N=3 \text{ and } a_1=a_2=a_3\equiv a)$ | 22 |

| 2.5  | HRM <b>の典型的な形</b>                                                              | 23 |

| 2.6  | 典型的な時間波形 $(N=3,a_1=a_2=a_3\equiv a)$                                           | 24 |

| 2.7  | 一入力系の HRMs と 3-D Plots $(N=3, a_1=a_2=a_3\equiv a, b^{-1}=3.3).$               | 28 |

| 2.8  | 一入力系の分岐現象 $(N=3,a_1=a_2=a_3\equiv a,b^{-1}=3.3)$                               | 29 |

| 2.9  | 多入力系の HRMs と 3-D Plots $(N=3,a_1^{-1}=a_2^{-1}=1.5,b^{-1}=3.3)$                | 30 |

| 2.10 | $0$ 多入力系の分岐現象 $(N=3,a_1^{-1}=a_2^{-1}=1.5,b^{-1}=3.3).$                        | 31 |

| 2.1  | 1 多入力系の HRMs と 3-D Plots $(N=3, a_1^{-1}=a_2^{-1}=1.2, b^{-1}=2.4)$            | 32 |

| 2.13 | $2$ 多入力系の分岐現象 $(N=3,a_1^{-1}=a_2^{-1}=1.2,b^{-1}=2.4).$                        | 33 |

| 3.1  | 単体の DC/DC コンバータとスイッチングルール                                                      | 39 |

| 3.2  | 単体のコンバータの典型的な波形                                                                | 40 |

| 3.3  | 出力波形の軌道                                                                        | 44 |

| 3.4  | Rule 1 <b>の位相マップ</b>                                                           | 45 |

| 3.5  | Rule 2 <b>の位相マップ</b>                                                           | 46 |

| 3.6  | 典型的な分岐現象・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                                   | 47 |

| 3.7  | 安定な不動点に対するパラメータ条件....................                                          | 48 |

| 3.8  | 並列化 DC/DC コンバータとスイッチングルール   | 51 |

|------|-----------------------------|----|

| 3.9  | PDCs の典型的な波形 $(N=3)$        | 52 |

| 3.10 | 周期軌道の相似形                    | 55 |

| 3.11 | パラメータ条件 $(N=3)$             | 56 |

| 3.12 | リップル特性 $(N=3)$              | 57 |

| 3.13 | Buck <b>コンバータの実験回路</b>      | 59 |

| 3.14 | Buck <b>コンバータの観測波形</b>      | 60 |

| 3.15 | 並列化 Buck コンバータの実験回路         | 63 |

| 3.16 | 並列化 Buck コンバータの観測波形 $(N=3)$ | 64 |

## 第1章 まえがき

パワーエレクトロニクス技術は今日までにほぼ完成され、産業の基盤技術であると ともに必要不可欠な技術となっている。近年、この技術は、電力システムのような高 電圧、大容量システムへの適用、エンジン等の熱機関に代わる動力源、さらにはチッ プ上に電源の全機能を組み込んだ小容量、低損失素子の開発といったようにその関連 分野を広げている。DC/DC コンバータは直流電力を所望の直流電力に変換するのに 用いられているパワーコンバータの一種であり、様々な電子機器の電源部分で用いら れている。パワーコンバータは、スイッチング動作を実現する素子(ダイオード、サイ リスタ、パワー MOSFET など) により、入力電力を所望の安定した電力に変換する電 源回路である。DC/DC コンバータのほかに、直流電力を所望の交流電力に変換する インバータ、交流電力を所望の直流電力に変換する整流回路、交流電力を所望の交流 電力に変換するサイクロコンバータなどが挙げられる。これらのパワーコンバータは、 所望の電力変換や損失の少ない高い変換効率が求められ、パワーエレクトロニクスの 分野においては重要な技術である。また、パワーコンバータは実際の電子機器の電源 などの実用的な回路に使用されている一方で、カオスや分岐現象といった多彩な非線 形現象を呈するスイッチトダイナミカルシステム (Switched Dynamical System) であ り、基礎研究と実用的な見地の両面において幅広く研究されている [1]-[4]。パワーエレ クトロニクスの分野においてそれらの非線形現象を解析することは、以下のことに意 義があると考えられる:

(1) 分岐現象: システムの呈する分岐現象を調べることにより、安定な動作をする領域や不安定な動作をする境界がわかる。これはパラメータに対するシステムの安定動作領域を明らかにすることにつながり、実際に設計する際の基準となる [5] [6]。

- (2) 多相同期 (Multi-phase synchronization: N-SYN): 並列化 DC/DC コンバータ (Paralleled DC/DC Converters: PDCs) において、N-SYN の実現はカレントシェアによる低電圧・大電流の供給や、リップルを低減できることが考えられ、次世代のマイクロプロセッサの電源に期待されている [7] [8]。

- (3) カオス: 電磁妨害 (Electro Magnetic Interference: EMI) に対する耐性の向上が考えられるのではないか [9]。

本修士論文では DC/DC コンバータを研究対象にする。DC/DC コンバータは直流チョッパと呼ばれる電力変換回路で、負荷に印加する電圧、負荷に流す電流を断続 (チョッピング) することにより、直流電圧、電流を変成する機器であり、パワーエレクトロニクスの分野において基本的な電源回路である。図 1.1 に DC/DC コンバータの概略図を示す。DC/DC コンバータは、直流電圧を非線形なスイッチングと周期 T のクロックを有するコンバータによって所望の直流電圧に変換する。スイッチングのために回路に何らかのフィードバック制御を付加する。フィードバックには、負荷電流値に基づく電流モード制御 (Current Mode Control: CMC) と負荷電圧値に基づく電圧モード制御 (Voltage Mode Control: VMC) がある。本研究ではスイッチ制御に CMC を用いる。DC/DC コンバータは入力電圧  $V_i$  と出力電圧  $V_o$  の関係によって、以下の代表的な3つの種類に分類される:

Buck コンバータ: 直流電圧を下げる目的で使用される  $(0 < V_o < V_i)$ 。

Boost コンバータ: 直流電圧を上げる目的で使用される  $(0 < V_i < V_o)$ 。

Buck-Boost コンバータ: Buck コンバータと Boost コンバータの双方の機能をもた

図 1.1: DC/DC **コンバータの**概略図

せたコンバータで、電圧を昇圧および降圧できる  $(0 < V_i, 0 < V_o)$ 。

一方、DC/DC コンバータはカオス [10]、Sub-harmonics [11] や分岐 [12] といった 多彩な現象を呈することで知られている興味深い非線形システムである。パワーコン バータにおけるこれらの現象や安定性を解析するために、Averaging Models [13]、Small Signal Models [5]、Piecewise Linear Models [1]、Distrete-time Models [3] といった様々 なモデルが用いられ、研究されている。その中で我々は DC/DC コンバータの呈する 現象を解析するために、区分定数 (Piecewise Constant Models: PWC) モデルを用いて 研究を行っている [6] [14]。 PWC モデルは、ある条件下ではシステムのベクトル場は 区分定数で表せるので解軌道は区分線形 (Piecewise Linear: PWL) な軌道となり、回 路のダイナミクスや各現象の存在領域などを理論的に解析することができる。DC/DC コンバータにおいては、スイッチング周期 (クロックT) に対して回路の時定数が十分 に大きいとき、負荷側を定電圧源とみなすことで PWC モデルを適応している [6] [14] [23]。また、PWC モデルはパワーコンバータだけでなく、様々な非線形回路の解析に も有効である [15] [16]。我々は PWC モデルを用いて DC/DC コンバータの呈する現 象を解析してきた。更に我々は回路の素子のパラメータに対して、無次元化変数を用 いることでそれらを統合した2つのパラメータに変換し、考察している。そして系の 呈する現象を解析するために PWL な 1D マップを導出し、パラメータに対する周期 的/非周期的な動作をする領域を明らかにしている [6]。このように系の呈する現象を 解析することは、基礎研究や実際のシステムの構築のための重要な情報となる。

DC/DC コンバータを並列に接続した並列化 DC/DC コンバータ (Paralleled DC/DC Converters: PDCs) もまた幅広く研究されている。PDCs は図 1.2 左図に示すように、N 個のコンバータを入力電圧と出力側の負荷の間に並列に接続した回路である。PDCs の利点として以下に挙げる:

(1) 各コンバータで負荷電流を分担する (Current Sharing) ため、低電圧・大電流を供給することができ、次世代のマイクロプロセッサ電源として期待されている [7] [8] [17] [18]。 Current Sharing は信頼性や耐久性の向上についても有効であると考えられる。

- (2) 図 1.2 右図のように N-SYN (図は N=3 の場合)を実現することで出力電流  $I_o$  のリップルの低減が可能である [19] [20]。リップルを低減することはスイッチング時の損失や、伝導損失を少なくすることにつながる。これは安定した電力を供給することを目的とするパワーコンバータにおいては、非常に重要なことと考えられる。このような N-SYN を実現するための位相制御法として、Sliding Mode Control [19]、Digital Logic Control [20]、Wireless PWM Control [21] など様々な方法が研究されている。

- (3) PDCs は複数の DC/DC コンバータを並列に接続しているため、その中の1つが 故障した場合において高いリカバリー能力があると考えられる。

また PDCs は多彩な同期や分岐現象を呈する興味深い高次元のスイッチトダイナミカルシステムとしても知られている [22] [23]。我々はスイッチングに Winner-Take-All (WTA) の原理 [23] [24] を適用し、独自の PDCs モデルについて系の呈する現象の解析や回路実験等を行っている。WTA は複数ある中から勝者 "Winner" を選択するというものだが、我々のようなパワーコンバータ以外でも、Self-organizing Neural Networks [25] や Multiplex Communications [26] といった様々なシステムで適用されている。PDCs において、WTA Switching は自動的に N-SYN を実現することができる。我々は WTA Switching に基づく PDCs のモデルにおいて、N-SYN が安定/不安定となるパラメータ領域を明らかにし、回路実験において動作を確認している [23]。

一方で PDCs は多入力系のクリーンエネルギー電源 [27] としても研究されている: Solar-cells [28]、Fuel-cells [29]、Hybrid Vehicles [30] など。このシステムは異なる入力に対して、安定した出力を供給するための電源回路として研究されている。

図 1.2: 並列化 DC/DC コンバータの概略図.

これらの背景をふまえて本修士論文では、WTA Switching に基づく PDCs の呈する非線形現象を Hybrid Return Maps を導入して解析する。また2つのスイッチングルールを用いてシステムの安定化を図るという実用的な方面からのアプローチを行う。本論文は4章から構成され、以下にその概要を述べる。

第2章では、非線形力学系である多入力系 PDCs の PWC モデルにおいて、系の呈する現象を調べる [31] [32]。位相制御法には WTA Switching を適用する。この系では入力電圧が全て等しい場合は一入力系に相当し、文献 [23] などで議論されている。多入力系では複数の入力に対して安定した出力が求められる。その中でパラメータに対する分岐現象を調べることは、安定な N-SYN から不安定な N-SYN (カオス, Hyperchaos, 複雑な超安定現象など) へ変わる境界を調べることに対応する。これは実際のシステムの設計において重要な情報となる。現象解析する手法として Hybrid Return Map (HRM)を導出する [33]。HRM はパラメータにより様々な形になり、各々のコンバータの出力がどのような振る舞いをしているのかを視覚的に見ることができる。ここでは一入力系と多入力系の PDCs において、それぞれシステムの呈する現象を調べ、HRM を用いて考察する。

第3章では、2章で示されるようなパラメータに対する不安定な振る舞いに対して、2つのスイッチングルールを適用し幅広いパラメータ領域出での系の安定化法について言及する [34]。まず単体の Buck コンバータについて、2章とは異なる位相マップを導する [35]。そして2つのスイッチングルールにおいて、それぞれパラメータに対する不動点の安定性について考察する。次に WTA Switching に基づく PDCs についても同様に考える。単体の系での安定性を基に、それぞれのスイッチングルールにおいてパラメータに対する N-SYN の安定性を明らかにする。またパラメータに対するリップルの変化を示すリップル特性を求める。最後に単体と並列系の両方のシステムにおいて簡素な回路を実装し、出力波形を観測しその動作を確認する。

第4章では、本論文の全体的な結論と今後の課題についてまとめる。

# 第2章 並列化 DC/DC コンバータ (PDCs) の呈する現象

#### 2.1 まえがき

本章では、並列化 DC/DC コンバータ (PDCs) の呈する現象を解析する。単体の DC/DC コンバータの呈する現象については、文献 [6] 等で詳細な解析がなされてい る。PDCs については、位相制御に WTA を用いて N-SYN の安定性についてや簡単な 回路実験は行われている [23] が、並列系の呈する現象の解析については不十分である。 本章では多入力系 PDCs の区分定数 (PWC) モデルを提案し、現象を解析するた めに Hybrid Return Map (HRM) を導出する。このモデルは入力電圧が全て等しいと き、一入力系 PDCs に対応する。位相制御には WTA Switching を適用する。WTA Switching は自動的に多相同期 (N-SYN) を実現することができる。はじめに回路の ダイナミクスを PWC モデルに簡単にし、無次元の回路方程式を導出する。この区 分定数な方程式は多入力、一入力の両方の系において記述でき、その軌道は区分線形 (PWL) であり、詳細な解析に適する [6] [23]。次に Hybrid Return Map を導出する。 HRM は連続導通モード (Continuous Conduction Mode: CCM) や不連続導通モード (Discontinuous Conduction Mode: DCM) の両方に対して、システムの振る舞いを視 覚化したり解析するのに役立つ。HRM を用い、典型的な分岐現象を示し解析する: N-SYN から Hyperchaos の分岐、異なる入力によるゆがんだ N-SYN からカオス、そし て複雑な超安定 (Superstable) な現象への分岐など。これらの結果は実際の回路設計や 新しい分岐理論の発展に対する重要な情報となる。

これらの内容は、文献 [31] [32] [33] をまとめたものである。

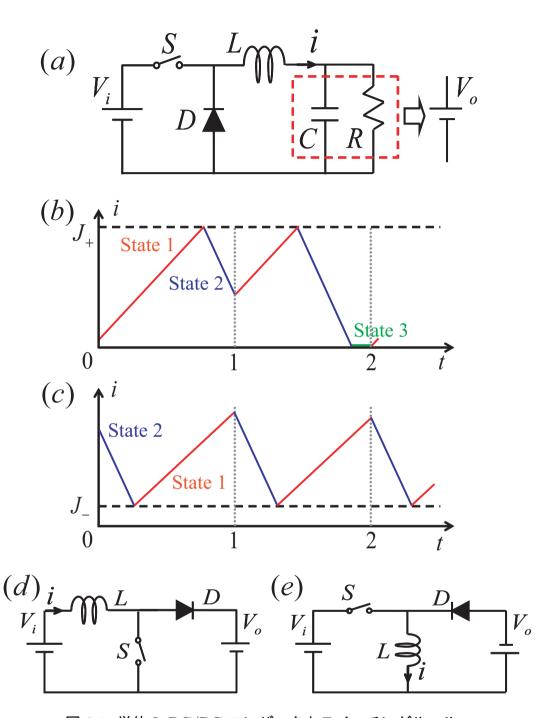

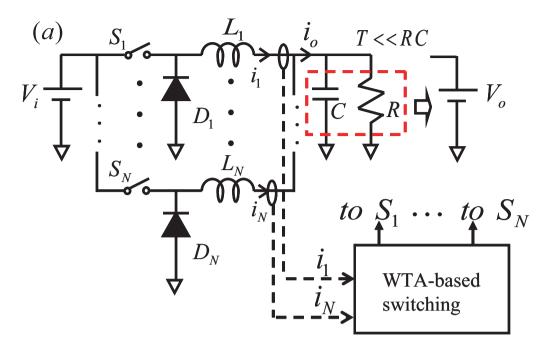

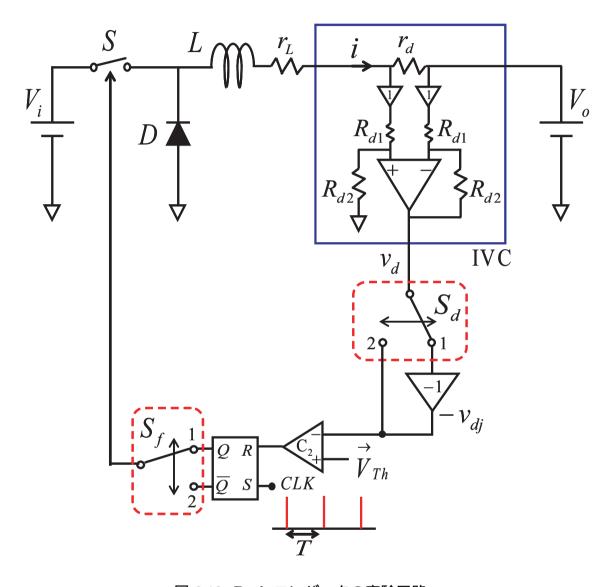

### 2.2 多入力系並列化 Buck コンバータの基本動作

図 2.1 (a) に多入力系 PDCs の回路モデルを示す。これは N 個  $(N \ge 2)$  の単体の Buck コンバータが並列に接続されており、出力電流は各々のコンバータに流れる電流 の総和  $i_o \equiv \sum_{j=1}^N i_j$  となる。また、全ての入力が等しい場合  $(V_1 = \cdots = V_N)$ 、このシステムは一入力系の PDCs に対応し、[23] の文献で研究されている。各々 (j 番目)の コンバータはスイッチ  $S_i$  とダイオード  $D_i$  により、以下の 3 つの状態をとる:

State 1:  $S_j$  conducting,  $D_j$  blocking and  $0 < i_j < J$

State 2:  $S_j$  blocking,  $D_j$  conducting and  $0 < i_j < J$

State 3:  $S_j$  and  $D_j$  both blocking and  $i_j = 0$

それぞれの状態へのスイッチングルールは以下のようになる:

State 1  $\rightarrow$  State 2 if  $i_i = J$

State 2  $\rightarrow$  State 3 if  $i_i = 0$

State 2 or State 3  $\rightarrow$  State 1 if  $i_i = \min$  at t = nT

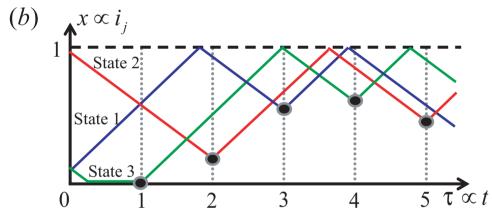

ここで、J はしきい値電流で、T はクロックである。 $State\ 1$  では電流は増加し、しきい値に達する  $(i_j=J)$  とスイッチ  $S_j$  は開き、 $State\ 2$  に切り替わり電流は減少する。そして電流が 0  $(i_j=0)$  となると  $State\ 3$  に切り替わる。 $State\ 1$  へのスイッチングはWTA を用いる: クロック毎 T=nt  $(n=0,1,2\cdots)$  に、ある j 番目のコンバータの電流 $i_j$  が他のコンバータの電流 $i_1 \sim i_N$  と比べ最小なら、そのコンバータのスイッチ  $S_j$  は閉じられ  $State\ 1$  に切り替わり、電流は増加する。このときの最小の電流 $i_j$  を Winner と定義する。 $State\ 3$  のコンバータ電流が複数ある場合、全てが Winner となり、T=ntで  $State\ 1$  に切り替わる。これらのスイッチングを図 2.1 (b) に示す。 $State\ 3$  を含まずに動作している場合を連続導通モード( $Continuous\ Conduction\ Mode:\ CCM$ )と呼び、 $State\ 3$  を含んで動作する場合を不連続導通モード( $Discontinuous\ Conduction\ Mode:\ DCM)と呼ぶ。$

簡単のため、クロック周期 T に対して時定数 RC が十分に大きい (RC >> T) という条件の下、負荷を定電圧源  $V_o$   $(V_o < V_j)$  と置き換えることができる (図 2.1 (a) $)。また、全てのコンバータの回路素子は理想的であり、<math>L_j = L$  と仮定する。回路方程式は

以下のように記述される:

$$L\frac{d}{dt}i_{j} = \begin{cases} V_{j} - V_{o} & \text{for State 1} \\ -V_{o} & \text{for State 2} \\ 0 & \text{for State 3} \end{cases}$$

(2.1)

これは PWC システムであり、呈する軌道は区分線形 (PWL) となる [6] [14] [23]。以下の無次元化変数とパラメータを導入すると、

$$\tau = \frac{t}{T}, \ x_j = \frac{i_j}{J}, \ a_j = \frac{T}{LJ}(V_j - V_o), \ b = \frac{T}{LJ}V_o$$

(2.2)

回路方程式は以下のように正規化される:

$$\frac{d}{d\tau}x_j = \begin{cases}

a_j & \text{for State 1} \\

-b & \text{for State 2} \\

0 & \text{for State 3}

\end{cases}$$

(2.3)

State  $1 \to \text{State 2 if } x_i = 1$

State 2  $\rightarrow$  State 3 if  $x_i = 0$

State 2 or State 3  $\rightarrow$  State 1 if  $x_i$  wins at  $\tau = n$

ここで、" $x_j$  wins" は  $x_j$  が他の値  $\{x_1,\cdots,x_N\}$  に比べ、最小であることを意味する。また、 $x_j$  は  $\tau \geq 0$  に対して  $0 \leq x_j \leq 1$  の範囲をとる。このシステムは N+1 個の正のパラメータ  $(a_1,\cdots,a_N,b)$  をもつ。ここで、 $a_j$  は j 番目のコンバータの  $State\ 1$  の傾き、b は  $State\ 2$  の傾きに対応する (図 2.1 (b))。そして  $a_j=a$  のときは、入力の等しい一入力系の PDCs に対応する [23]。ここで以下に3 つの定義をする。

定義 1: 各コンバータの状態の集合を  $m{x}=(x_1,\cdots,x_N)$  とする。式 2.3 が  $m{x}(\tau+N)=m{x}(\tau)$  を満たす周期 N の周期解であり、各コンバータは 1 周期の間  $0\leq \tau < N$  に 1 度 "Winner" となる。このとき、PDCs は N-相同期 (N-SYN) を呈する。

定義 2: N-相同期となる各コンバータの状態の集合を  $x_p=(x_{p1},\cdots,x_{pN})$  とする。  $x(\tau)$  が、小さな摂動  $\epsilon(0)$  を含む初期値  $x(0)=x_p(0)+\epsilon(0)$  に対して、時間が経過すると  $x_p(\tau)$  に収束する。このとき、N-SYN は初期値に対して安定である。また、  $x(0)=x_p(0)+\epsilon(0)$  が  $\tau>\tau_f$  ( $\tau_f$ : 有限時間) に対して  $x(\tau)=x_p(\tau)$  であるとき、N-SYN は初期値に対して超安定 (Superstable) である。

定義  $\mathbf{3}$ :  $\mathbf{x}(\tau+M)=\mathbf{x}(\tau)$  となる周期 M の周期解に対して、リップル  $R_p$  を以下のよ

うに求める。

$$R_p = (\max X(\tau) - \min X(\tau)) / \bar{X}(\tau)$$

(2.4)

ここで、 $0 \le \tau < M$ 、 $X(\tau) \equiv \sum_{j=1}^N x_j(\tau)$  は無次元の出力電流であり、 $\bar{X}(\tau)$  はそれらの平均の値である。

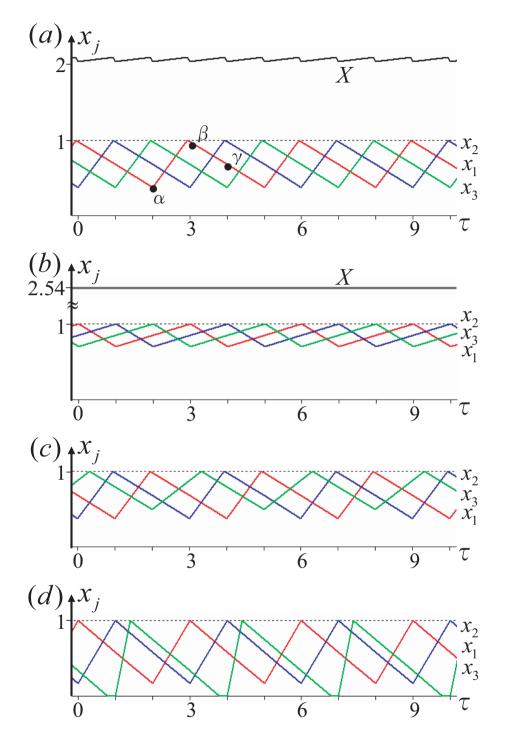

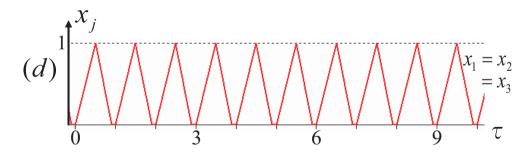

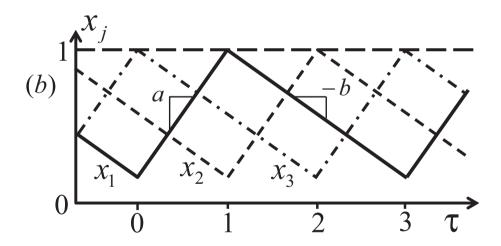

WTA スイッチングは自動的に N-SYN を実現でき、図 2.2 に N=3 のときの典型的な波形を示す。ここで、 $x_1$ 、 $x_2$ 、 $x_3$  は 1 周期  $n \le \tau < n+3$  の間に 1 度 "Winner"になる。図 2.2 (b) は入力が等しく  $a_1=a_2=a_3\equiv a$ 、かつ 2a=b or a=2b のとき、ゼロリップル  $R_p=0$  となる。1 つの入力  $a_3$ 、もしくは b を変化させると、3-SYN は図 2.2 (c)、(d) のようになる。このように図 2.1 (a) のモデルは一入力系の PDCs にも対応し、様々な波形を出力する。次章では、これらを解析するための手法について述べる。

図 2.1: 多入力系並列化 DC/DC コンバータ. (a) 回路モデル. (b) スイッチングルール (N = 3).

- 図 2.2: 3相同期の典型的な波形.

(a) Stable 3-SYN in CCM for  $a_1^{-1}=a_2^{-1}=a_3^{-1}=1.5$  and  $b^{-1}=3.3$  ( $R_p=0.03$ ).

(b) Unstable 3-SYN in CCM for  $a_1^{-1}=a_2^{-1}=a_3^{-1}=6.6$  and  $b^{-1}=3.3$  ( $R_p=0$ ).

(c) Distorted 3-SYN in CCM for  $a_1^{-1}=a_2^{-1}=1.5$ ,  $a_3^{-1}=2.6$  and  $b^{-1}=3.3$  ( $R_p=0.13$ ).

(d) Distorted 3-SYN in DCM for  $a_1^{-1}=a_2^{-1}=1.2$ ,  $a_3^{-1}=0.4$ ,  $b^{-1}=2.4$  ( $R_p=0.46$ ).

### 2.3 Hybrid Return Map

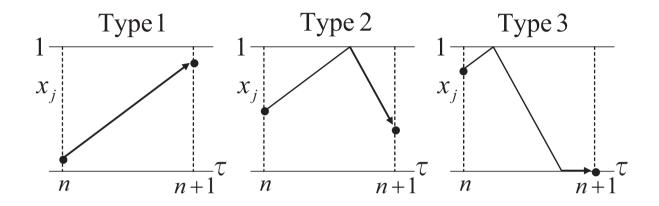

本章ではシステムの呈する現象を調べるために、Hybrid Return Map (HRM) を導出する [32]。HRM はクロック  $\tau=n$  毎にサンプリングされた状態を示す。状態  $x_j(\tau)$  と軌道の傾きを示す  $\mathrm{sgn}(\dot{x}_j(\tau))\equiv s_j(\tau)$  は、時間 n の関数で表される。ここで、連続時間  $n\leq \tau < n+1$  の  $x_j$  の軌道を図 2.3 に示すように、次の 5 つに分類する:

Type 1:  $x_j$  がしきい値 x=1 に到達することなく増加する (CCM)。 $a_j^{-1}>1,\ 0\le x_j(n)<\alpha_j$  and  $s_j(n)=1$  のとき  $(\alpha_j\equiv 1-a_j)$ 。このとき、次のような差分方程式が得られる。

$$x_j(n+1) = x_j(n) + a_j, \ s_j(n+1) = 1$$

(2.5)

Type 2:  $x_j$  は増加し、しきい値に達して減少する。x=0 には到達しない ( CCM )。  $a_i^{-1}+b^{-1}>1,\ \alpha_j\leq x_j(n)<\beta_j\ {\rm and}\ s_j(n)=1$  のとき  $(\beta_j\equiv 1-a_j+a_j/b)$ 。

$$x_j(n+1) = -p_j x_j(n) + q_j$$

$$s_j(n+1) = \begin{cases} 1 & \text{if } x_j(n+1) \text{ wins} \\ -1 & \text{otherwise} \end{cases}$$

(2.6)

ここで、 $p_j \equiv b/a_j$  and  $q_j \equiv 1 - b + p_j$ 。

Type 3:  $x_j$  は増加し、しきい値に達して減少し、x=0 となる ( DCM )。  $b^{-1}<1$ ,  $\beta_j \leq x_j(n)$  and  $s_j(n)=1$  のとき。

$$x_j(n+1) = 0, \ s_j(n+1) = 1$$

(2.7)

Type 4:  $x_i$  は減少し、x=0 となる (DCM)。  $0 \le x_i(n) \le b$  and  $s_i(n)=-1$  のとき。

$$x_j(n+1) = 0, \ s_j(n+1) = 1$$

(2.8)

**Type 5**:  $x_j$  は減少し、x=0 には到達しない ( CCM )。 $b^{-1}>1,\ b< x_j(n)$  and  $s_j(n)=-1$  のとき。

$$x_j(n+1) = x_j(n) - b$$

$$s_j(n+1) = \begin{cases} 1 & \text{if } x_j(n+1) \text{ wins} \\ -1 & \text{otherwise} \end{cases}$$

(2.9)

HRM は j 番目のコンバータにおいて、横軸  $x_j(n)$  は時間 n の状態、縦軸  $x_j(n+1)$  は次の状態を表し、 $x_j(n+1)=f_j(x_j(n),s_j(n))$  and  $s_j(n+1)=g_j(\boldsymbol{x}(n),s_j(n)), j=1\sim N$

で記述される。Type 2 と 5 では、 $s_i(n+1)$  の値は WTA スイッチングにより、他のコ ンバータの状態よってきまる:  $x_i(n+1)$  が "Winner" であれば、 $s_i(n+1) = 1$  となる。  ${

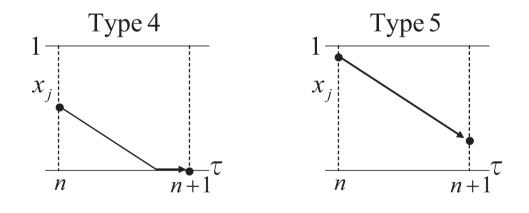

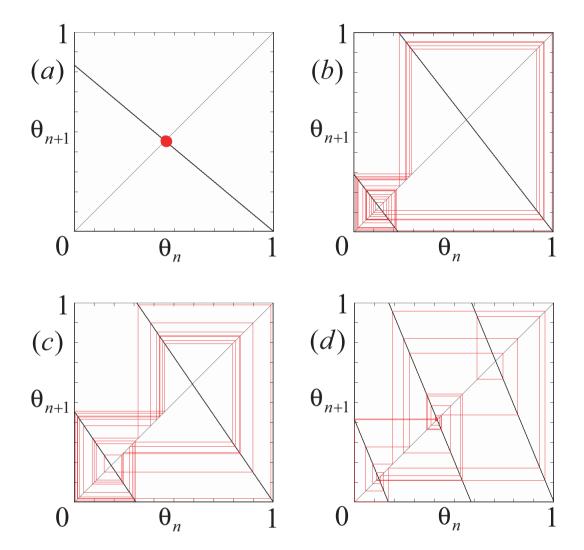

m HRM}$  はパラメータに依存して様々な形となる。はじめに、 $a_i^{-1}>1$  and  $b^{-1}>1$  に ついて考える。この場合 Type 1、Type 2、Type 4、Type 5 が考えられ、 $f_j$  は図 2.4に示されるような形となる:  $f_i$  は  $B_1$ 、 $B_2$ 、 $B_4$ 、 $B_5$  の 4 つの枝をもち、それらは Type 1、2、4、5 にそれぞれ対応する。このような HRM を Class A とし、後で言及する。 全ての  $x_i(n)$  に対して上側と下側の 2 本の枝が存在し、マップ上の軌道がどちらの枝 を打つのかは式 2.5 から 2.9 の  $s_j(n)$  によってきめられる:  $s_j(n)=1$  ならば上側の  $B_1$ or  $B_2$  の枝を打ち、 $s_i(n) = -1$  ならば下側の  $B_4$  or  $B_5$  の枝を打つ。 $x_i(n)$  が "Winner" でないときは、図  $2.4~(\mathrm{a})$  のように安定な周期点をもつ  $B_2$  を打った軌道は、 $B_5$  の枝を 打つ。図 2.4 (a) の軌道は図 2.2 (a) の 3-SYN に対応する。ここでは  $a_1=a_2=a_3=a$ であり、このとき  $x_2(n)$  と  $x_3(n)$  の HRM の形は同じになる。また、 $a_i \neq a$  ならば それぞれ独立した  ${

m HRM}$  となる。図  $2.4~({

m a})$  は  $x_1(n)$  の  ${

m HRM}$  であり、マップ上の点 lpha は au=n の "Winner" の値であり、eta と  $\gamma$  はそれ以外の au=n の値である。 $x_1(n)$ は  $\tau = n$  毎に  $B_2$ 、 $B_5$ 、 $B_5$  と枝に当たるため、時間波形は Type 2、 Type 5、 Type 5 となる。 $x_2$ 、 $x_3$  のマップは時間 1、2 遅れて、それぞれ  $x_1$  と同じ振る舞いをする。図 2.4 (a') は  $x_1$ - $x_2$ - $x_3$  空間に  $x_1(n)$ 、 $x_2(n)$ 、 $x_3(n)$  の値を直線で結んだ 3-D Plot である:  $(\alpha, \gamma, \beta), (\beta, \alpha, \gamma)$  and  $(\gamma, \beta, \alpha)$ 。それぞれのマップの軌道は、傾き  $-p_i$  と 1 の  $B_2$  と  $B_5$  の枝を打つ。 $B_2$  の枝は収縮的  $0 < p_j = b/a_j < 1$  なので、この  $3 ext{-SYN}$  は安定であ るといえる。 $a^{-1}$  が大きくなると  $B_2$  の枝の傾きは急 (拡大的) になっていき、3-SYNは不安定になっていく。一般的に  $N \geq 2$  の系に対して、定理1を用いる。

定理  $1: 1>N/(a^{-1}+b^{-1})$  ならば、CCM の N-SYN が存在する。N-SYN は  $b/a_j<1$  のとき、全ての j に対して安定であり、 $b/a_j>1$  のときはある j に対して不安定である。(これらについては 3 章で言及する)

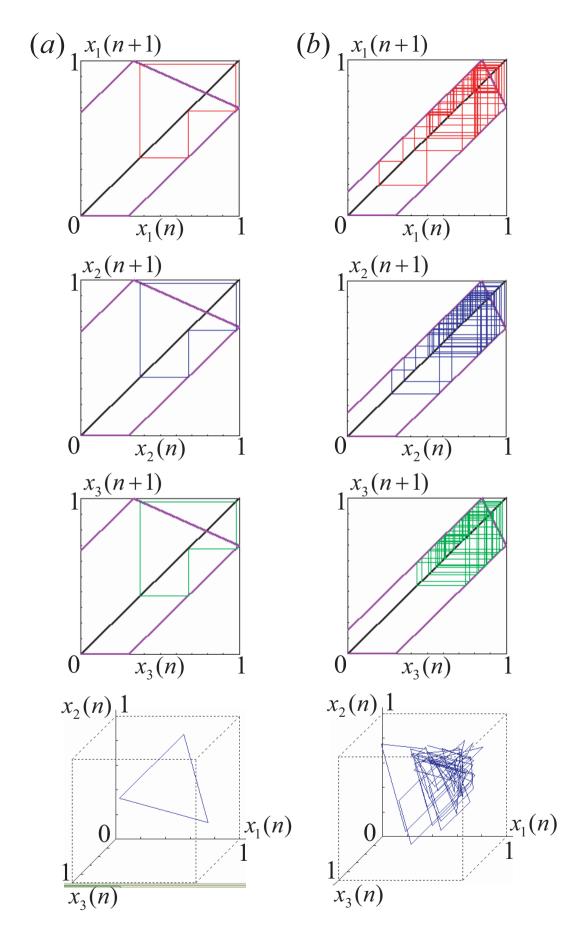

N-SYN は  $a_j^{-1}>b^{-1}$  となると安定性を失う。図 2.4 (b) の HRM の軌道は図 2.2 (b) の 3-SYN に対応する。ここで、 $B_2$  の枝は  $p_j>1$  と拡大率が大きいため、この 3-SYN

は不安定である。この不安定な 3-SYN を観測することはできず、実際は図 2.4 (c) と (c') のようなカオスの振る舞いをする。これらのカオスの軌道は傾きが 1、 $-p_j$ 、1 である  $B_1$ 、 $B_2$ 、 $B_5$  の枝を打つ。 $p_j > 1$  であるため、 $x_1$ 、 $x_2$ 、 $x_3$  ともに HRM の軌道は拡大的になる。2 つ以上の方向に拡大的となるカオスの軌道を Hyperchaos という。つまり図 2.4 (c') は Hyperchaos を示す。 Hyperchaos の詳細については [36] の文献で議論されている。 $p_j > 0$ 、 $x_j > 0$  ならば  $x_j$  は不安定であり、次のことがいえる。

定理 2:  $p_j=b/a_j>1$ 、 $x_j>0$  ならば、PDCs はある j に対してカオスを呈する。  $p_j=b/a_j>1$ 、 $x_j>0$  ならば、PDCs は 2 つ以上の j に対して Hyperchaos を呈する。

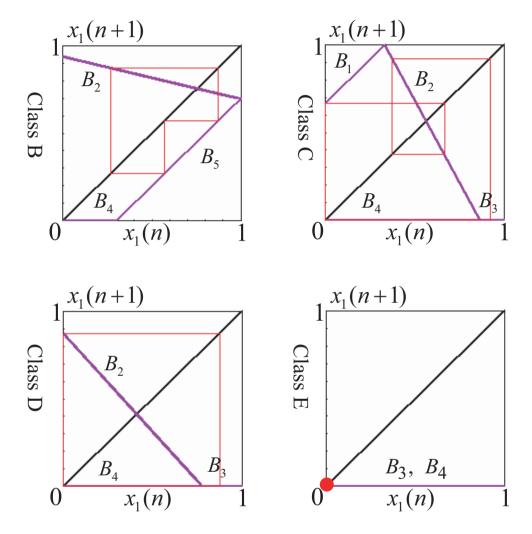

パラメータを変化させると  $\operatorname{HRM}$  は様々な形となる。パラメータの範囲によって、 $x_j$  成分  $f_i$  の形は次の 5 つの  $\operatorname{Class}$  に分類される:

Class A:  $a_j^{-1}>1$ ,  $b^{-1}>1$  で Type 1, 2, 4, 5 が存在し、図 2.4 に示されるように  $f_j$ は  $B_1$ ,  $B_2$ ,  $B_4$ ,  $B_5$  の 4 つの枝をからなる。

Class B:  $a_j^{-1} < 1$ ,  $b^{-1} > 1$  で Type 2, 4, 5 が存在し、 $f_j$  は  $B_2$ ,  $B_4$ ,  $B_5$  の 3 つの枝からなる。

Class C:  $a_j^{-1} > 1$ ,  $b^{-1} < 1$  で Type 1, 2, 3, 4 が存在し、 $f_j$  は  $B_1$ ,  $B_2$ ,  $B_3$ ,  $B_4$  の 4 つの枝からなる。

Class D:  $a_j^{-1} < 1$ ,  $b^{-1} < 1$ ,  $a_j^{-1} + b^{-1} > 1$  で Type 2, 3, 4 が存在し、 $f_j$  は  $B_2$ ,  $B_3$ ,  $B_4$  の 3 つの枝からなる。

Class E:  $a_j^{-1} + b^{-1} < 1$  で Type 3, 4 が存在し、 $f_j$  は  $B_3, B_4$  からなる。しかし全ての軌道は Type 3 になるので、 $f_j$  は  $B_3$  に対して考えれば十分である。

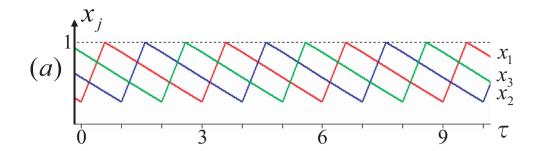

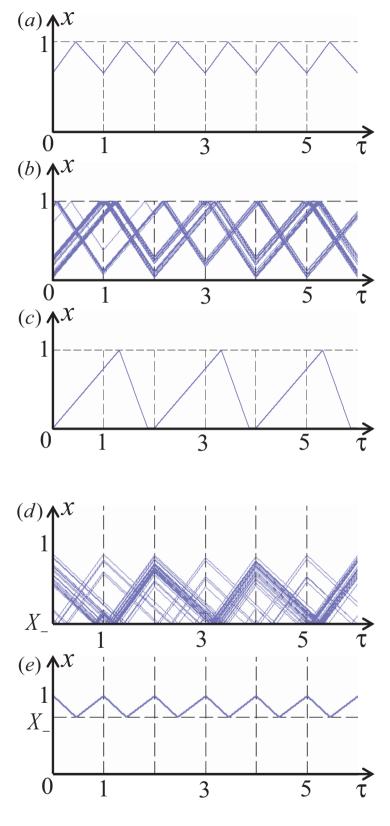

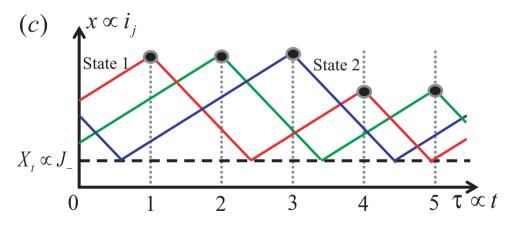

Class B から E までの典型的な HRM を図 2.5 に示す。HRM は 2 つのグループにわかれる:  $b^{-1} > 1$  では  $\{$  Class A, Class B  $\}$  に、 $b^{-1} < 1$  では  $\{$  Class C, Class D, Class E  $\}$  になる。図 2.5 Class B から E に対応した時間波形  $(a_j = a$  の場合)を図 2.6 に示す。

図 2.3: 5 種類の基本的な軌道.

Type 1, 2 and 3  $\text{Clim}(s_j(n)) = -1$   $(\dot{x}_j(n) > 0)$ . Type 4 and 5  $\text{Clim}(s_j(n)) = -1$   $(\dot{x}_j(n) < 0)$ .

■ 2.4: Hybrid return maps  $\succeq$  3D plots  $(N=3 \text{ and } a_1=a_2=a_3\equiv a)$ . (a) Stable 3-SYN for  $(a^{-1},b^{-1})=(1.5,3.3)$ , (b) Unstable 3-SYN for  $(a^{-1},b^{-1})=(6.6,3.3)$ , (c) Hyperchaos for  $(a^{-1},b^{-1})=(6.6,3.3)$ .

図 2.5: HRM の典型的な形. Class B:  $(a_1^{-1}, b^{-1}) = (0.8, 3.3)$ . Class C:  $(a_1^{-1}, b^{-1}) = (1.5, 0.8)$ . Class D:  $(a_1^{-1}, b^{-1}) = (0.9, 0.8)$ . Class E:  $(a_1^{-1}, b^{-1}) = (0.5, 0.4)$ .

図 2.6: 典型的な時間波形  $(N=3, a_1=a_2=a_3\equiv a)$ . (a)  $(a_1^{-1}, b^{-1})=(0.8, 3.3)$ . (b)  $(a_1^{-1}, b^{-1})=(1.5, 0.8)$ . (c)  $(a_1^{-1}, b^{-1})=(0.9, 0.8)$ . (d)  $(a_1^{-1}, b^{-1})=(0.5, 0.4)$ .

(a)

$$(a_1^{-1}, b^{-1}) = (0.8, 3.3).$$

(b)

$$(a_1^{-1}, b^{-1}) = (1.5, 0.8).$$

(c)

$$(a_1^{-1}, b^{-1}) = (0.9, 0.8)$$

(d)

$$(a_1^{-1}, b^{-1}) = (0.5, 0.4).$$

(a) から (d) は図 2.5 の Class B から Class E にそれぞれ対応する。(b) と (c) では  $x_1$  は  $x_3$ に重なり、(d) では  $x_1$  は  $x_2$  と  $x_3$  に重なる。これは DCM のときにのみ起こる。

### 2.4 PDCs の呈する分岐現象

本章では HRM と 3-D Plot を用いてシステムの呈する分岐現象を調べる。N=3 において、以下に基本的な 3 つの 1 パラメータ分岐を示し、考察する。

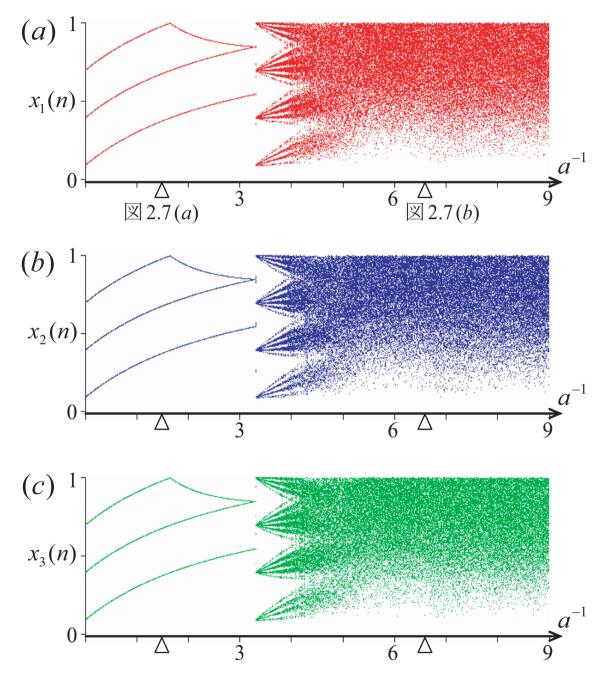

## 2.4.1 一入力系 $a_i = a$ の分岐 (CCM)

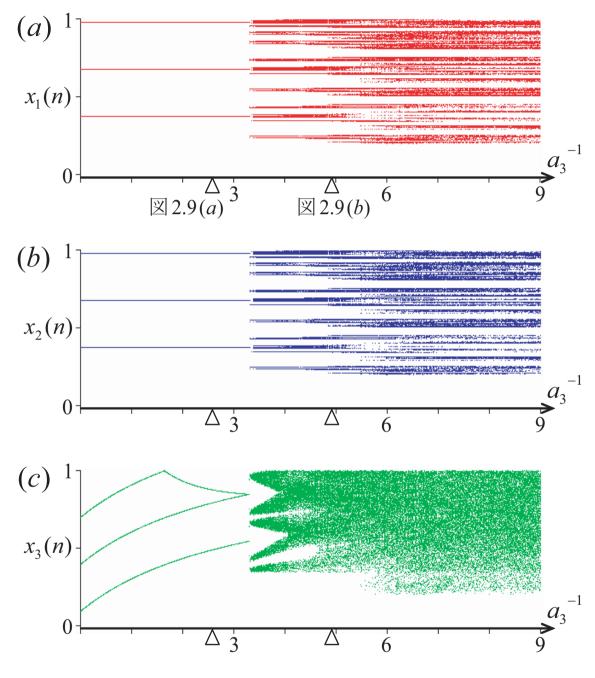

ここでは  $a_1=a_2=a_3\equiv a, b^{-1}=3.3$  とし、a を変化させたときの分岐について考察する。この場合、システムは入力は全て等しい一入力系に対応する。一入力系なので、図 2.7 に示されるように  $x_1$  から  $x_3$  のマップの形は全て同じになるため、 $x_1$  から  $x_3$  の分岐は同じ現象を呈する。図 2.8 に系の呈する分岐現象を示す。これらの分岐図は $x_1$  から  $x_3$  の HRM について  $a^{-1}$  が大きくなる度に、クロック毎  $\tau=n$  にプロットしたものである。安定な 3-SYN は  $a^{-1}$  が大きくなるにつれて不安定へと変わる。これはHRM の  $B_2$  傾き  $-p_j=-b/a$  が急になるからである。安定動作の境界は  $a^{-1}=b^{-1}$  であり、 $B_2$  の傾きは  $p_j<1$  (図 2.7 (a)) から  $1< p_j$  (図 2.7 (b)) となり、安定な 3-SYN は 2-SYN は

## 2.4.2 多入力系 $a_i \neq a$ の分岐 (CCM)

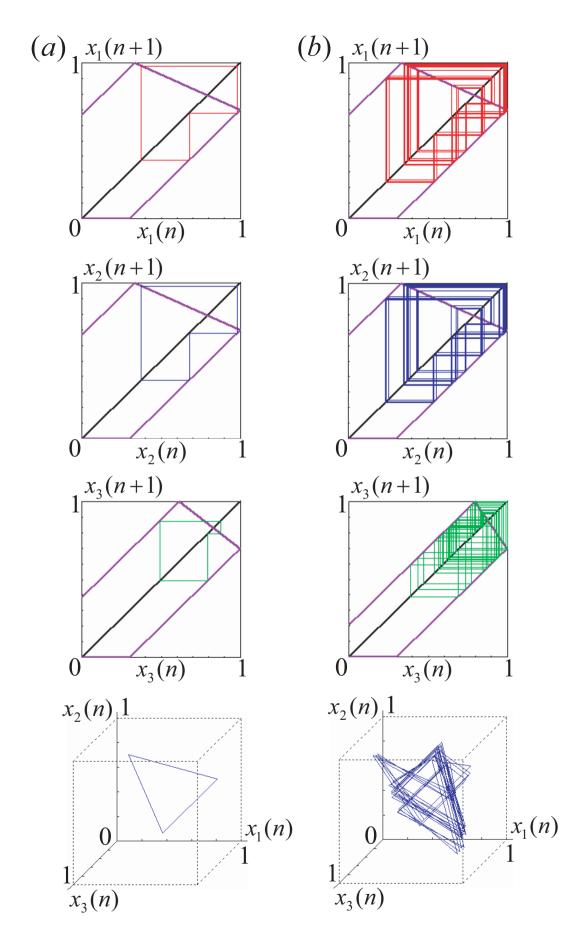

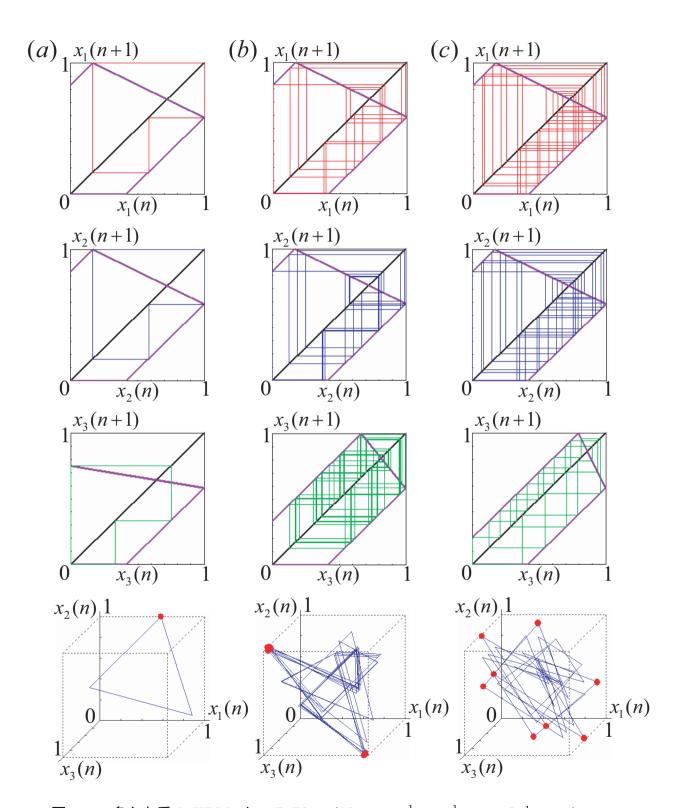

ここではパラメータを  $a_1^{-1}=a_2^{-1}=1.5$ ,  $b^{-1}=3.3$  と固定し、3 つ目のコンバータ $a_3^{-1}$  を変化させたときの分岐について考察する。この場合、3 つ目のコンバータの入力が異なる多入力系に対応する。 $a_3$  は 3 つ目のコンバータの直流の入力電圧  $V_3$  に比例している。つまり  $a_3$  を変化させたときの分岐は、入力電圧  $V_3$  が変化したときの現象に対応する。図 2.9 に、安定な 3-SYN (図 2.7 (a)) から  $a_3^{-1}$  のみ変化させたときの典型的な現象を示す。図 2.9 (a) の HRM と 3D Plot は図 2.2 (c) の Distorted 3-SYN の波形に対応する。

${

m HRM}$  において  $f_1$  から  $f_3$  は、全て  $B_1$ ,  $B_2$ ,  $B_4$ ,  $B_5$  の枝を含む  ${

m Class}$  A である。  $a_3^{-1}$  を変化させると  $f_3$  の形は変わるが、 $f_1$  と  $f_2$  の形は保たれている。しかし、 $x_3$  が  $a_3^{-1}>b^{-1}$  となるとそれに影響され、  $x_1$  と  $x_2$  の振る舞いは WTA Switching により、安定な 3-SYN からカオスの振る舞いへと図 2.9 (b) のように変わる。

図 2.10 (a) から (c) に  $x_1$  から  $x_3$  の分岐現象を示す。これらの分岐図は  $x_1$  から  $x_3$  の HRM について  $a_3^{-1}$  が大きくなる度に、クロック毎  $\tau=n$  にプロットしたものである。 $a_3^{-1}$  が大きくなると 3-SYN はゆがみ、 $a_3^{-1}$  が  $b^{-1}$  をこえると CCM のカオスに変わる。 $a_3^{-1}>b^{-1}$  では HRM は CCM のカオスの振る舞いを呈する。 $x_3$  に対しては  $B_2$  の枝は拡大的  $(p_3>1)$  であるが、 $x_1$  と  $x_2$  に対しては  $B_2$  の枝は収縮的  $(p_1=p_2<1)$  である。よってこのカオスの振る舞いでは  $x_3$  成分のみが拡大的である。 $p_1$  と  $p_2$  は  $p_2$  は  $p_3$  をこえないが、 $p_3$  がカオスの振る舞いであり WTA Switching によりその影響を受け、 $p_3$  は  $p_3$  は  $p_4$  は  $p_5$  は

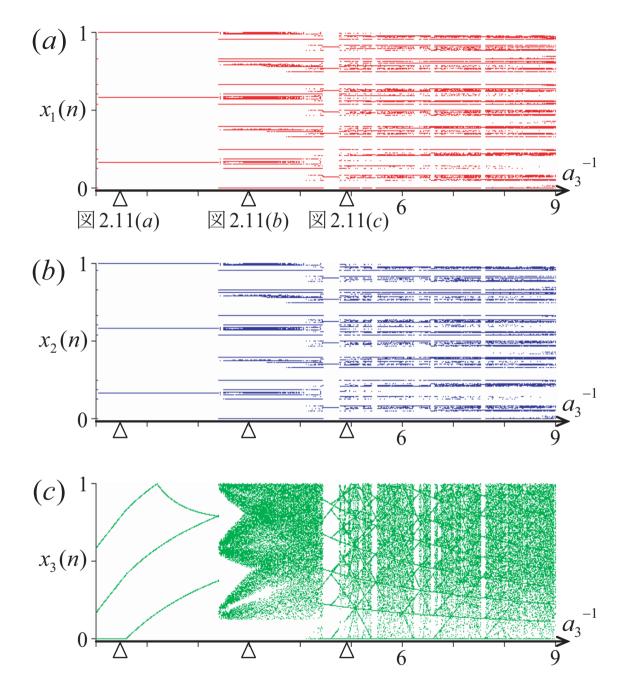

### 2.4.3 DCM を含む多入力系 $a_i \neq a$ の分岐

ここでは前章と同様に  $a_1^{-1}=a_2^{-1}=1.2,\,b^{-1}=2.4$  と固定し、 $a_3^{-1}$  に対する分岐について考察する。図 2.11 (a) は図 2.2 (d) の Distorted 3-SYN の波形に対応する。HRMにおいて  $f_1$  と  $f_2$  は Class A であるが、 $f_3$  は  $B_2$ ,  $B_4$ ,  $B_5$  の 3 つの枝を含む Class B である。 $x_3$  の軌道は傾き 0 の枝(Zero-slope) $B_4$  を打つため、DCM で超安定である。しかし、 $x_1$  と  $x_2$  は  $B_4$  の枝は打たず CCM である。図 2.11 の 3D Plot において、赤い・は  $x_3$  が  $B_4$  の枝を打った  $(x_3(n)=0)$  ことを意味する:DCM である印であり、超安定である。

$a_3^{-1}$  を大きくすると、この 3-SYN は図 2.11 (b) に示されるように  $x_1$  と  $x_2$  は超安定な現象、 $x_3$  はカオスへと変わる:  $x_1$  と  $x_2$  は  $B_4$  の枝を打ち、HRM は複雑で超安定な振る舞いを呈する。 $x_3$  は  $B_2$  の拡大的な枝  $p_3>1$  を打ち、 $B_4$  の枝を打たないためカオスである。更に  $a_3^{-1}$  を大きくすると、図 2.11 (c) の複雑な超安定な現象へと変わる:  $x_1$  から  $x_3$  は全て  $B_4$  の枝を打ち、HRM は複雑で超安定な振る舞いを呈する。数値実

験に関する限り、そのような振る舞いが周期的か非周期的かを判断することは難しい。 図 2.12 (a) から (c) に  $a_3^{-1}$  を大きくしたときの分岐現象を示す。DCM での 3-SYN は CCM での 3-SYN に変わり、そして CCM のカオスへと変わる。安定な 3-SYN と CCM でのカオスの境界は  $a_3^{-1}=b^{-1}=3.3$  であり、その移り変わりの様子は前章の図 2.8 と図 2.10 に似ている。更に  $a_3^{-1}$  を大きくすると CCM のカオスは様々な DCM で の超安定な現象へと変わる。それらは初期値に対しては超安定であるが、図 2.12 に示されるようにパラメータに対しては非常に敏感である。そのような超安定な振る舞い は単体のコンバータにおいては周期的である [6]。PDCs においてこのような "複雑な 超安定現象" を解析することは今後の課題である。

図 2.7: 一入力系の HRMs と 3-D Plots  $(N=3, a_1=a_2=a_3\equiv a, b^{-1}=3.3)$ . (a) Stable 3-SYN for  $a^{-1}=1.5$ . (b) Chaos for  $a^{-1}=6.6$ .

図 2.8: 一入力系の分岐現象  $(N=3,\,a_1=a_2=a_3\equiv a,\,b^{-1}=3.3).$  (a), (b), (c):  $x_1,\,x_2,\,x_3$  の分岐。

図 2.9: 多入力系の HRMs と 3-D Plots  $(N=3,\,a_1^{-1}=a_2^{-1}=1.5,\,b^{-1}=3.3).$  (a) Distorted 3-SYN for  $a_3^{-1}=2.6.$  (b) Chaos for  $a_3^{-1}=4.9.$

図 2.10: 多入力系の分岐現象  $(N=3,\,a_1^{-1}=a_2^{-1}=1.5,\,b^{-1}=3.3).$  (a), (b), (c):  $x_1,\,x_2,\,x_3$  の分岐。

図 2.11: 多入力系の HRMs と 3-D Plots  $(N=3,\,a_1^{-1}=a_2^{-1}=1.2,\,b^{-1}=2.4).$  (a) Distorted 3-SYN for  $a_3^{-1}=0.4.$  (b) Complicated superstable behavior and chaos for  $a_3^{-1}=3.0.$  (c) Complicated superstable behavior for  $a_3^{-1}=4.9.$

図 2.12: 多入力系の分岐現象  $(N=3,\,a_1^{-1}=a_2^{-1}=1.2,\,b^{-1}=2.4).$  (a), (b), (c):  $x_1,\,x_2,\,x_3$  の分岐。

#### 2.5 むすび

本章では一入力/多入力系 PDCs の区分定数 (PWC) モデルを提案した。現象解析のために Hybrid Return Map (HRM) を導出し、N=3 において典型的な分岐現象について考察した。パラメータを変化させると HRM は様々な形 (Class A から Class E) となり  $B_2$  の枝の傾き  $p_i$  に依存し、それぞれの系において多彩な現象を呈する。

一入力系 PDCs: 安定な N-SYN  $(p_j < 1)$  から  $a^{-1} = b^{-1}$  を境界に、CCM での Hyperchaos  $(p_j > 1)$  に変わる。

多入力系 PDCs:  $a_3^{-1}$  のみ変化させる。CCM の分岐では、安定な N-SYN はカオス  $(p_1=p_2<1,\,p_3>1)$  へと変わる。DCM の分岐では、安定な N-SYN は カオスへと 変わり、さらに複雑な超安定周期解 (SSPOs) に変わる。このように 3 つ目のコンバータが不安定な動作をすると、WTA Switching により影響を受け、他のコンバータも不 安定な現象へと変わり多彩な現象を引き起こす。

これらの結果は実際の回路設計や新しい分岐理論の発展に対する重要な情報となる。

今後の課題は、詳細な分岐現象の解析、PWC モデルと RC 負荷を用いた実際のモデルとの比較、多入力系の回路実験等が挙げられる。

# 第3章 2スイッチングルールを用いた 系の安定動作化

## 3.1 まえがき

本章では、2章で示されるようなパラメータに対する不安定な振る舞いに対して、2 つのスイッチングルールを適用し幅広いパラメータ領域での系の安定化を図る。単体と 並列の系の両方において考察する。はじめに単体の DC/DC コンバータにおいて回路 のダイナミクスを区分線形 (PWC) モデルに簡単にする [6]。Buck, Boost, Buck-Boost コンバータのそれぞれに対して、適切な無次元化変数とパラメータを導入すると、それ ぞれのコンバータを同様に考えることができる [14]。 スイッチングには 2 つのスイッチ ングルールを適用する。系の呈する現象を解析するために、2章のマップとは異なる位 相マップを導出する。このマップは1次元であり区分線形 (PWL) である。また系の安 定性やカオス現象を解析するために有効である。そしてそれぞれのスイッチングルー ルにおいてパラメータに対する安定な不動点の領域を明らかにする。次に N 個のコン バータを並列に接続した並列化 DC/DC コンバータ (PDCs) について考察する。単体 と同様に PWC モデルを適用し、位相制御には WTA Switching を用いる [23]。 PDCs は2章でも述べたように多相同期 (N-SYN) を実現できる。並列な系においても、安定 な N-SYN を実現するために 2 つのスイッチングルールを適用する。そしてそれぞれの スイッチングルールにおいてパラメータに対する N-SYN の安定な領域を明らかにす る。最後に、単体と並列の系に対してそれぞれ簡素な回路を実装し、現象の確認をす る。スイッチングルールを適切に切り替えることで、幅広いパラメータ領域で安定な 動作を呈することで安定化を図れる。

これらの内容は、文献 [34] [35] をまとめたものである。

# 3.2 単体の DC/DC コンバータ

# 3.2.1 回路モデルと基本動作

図 3.1 (a) に Buck コンバータの回路モデルを示す。この系はスイッチ S とダイオード D により、2 章のシステムと同様に以下の 3 つの状態をとる:

State 1: S conducting, D blocking and 0 < i

State 2: S blocking, D conducting and 0 < i

State 3: S and D both blocking and i = 0

このシステムでは2つのスイッチングルールを用いる。

Rule 1 (Fig. 3.1 (b) ): State 1 ではスイッチ S が on でコイルに流れる電流 i は増加する。そして上側のしきい値電流  $J_+>0$  に到達するとスイッチ S は off、そしてダイオード D は on となり State 2 に切り替わる。State 2 では電流 i は減少する。電流 i が 0 に到達すると State 3 となり、ここではスイッチ S とダイオード D は両方とも off となる。State 2 or 3 では次のクロックパルス (周期 T) により、スイッチ S が on、ダイオード D は off となり、State 1 で電流 i は増加する。2 章と同様、回路の動作が State 3 を含んで動作する場合を不連続導通モード (Discontinuous Conduction Mode: DCM) と呼び、State 3 を含まずに動作している場合を連続導通モード (Continuous Conduction Mode: CCM) と呼ぶ。全ての回路素子が理想的とすると、スイッチングルールは以下のように記述できる:

State 1  $\rightarrow$  State 2: when  $i = J_+$ State 2  $\rightarrow$  State 3: when i = 0

State 2 or  $3 \rightarrow$  State 1: when t = nT

Rule 2 (Fig. 3.1 (c) ): State 2 ではスイッチ S は off であり、i は減少する。そして下側のしきい値電流  $J_->0$  に到達するとスイッチ S は on、ダイオード D は off となり State 1 に切り替わる。State 1 では i は増加し、次のクロックパルスにより S は off、D は on となり State 2 に切り替わる。Rule 2 では下側のしきい値  $J_-$  により i は 0 には到達しないため State 3 は存在しない。スイッチングルールは以下のように記述できる:

State 2  $\rightarrow$  State 1: when  $i = J_{-}$

State  $1 \to \text{State } 2$ : when t = nT

ここでクロックの周期 T がコンバータの負荷の時定数 RC に比べ非常に小さい場合 (T<< RC)、図 3.1 (a) の様に負荷を定電圧源  $V_o$  として考えることができる [6]。そして回路方程式は以下のようになる:

$$L\frac{di}{dt} = \begin{cases} V_i - V_o & \text{for State 1} \\ -V_o & \text{for State 2} \\ 0 & \text{for State 3} \end{cases}$$

(3.1)

ここで  $V_i > V_o$  である。このような PWC (区分定数) システムは PWL (区分線形) な解をもち、系の解析が容易である。以下の無次元化変数とパラメータを導入すると、

$$\tau = \frac{t}{T}, \ x = \frac{i}{J_{+}}, \ a = \frac{T}{LJ_{+}}(V_{i} - V_{o}), \ b = \frac{T}{LJ_{+}}V_{o}, \ X_{-} = \frac{J_{-}}{J_{+}}.$$

(3.2)

回路方程式は以下のように正規化され、スイッチングルールは以下のようになる:

$$\frac{dx}{d\tau} = \begin{cases}

a & \text{for State 1} \\

-b & \text{for State 2} \\

0 & \text{for State 3}

\end{cases}$$

(3.3)

#### Rule 1:

State 1  $\rightarrow$  State 2 when x = 1

State 2  $\rightarrow$  State 3 when x = 0

State 2 or State 3  $\rightarrow$  State 1 when  $\tau = n$

#### Rule 2:

State 2  $\rightarrow$  State 1 when  $x = X_{-}$

State 1  $\rightarrow$  State 2 when  $\tau = n$

図 3.1 (d), (e) は Boost コンバータと Buck-Boost コンバータの PWC モデルである。これらのモデルは Buck コンバータと同じスイッチングルールをもち、Boost コンバータにおいては  $a=(T/LJ_+)V_i$ ,  $b=(T/LJ_+)(V_o-V_i)$ 、Buck-Boost コンバータにおいては  $a=(T/LJ_+)$ , $b=(T/LJ_+)$  とすると、同様の無次元化されたパラメータでシステムを解析できる。Buck コンバータを含んだこれらのコンバータに基づく PWC モデルの 6 つのパラメータ  $(T,L,J_+,J_-,V_i,V_o)$  は、3 つの無次元のパラメータ a>0,b>0, $X_-\geq 0$  に統合される。ここで、a は State 1 の傾き、b は State 2 の傾き、 $X_-$  は下側のしきい値に対応する(図 3.1 (b), (c))。

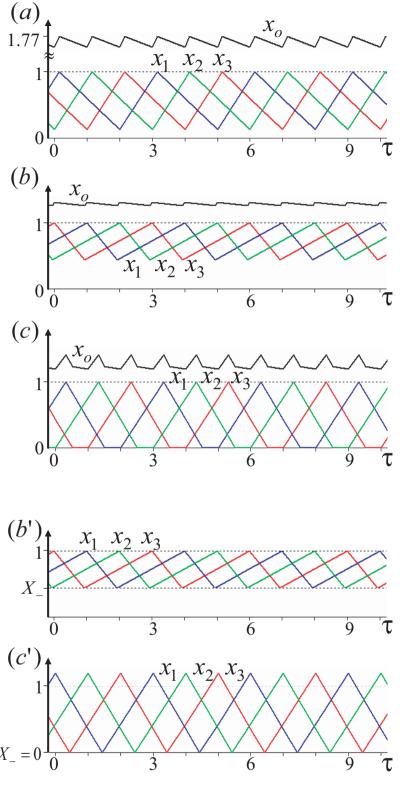

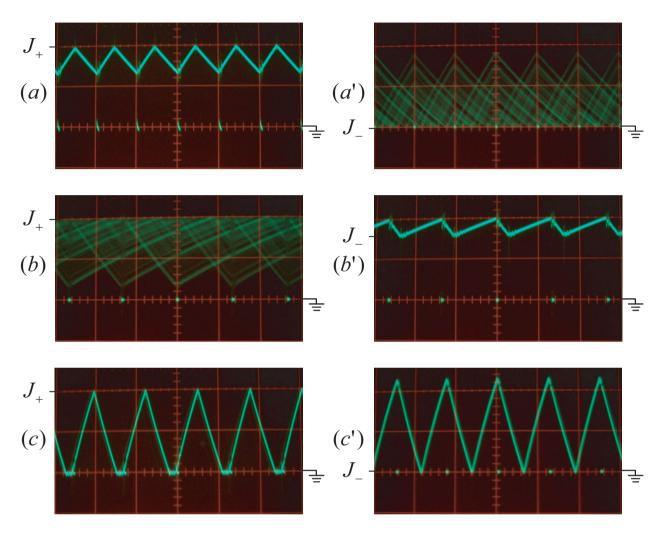

図 3.2 (a) から (c) に Rule 1 の典型的な波形を示す:  $b^{-1}$  を小さくすると CCM での周期軌道はカオスの軌道に変わり、そして DCM の周期軌道に変わる。この DCM で

の動作は、 $State\ 3$  での全ての軌道は時間 m 前に x=0 から増加し、時間 m 後に同様に x=0 から増加するため、初期値に対して強い安定性をもつ。図 3.2 (d), (e) に Rule 2 の典型的な波形を示す:  $a^{-1}$  を大きくするとカオスの軌道は CCM での周期軌道に変わる。 Rule 1 において、パラメータ (a,b) に対して CCM での周期的なアトラクタを呈するときには、Rule 2 では同パラメータ  $(X_- \ge 0)$  に関係なく)ではカオス的なアトラクタを呈する。また Rule 1 において、あるパラメータ (a,b) に対してカオス的なアトラクタを呈するときには、Rule 2 では CCM での周期的なアトラクタを呈する。

次章ではこのシステムの呈する現象を解析するために位相マップを導出し、分岐現象を調べる。そしてそれぞれの Rule に対する系の安定性について言及する。

図 3.1: 単体の DC/DC コンバータとスイッチングルール.

- (a) Buck コンバータの回路モデル  $(0 < V_o < V_i)$ .

- (b) Rule 1 のスイッチングルール.

- (c) Rule 2 のスイッチングルール.

- (d) Boost コンバータの PWC モデル  $(0 < V_i < V_o)$ .

- (e) Buck-Boost コンバータの PWC モデル  $(0 < V_i, 0 < V_o)$ .

図 3.2: 単体のコンバータの典型的な波形. (a) Periodic orbit in Rule 1 for  $(a^{-1},b^{-1})=(1.32,1.58)$ . (b) Chaotic orbit in Rule 1 for  $(a^{-1}, b^{-1}) = (1.32, 1.02)$  (overlapped drawing). (c) Periodic orbit in DCM in Rule 1 for  $(a^{-1}, b^{-1}) = (1.32, 0.55)$ . (d) Chaotic orbit in Rule 2 for  $(a^{-1}, b^{-1}) = (1.14, 1.66)$  and  $X_{-} = 0$  (overlapped drawing). (e) Periodic orbit in Rule 2 for  $(a^{-1}, b^{-1}) = (2.00, 1.66)$  and  $X_{-} = 0.72.$

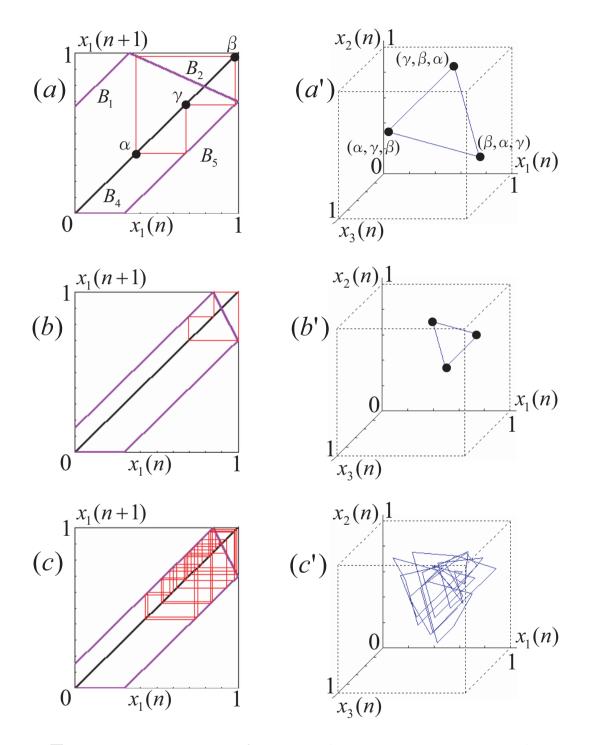

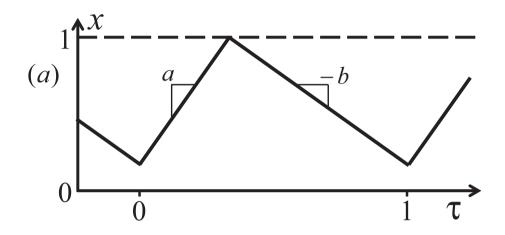

## 3.2.2 位相マップと系の安定性

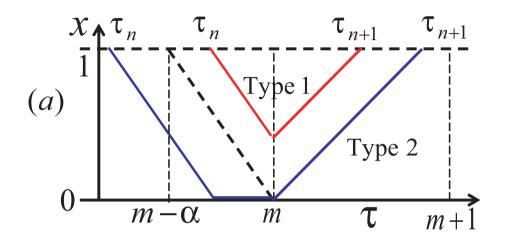

系の安定性と動作の解析のために位相マップを導出する [35]。図 3.3 にマップを導出するために、その例としてある区間  $m-1<\tau\le m+1$  における軌道を示す。時間 nで状態 x がしきい値に到達する時間を  $\tau_n$  とする。Rule 1 では時間  $\tau_n$  で上側のしきい値 1 に到達し、State 1 は State 2 に変わり状態 x は減少する。Rule 2 では時間  $\tau_n$  で下側のしきい値  $X_-$  に到達し、State 2 は State 1 に変わり状態 x は増加する。 $\tau_n$  は次のしきい値に到達する時間  $\tau_{n+1}$  を決めるため、1 次元マップ  $\tau_{n+1}=F(\tau_n)$  を定義できる。ここで位相変数  $\theta_n=\tau_n \mod 1$  を導入すると、 $I\equiv [0,1)$  から I への写像として次のように記述できる:

$$\theta_{n+1} = f(\theta_n) \equiv F(\theta_n) \mod 1$$

(3.4)

Rule 1 において  $\tau_n < \tau < \tau_{n+1}$  では 2 つのタイプの軌道が存在する (図 3.3 (a))。 Type 1: 状態 x は x=0 には到達しない。 Type 2: 状態 x は x=0 に到達する (DCM となる)。  $\alpha \equiv 1-b^{-1}>0$  ならば 2 つのタイプが存在し、位相マップは式 3.4 と 3.5 により記述される。

$$F(\theta_n) = \begin{cases} -p_1(\theta_n - 1) + 1 & \text{for } \alpha < \theta_n \le 1\\ a^{-1} + 1 & \text{for } 0 < \theta_n \le \alpha \end{cases}$$

(3.5)

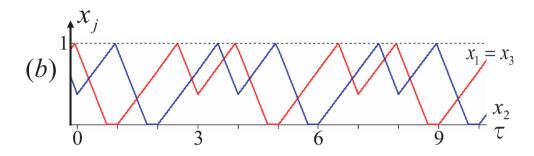

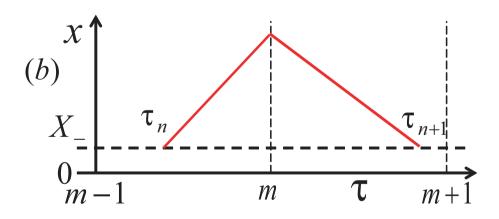

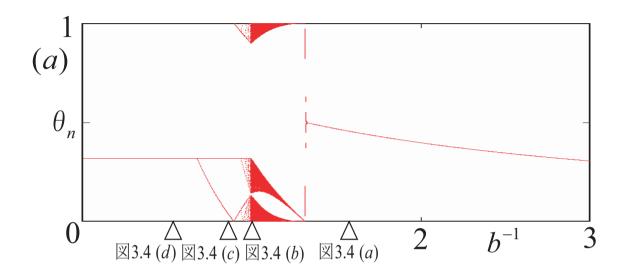

ここで  $p_1 \equiv b/a$  である。 $Type\ 1$  のマップは  $p_1$  によってのみきめられ、 $Type\ 2$  に対してはマップは傾き 0 の "Zero-slope" をもつ。図 3.4 に  $Rule\ 1$  の典型的な位相マップを示す。

Rule 2 において  $\tau_n < \tau < \tau_{n+1}$  では軌道は下側のしきい値  $x = X_-$  から増加し、クロック T により State 1 から State 2 に変わり、そして  $x = X_-$  に戻ってくる。State 3 は存在せず、位相マップは 3.4 と 3.6 により記述される。

$$F(\theta_n) = -p_2(\theta_n - 1) + 1 \tag{3.6}$$

ここで  $p_2 \equiv a/b$  (式  $3.5~p_1$  の逆数) である。図 3.5 に Rule 2 の典型的な位相マップを示す。これらの位相マップは、クロック T 毎に状態をサンプルしたマップ [6] よりシンプルである。ダイナミクスを考察するために以下に定義を記す。

定義 4: 区間  $1 \le l < k$  に対して  $x_p = f^k(x_p)$  and  $x_p \ne f^l(x_p)$  ならば、 $x_p$  は k-周期点である。ここで  $f^l(x_p) = f(f^{l-1}(x_p))$  and  $f^0(x) \equiv x$  。 1 周期点は不動点である。k-周期点の数列  $\{f(x_p), \cdots, f^k(x_p)\}$  を k-周期軌道という。周期軌道はそれぞれ初期値に対して  $|Df^k(x_p)| > 1$  ならば不安定、  $|Df^k(x_p)| < 1$  ならば安定、 $Df^k(x_p) = 0$  ならば超安定 (Superstable) である。ここで  $Df^k(x_p)$  は  $x_p$  での  $f^k$  の傾きである。

定義 5: 正の整数 l が存在するなら、 $|Df^l(x_0)| > 1$  は全ての  $x_0 \in I$  に対して満たされる。そして f は拡大的であり、安定な周期点をもたない。この場合 f のリヤプノフ指数は正であり、カオスといわれる [37]。

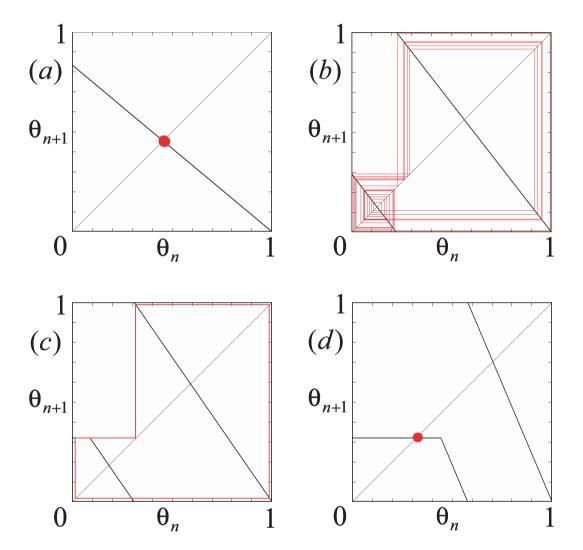

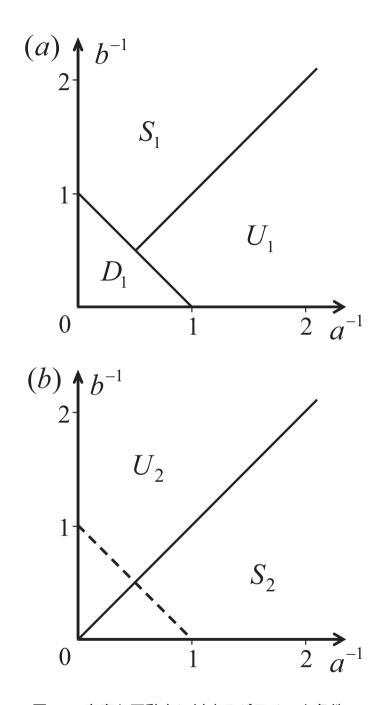

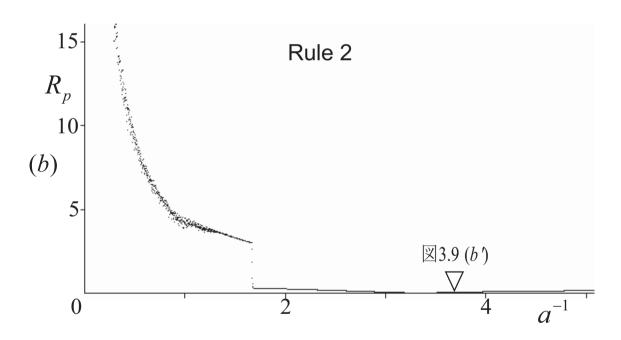

Rule 1 では図 3.4 (a), (b), (d) の位相マップは図 3.2 (a), (b), (c) の出力波形に対応する。 $a^{-1} < b^{-1}$  ならばリターンマップは収縮的な傾き  $0 < p_1 < 1$  の枝をもち、図 3.4 (a) に示されるような安定な不動点をもつ。 $a^{-1} > b^{-1}$  ならばマップは拡大的な傾き  $p_1 > 1$  の枝をもち、図 3.4 (b) のようにカオスを呈する。 $a^{-1} < 1 - b^{-1} \equiv \alpha$  ならばマップは図 3.4 (d) のように超安定な不動点をもつ。 $0 < 1 - b^{-1}$  ならばマップは Zero-slope をもち(図 3.4 (c))、様々な超安定周期解(Superstable Periodic Orbits: SSPOs)を呈する。これは初期値に対しては超安定だが、パラメータに対しては敏感である。実際にシステムにおいてはそのような SSPOs を観測することは難しい。なぜならマップの軌道は "Zero-slope branch" に到達するまでの長い間拡大的であり、実際のシステムでは Zero-slope は実現できないからである。SSPOs についての詳細については文献 [6] で議論している。図 3.6 (a) に Rule 1 の分岐図を示す。パラメータ  $b^{-1}$  を小さくすると CCM での周期的な軌道は  $b^{-1} = a^{-1}$  でカオスの軌道へと変わり、更に  $b^{-1} = 1$  で SSPOs へと変わる。 $b^{-1} = a^{-1}$  は安定性の境界であり、 $a^{-1} + b^{-1} = 1$  は不動点に対して超安定となる境界である。以下に 3 つの基本的なパラメータ領域を示す(図 3.7 (a)):

$$S_{1} \equiv \{(a,b) | a^{-1} + b^{-1} > 1, a^{-1} < b^{-1} \}$$

$$U_{1} \equiv \{(a,b) | a^{-1} + b^{-1} > 1, a^{-1} > b^{-1} \}$$

$$D_{1} \equiv \{(a,b) | a^{-1} + b^{-1} < 1 \}$$

(3.7)

ここで $S_1$ では不動点は安定、 $U_1$ では不安定、 $D_1$ では超安定である。

Rule 2 では図 3.5 (a), (c) の位相マップは図 3.2 (e), (d) の出力波形に対応する。  $a^{-1}>b^{-1}$  ならばマップは収縮的な傾き  $0< p_2<1$  の枝をもち、図 3.5 (a) に示され

るように不動点は安定である。 $a^{-1} < b^{-1}$  ならばマップは拡大的な傾き  $p_2 > 1$  の枝をもち、不動点は不安定である。この場合、図 3.5 (b), (c), (d) に示されるようにカオスを呈する。これに対応した分岐図を図 3.6 (b) に示す。パラメータ  $a^{-1}$  を小さくすると CCM での周期的な軌道は  $b^{-1} = a^{-1}$  でカオスの軌道へと変わる。以下に 2 つの基本的なパラメータ領域を示す(図 3.7 (b)):

$$S_2 \equiv \{(a,b) | a^{-1} > b^{-1}, \}$$

$$U_2 \equiv \{(a,b) | a^{-1} < b^{-1}, \}$$

(3.8)

ここで $S_2$ では不動点は安定、 $U_2$ では不安定である。

Rule 1 と Rule 2 のパラメータ領域において、 $U_1$  と  $U_2$  はカオスを呈する。 $a^{-1}+b^{-1}>1$  に対しては  $S_1$  の領域と  $S_2$  の領域は逆の関係である。また  $a^{-1}+b^{-1}>1$  のパラメータ領域は、回路のパラメータ  $LJ_+V_i/(V_o(V_i-V_o))>T$  と等価である:  $a^{-1}< b^{-1}$  に対しては Rule 1 を、 $a^{-1}>b^{-1}$  に対しては Rule 2 を適応すると、幅広いパラメータ領域において安定な CCM の出力を得ることができ、系の安定化を図れる。

次章では Buck コンバータを並列に接続した PDCs のシステムにおいて、多相同期 (N-SYN) の安定性について言及し、同様に系の安定化を図る。

図 3.3: 出力波形の軌道. (a) Rule 1. (b) Rule 2.

- 図 3.4: Rule 1 の位相マップ.

(a) Stable fixed point  $(p_1 = 0.83)$  for  $(a^{-1}, b^{-1}) = (1.32, 1.58)$ .

(b) Chaos  $(p_1 = 1.29)$  for  $(a^{-1}, b^{-1}) = (1.32, 1.02)$ .

(c) SSPO  $(p_1 = 1.45)$  for  $(a^{-1}, b^{-1}) = (1.32, 0.91)$ .

(d) SSPO  $(p_1 = 2.40)$  for  $(a^{-1}, b^{-1}) = (1.32, 0.55)$ .

- 図 3.5: Rule 2 の位相マップ.

(a) Stable fixed point  $(p_2 = 0.83)$  for  $(a^{-1}, b^{-1}) = (2.00, 1.66)$ .

(b) Chaos  $(p_2 = 1.29)$  for  $(a^{-1}, b^{-1}) = (1.29, 1.66)$ .

(c) Chaos  $(p_2 = 1.45)$  for  $(a^{-1}, b^{-1}) = (1.14, 1.66)$ .

(d) Chaos  $(p_2 = 2.40)$  for  $(a^{-1}, b^{-1}) = (0.69, 1.66)$ .

図 3.6: 典型的な分岐現象. (a) Rule 1 for  $a^{-1}=1.32$ . (b) Rule 2 for  $b^{-1}=1.66$ .

図 3.7: 安定な不動点に対するパラメータ条件. (a) Rule 1.  $S_1$ : stable,  $U_1$ : unstable,  $D_1$ : superstable. (b) Rule 2.  $S_2$ : stable,  $U_2$ : unstable.

# 3.3 並列化 DC/DC コンバータ

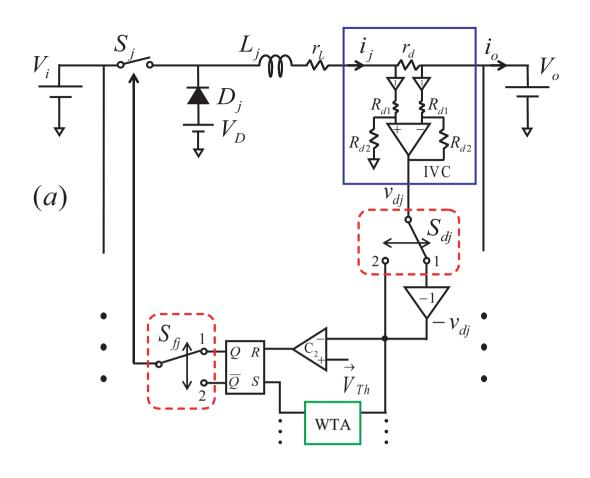

# 3.3.1 回路モデルと基本動作

図 3.8 (a) に並列化 DC/DC コンバータ (PDCs) の回路モデルを示す: N 個 ( $N \ge 2$ ) の単体の Buck コンバータが並列に接続されており、出力電流は各々のコンバータに流れる電流の総和  $i_o \equiv \sum_{j=1}^N i_j$  である。これは 2 章の図 2.1 (a) のモデルにおいて、全ての入力が等しい場合の系に対応する。同系についてもスイッチ  $S_j$  とダイオード  $D_j$  により、State 1 から State 3 の 3 つの状態をとる。同系は単体の系と同様に 2 つのスイッチングルールをもつ。Rule 1 では State 1 へのスイッチングに WTA を適応する。

#### Rule 1:

State 1  $\rightarrow$  State 2 if  $i_j = J_+$ State 2  $\rightarrow$  State 3 if  $i_j = 0$ State 2 or State 3  $\rightarrow$  State 1 if  $i_j = \min$  at t = nT

ここで単体の系と同様、 $J_+$  は上側のしきい値電流であり T はクロックである。State 1 へのスイッチングに WTA を用いる:  $i_j$  はクロック時 T=nt の全てのコンバータの電流  $i_1 \sim i_N$  の中で最小となる電流を選択し、対応するコンバータのスイッチ  $S_j$  を切り替える。

Rule 2 では State 2 へのスイッチングに WTA を適応する。

#### Rule 2:

State 2

$$\rightarrow$$

State 1 if  $i_j = J_- \ge 0$

State 1  $\rightarrow$  State 2 if  $i_j = \max$  at  $t = nT$

ここで  $J_-$  は下側のしきい値電流である。 $State\ 2$  へのスイッチングに WTA を用いる:  $i_j$  はクロック時 T=nt の全てのコンバータの電流  $i_1\sim i_N$  の中で最大となる電流を選択し、対応するコンバータのスイッチ  $S_j$  を切り替える。クロックの周期 T がコンバータの負荷の時定数 RC に比べ非常に小さい場合 (T<< RC)、図 3.8 (a) の様に負荷を定電圧源  $V_o$  として考えることができる [6]。そして回路方程式は以下のようになる:

$$L_{j}\frac{d}{dt}i_{j} = \begin{cases} V_{i} - V_{o} & \text{for State 1} \\ -V_{o} & \text{for State 2} \\ 0 & \text{for State 3} \end{cases}$$

(3.9)

ここで  $V_i > V_o$  である。簡単のために回路における全ての素子は理想的であり、 $L_1 = \cdots = L_N \equiv L$  として考える。以下の無次元化変数とパラメータを導入すると、

$$\tau = \frac{t}{T}, \ x_j = \frac{i_j}{J_+}, \ a = \frac{T}{LJ_+}(V_i - V_o), \ b = \frac{T}{LJ_+}V_o, \ X_- = \frac{J_-}{J_+}$$

(3.10)

回路方程式は以下のように正規化され、スイッチングルールは以下のようになる:

$$\frac{d}{d\tau}x_j = \begin{cases}

a & \text{for State 1} \\

-b & \text{for State 2} \\

0 & \text{for State 3}

\end{cases}$$

(3.11)

#### Rule 1:

State 1  $\rightarrow$  State 2 if  $x_i = 1$

State 2  $\rightarrow$  State 3 if  $x_i = 0$

State 2 or State 3  $\rightarrow$  State 1 if  $x_i = \min at \tau = n$

#### Rule 2:

State 2  $\rightarrow$  State 1 if  $x_i = X_-$

State 1  $\rightarrow$  State 2 if  $x_i = \max at \tau = n$

単体と同様に回路のパラメータは3つの無次元のパラメータ $a, b, X_-$ に統合される。

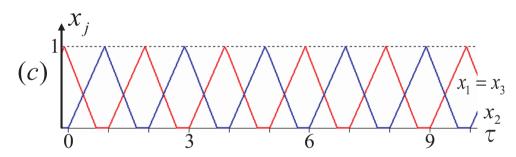

図 3.9 に PDCs の典型的な出力波形を示す (N=3)。 Rule 1 では図 3.9 (a) に示されるように、WTA は自動的に安定な N-SYN を実現できる。パラメータを変化させると、3-SYN は図 3.9 (b) のような不安定な 3-SYN になり、これは回路実験では観測できない。ここで Rule 2 を適用すると、不安定な 3-SYN は図 3.9 (b') のような安定な 3-SYN となる。このように並列化システムにおいても、2 つのスイッチングルールを適切に切り替えることで系の安定化を図れる。図 3.9 (c) は Rule 1 での DCM の 3-SYN である: これは初期値に対しては超安定であり過渡状態はとても短いが、リップルは大きくなる。この DCM については文献 [23] で議論されている。ここで Rule 2 を適用すると、DCM での安定な 3-SYN は図 3.9 (c') のような CCM での安定な 3-SYN となる。次章で 1-SYN の安定性について言及する。

図 3.8: 並列化 DC/DC コンバータとスイッチングルール.

- (a) 並列化 Buck コンバータの回路モデル  $(0 < V_o < V_i)$ .

- (b) Rule 1 のスイッチングルール.

- (c) Rule 2 のスイッチングルール.

図 3.9: PDCs の典型的な波形 (N=3).

(a) Stable 3-SYN in CCM in Strategy 1 for  $(a^{-1}, b^{-1}) = (1.32, 2.13)$   $(R_p = 0.154)$ . (b) Unstable 3-SYN in CCM in Strategy 1 for  $(a^{-1}, b^{-1}) = (3.70, 1.67)$   $(R_p = 0.054)$ . (c) Stable 3-SYN in DCM in Strategy 1 for  $(a^{-1}, b^{-1}) = (1.32, 1.20)$   $(R_p = 0.218)$ . (b') Stable 3-SYN in CCM in Strategy 2 for  $(a^{-1}, b^{-1}) = (3.70, 1.67)$ ,  $X_- = 0.441$   $(R_p = 0.054)$ . (c') Stable 3-SYN in CCM in Strategy 2 for  $(a^{-1}, b^{-1}) = (1.32, 1.20)$ ,  $X_- = 0$   $(R_p = 0.389)$ .

# 3.3.2 多相同期 (N-SYN) の安定性

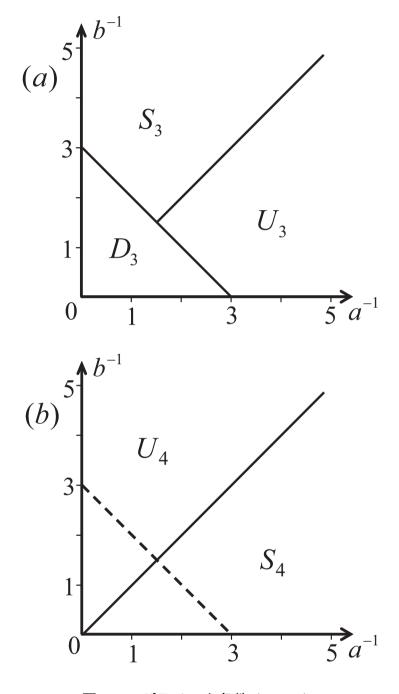

この章ではパラメータに対する CCM での N-SYN の存在と、その安定性について考える。図 3.9 と 図 3.2 をみると、CCM での N-SYN では  $x_j$  の出力波形は単体の系の x の CCM での周期的な軌道と似ている。N-SYN に対して  $\tau$  を  $\tau/N$  と替えると、図 3.12 に示されるように並列化システム  $x_j$  の波形は単体の x の波形と一致する。この変換はパラメータ (a,b) を (Na,Nb) に替えるのと等価であるので、単体の系での式 3.7 と 3.8 のパラメータ領域は、並列化システムにおける N-SYN のパラメータ領域に変形することができる。Rule 1 においては次のように変形される (図 3.11 (a)):

$$S_{3} \equiv \{(a,b) | a^{-1} + b^{-1} > N, a^{-1} < b^{-1} \}$$

$$U_{3} \equiv \{(a,b) | a^{-1} + b^{-1} > N, a^{-1} > b^{-1} \}$$

$$D_{3} \equiv \{(a,b) | a^{-1} + b^{-1} < N \}$$

$$(3.12)$$

ここで  $S_3$  では N-SYN は安定であり、 $U_3$  では不安定である。WTA Switching は自動的に位相のシフトを実現する。小さな摂動に対する N-SYN の安定性は、単体の系における位相マップの不動点の安定性と同じ原理で確かめられる。 $D_3$  では DCM であり、2 章や文献 [32] で議論したような様々な超安定現象を呈する。

Rule 2 においてはパラメータ領域は次のように変形される (図 3.11 (b)):

$$S_4 \equiv \{(a,b) | a^{-1} > b^{-1} \}$$

$$U_4 \equiv \{(a,b) | a^{-1} < b^{-1} \}$$

(3.13)

ここで  $S_4$  では N-SYN は安定であり、 $U_4$  では不安定であり Hyperchaos を呈する。  $a^{-1}+b^{-1}=N$  の状態は N-SYN の振幅が 1 であることを意味する。また  $X_-=1-\frac{N}{a^{-1}+b^{-1}}\geq 0$  ならば頂点は  $X_{max}=1$  である。式 3.10 について言及すると、 $a^{-1}+b^{-1}>N$  というのは  $LJ_+V_i/(V_o(V_i-V_o))>NT$  であるのと等価である。この領域では、CCM で頂点が  $X_{max}=1$  である安定な N-SYN は Rule の切り替えやパラメータを調整することで常に可能である: T や  $J_-$  の調整で  $a^{-1}< b^{-1}$  では Rule 1 を、 $a^{-1}< b^{-1}$  では Rule 2 を用いる。

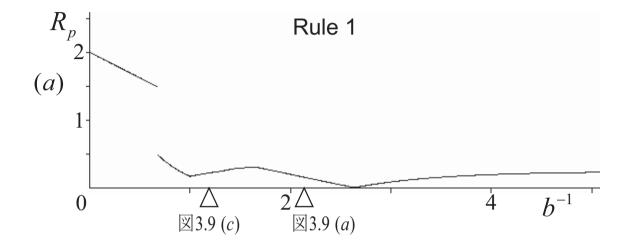

図 2.4 に無次元の出力電流  $x_o$  のリップル特性を示す。 $\mathrm{Rule}\ 1$  ではリップル  $R_p$  は小さく、 $S_3$  の領域で  $a^{-1}=(N-1)b^{-1}$  のとき最適値  $R_p=0$  となる。 $b^{-1}$  を小さくする

と  $R_p$  は大きな値へとぶ。 $Rule\ 2$  では  $a^{-1}$  が  $b^{-1}$  を越えると  $R_p$  は小さくなり、 $S_4$  の領域で  $(N-1)a^{-1}=b^{-1}$  のとき最適値  $R_p=0$  となる。このように CCM での安定な N-SYN は、DCM での動作や不安定な N-SYN に比べリップルが小さくなることがわかる。次章ではこれらの動作を回路実験により確認する。

図 3.10: 周期軌道の相似形. (a) Periondic orbit in the sigle system. (b) N-SYN in the parallel system (N=3).

図 3.11: パラメータ条件 (N=3).

(a) Rule 1.  $S_3$ : stable N-SYN in CCM,  $U_3$ : unstable N-SYN in CCM,  $D_3$ : DCM. (b) Rule 2.  $S_4$ : stable N-SYN in CCM,  $U_4$ : unstable N-SYN in CCM.

図 3.12: リップル特性 (N=3). (a) Rule 1 for  $a^{-1}=1.32$ . (b) Rule 2 for  $b^{-1}=1.67$ .

### 3.4 回路実験

この章では単体と並列化のそれぞれの系において PWC モデルを用いて回路実験を行い、呈する現象を確認する。

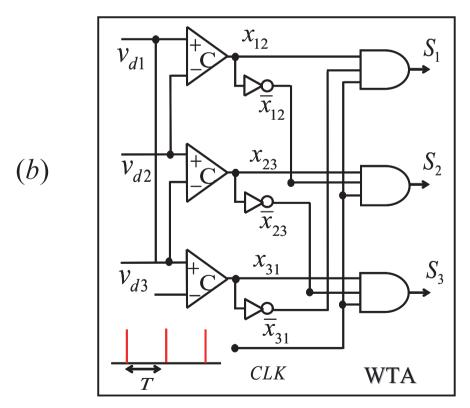

## 3.4.1 単体の Buck コンバータ

図 3.13 に示されるような Buck コンバータに基づく PWC モデルにおいて回路を実装し、系の呈する現象を確認する。図中の青い四角で囲まれている部分は電流-電圧変換回路 (Current-to-Voltage Conversion module: IVC) である。インダクタ電流 i を測定するために、小さい抵抗  $r_d$  を挿入し、IVC の入力側の抵抗  $R_{d1}$  を十分に大きくする。インダクタ電流 i は式 3.14 により、電圧  $v_d$  に変換される。

$$v_d = (R_{d2}/R_{d1})r_d i (3.14)$$

接点電圧  $v_d$  はコンパレータ (Comparator) にかかり、その出力電圧はフリップフロップ (Flip-Flop) のリセット (Reset) 端子へかかる。周期 T のクロック信号はフリップフロップのセット (Set) 端子へとかかり、その出力がスイッチ S を制御する。 $r_L$  はインダクタの内部抵抗である。図中の赤い四角は Rule を切り替えるスイッチであり、Rule 1 を適用する場合は  $S_d$ ,  $S_f$  を端子 1 に接続し、Rule 2 を適用する場合は  $S_d$ ,  $S_f$  を端子 2 に接続することで Rule の切り替えが可能である。

図 3.14 に Buck コンバータの観測波形を示す。  $Rule\ 1$  では図 3.7 (a) の  $S_1$  の領域では、図 3.14 (a) のように CCM での安定な周期軌道である。パラメータを図 3.7 (a) の  $U_1$  の領域に変えると、図 3.14 (b) のようにカオスへと変わる。この場合  $Rule\ 2$  を適用すると、図 3.7 (b) の  $S_2$  の領域となるので、図 3.14 (b') のように CCM での安定な周期軌道となる。このようにパラメータ a,b に対して適切に Rule を切り替えることで、幅広 N パラメータ領域で安定な出力を得ることができる。また  $Rule\ 1$  で図 3.14 (c) のような DCM での安定な周期軌道に対して  $Rule\ 2$  を適用すると、図 3.14 (c') のような CCM での安定な周期軌道となる。

図 3.13: Buck コンバータの実験回路. 回路素子: 071 ( IVC ), LM339 ( Comparator ), 4066 ( Switch ), 4013 ( Flip-Flop ).

図 3.14: Buck コンバータの観測波形.

### 3.4.2 並列化 Buck コンバータ

図 3.15 に示されるような並列化 Buck コンバータに基づく PWC モデルにおいて回路を実装し、系の呈する現象を確認する。N=3 の系において実験を行う。この実験では各コンバータのインダクタは全て等しい  $(L_j=L)$ 。単体の系と同様に IVC を用いて電流-電圧変換を行っている。各々のコンバータにおいて、インダクタ電流  $i_j$  は式3.15 により、電圧  $v_{dj}$  に変換される。

$$v_{di} = (R_{d2}/R_{d1})r_d i_i (3.15)$$

接点電圧  $v_{dj}$  はコンパレータと WTA 回路にかかる。図 3.15 (a) 中の緑の四角で囲まれた部分が WTA 回路である。この回路では各コンバータの接点電圧  $v_{dj}$  をそれぞれリーグ戦の要領で比較し、"Winner" を選択する。よってその組み合わせは  ${}_{n}C_{2}$  通りなので、 $\frac{n(n-1)}{2}$  個のコンパレータ、 $\frac{n(n-1)}{2}$  個の Inverting converter、n 個の AND ゲートにより構成される。N=3 の場合を図 3.15 (b) に示す。WTA 回路の出力はクロック T 毎にサンプルされ、各コンバータのフリップフロップのセット端子にかかる。一方コンパレータ  $C_{2}$  の出力は各コンバータのフリップフロップのリセット端子にかかる。各コンバータのフリップフロップの出力はそれぞれのスイッチ  $S_{1}$  から  $S_{N}$  を制御する。単体での実験回路と同様に、Rule 1 を適用する場合は  $S_{dj}$ ,  $S_{fj}$  を端子 1 に接続し、Rule 2 を適用する場合は  $S_{dj}$ ,  $S_{fj}$  を端子 2 に接続することで Rule の切り替えが可能である。

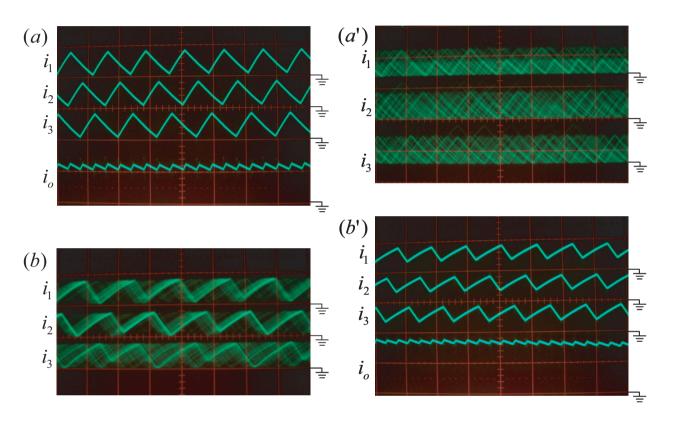

図 3.16 に並列化 Buck コンバータ (N=3) の観測波形を示す。 $Rule\ 1$  では図 3.11 (a) の  $S_3$  の領域では、図 3.16 (a) のような CCM での安定な 3-SYN を呈する。このような 3-SYN ではリップルは小さい。パラメータを図 3.11 (a) の  $U_3$  の領域に変えると、図 3.16 (b) のように不安定な 3-SYN となり、これは Hyperchaos である。この場合  $S_{dj}$  と  $S_{fj}$  のスイッチを 1 端子から 2 端子へ切り替えると  $Rule\ 1$  から  $Rule\ 2$  へと切り替わり、Hyperchaos は図 3.16 (b) に示されるようなリップルの小さい CCM で安定な 3-SYN へと変わる。このように並列化のシステムにおいてもパラメータ a,b に

対して適切に Rule を切り替えることで、幅広いパラメータ領域で安定な出力を得ることができる。

図 3.15: 並列化 Buck コンバータの実験回路.

(a) Parallel system where N=3. (b) WTA circuit: 071 ( IVC ), LM339 ( Comparator ), 4066 ( Switch ), 4013 ( Flip-Flop ), 4049 ( Inverting Converter ), 4082 ( AND Gate ).

図 3.16: 並列化 Buck コンバータの観測波形 (N = 3).

$L \doteq 100 [\mathrm{mA}], \ r_L \doteq 100 [\Omega], \ r_d \doteq 91 [\Omega] \ \text{and} \ R_{d1} = R_{d2} \doteq 10 [k\Omega]. \ \text{Horizontal:} \ 0.2 \mathrm{ms/div},$  Vertical:  $5 \mathrm{mA/div}.$  (a) 3-SYN in CCM in Rule 1 for  $(a^{-1}, b^{-1}) = (1.14, 2.39). \ V_i \doteq 6.88 [\mathrm{V}],$   $V_o \doteq 2.22 [\mathrm{V}], \ V_{Th} \doteq -0.40 [\mathrm{V}], \ T \doteq 0.08 [\mathrm{ms}], \ J_+ \doteq 4.40 [\mathrm{mA}].$  (b) Hyperchaos in Rule 1 for  $(a^{-1}, b^{-1}) = (2.36, 1.54). \ V_i \doteq 5.69 [\mathrm{V}], \ V_o \doteq 3.44 [\mathrm{V}], \ V_{Th} \doteq -0.40 [\mathrm{V}], \ T \doteq 0.08 [\mathrm{ms}],$   $J_+ \doteq 4.40 [\mathrm{mA}].$  (a') Hyperchaos in Rule 2 for  $(a^{-1}, b^{-1}) = (1.11, 2.51). \ V_i \doteq 6.88 [\mathrm{V}],$   $V_o \doteq 2.12 [\mathrm{V}], \ V_{Th} \doteq 0 [\mathrm{V}], \ T \doteq 0.08 [\mathrm{ms}], \ J_- \doteq 0 [\mathrm{mA}].$  (b') 3-SYN in CCM in Rule 2 for  $(a^{-1}, b^{-1}) = (2.57, 1.46). \ V_i \doteq 5.69 [\mathrm{V}], \ V_o \doteq 3.63 [\mathrm{V}], \ V_{Th} \doteq 0.17 [\mathrm{V}], \ T \doteq 0.08 [\mathrm{ms}],$   $J_- \doteq 1.87 [\mathrm{mA}].$

### 3.5 むすび

本章では幅広いパラメータ領域において、安定動作を実現するために2つのスイッチングルールを適用したシステムについて言及した。単体の系については1次元の位相マップを導出し、呈する現象の解析に有効であることを示した。そしてそれぞれのRule において、パラメータに対する不動点の安定性やカオス的な動作をする領域を明らかにした。並列な系についてはN=3の場合において考察した。単体の系と同様にそれぞれのRule において、パラメータに対する3-SYN の安定性や Hyperchaos となる領域を明らかにした。またリップル特性から、Rule 1 では $a^{-1}=(N-1)b^{-1}$  のときに、Rule 2 では $(N-1)a^{-1}=b^{-1}$  のときに"ゼロリップル $R_p=0$  "を実現できることを示した。回路実験により典型的な現象を確認し、適切にRule を切り替えることで幅広いパラメータ領域での安定な動作が可能であることを示した。

今後の課題は、安定化に有効な様々なスイッチングルール則の提案、パラメータや Rule の自動的な調整、多入力系への適用、実用的な回路設計、分岐現象の解析等が挙 げられる。

# 第4章 結論

本修士論文では、並列化 DC/DC コンバータ (PDCs) の呈する現象解析とその安定 化について述べた。主に2章では系の呈する非線形現象の解析を、3章では2スイッチ ングルールを用いた系の安定化について言及し、以下にそれぞれのまとめと今後の課 題を示す。

2章では、非線形力学系である一入力/多入力系 PDCs の PWC モデルにおいて、系の呈する現象を調べた。位相制御には WTA Switching を適用した。この系は多相同期 (N-SYN) やカオス、Hyperchaos、複雑な超安定現象といった様々な非線形現象を呈する。これらの解析に Hybrid Return Map を導出した。N=3 の系においてパラメータを変化させると HRM は様々な形となり、それに応じて多彩な現象を呈した: 一入力系では安定な N-SYN から CCM での Hyperchaos へと変わる。多入力系においては CCM の分岐では、安定な N-SYN はカオスへと変わる。また DCM の分岐では、安定な N-SYN はカオスへと変わる。また DCM の分岐では、安定な N-SYN はカオスへと変わり、さらに複雑な超安定周期解 (SSPOs) に変わる。このように 1 つの入力を変え、対応するコンバータが不安定な動作をすると、WTA Switching により影響を受け、他のコンバータも不安定な現象へと変わり多彩な現象を引き起こす。これらの結果は実際の回路設計や新しい分岐理論の発展に対する重要な情報となると考えられる。

- 2章の内容について、今後の課題を以下に挙げる。

- ・詳細な分岐現象の解析

- ・PWC モデルと RC 負荷を用いた実際のモデルとの比較

- ・多入力系の回路実験

3章では、2章で示されるような不安定な振る舞いに対して、幅広いパラメータ領域での安定な動作を実現するために、2つのスイッチングルールを適用したシステムについて言及した。単体の系については1次元の位相マップを導出し、現象の解析に有効であることを示した。そしてそれぞれの Rule において分岐現象を示し、パラメータに対する不動点の安定性を明らかにした。並列な系については、それぞれの Rule においてパラメータに対する N-SYN の安定性を明らかにした。またリップル特性から、それぞれの Rule において"ゼロリップル"となるパラメータを示した。単体と並列な系において回路実験を行い、典型的な現象を確認した。これらの結果から、適切に Rule を切り替えることで、幅広いパラメータ領域でリップルの少ない安定した動作が実現可能である言える。

- 3章の内容について、今後の課題を以下に挙げる。

- ・安定化に有効な様々なスイッチングルール則の提案

- ・パラメータや Rule の自動的な調整

- ・多入力系への適用

- ・実用的な回路設計

- ・詳細な分岐現象の解析

# 参考文献

- [1] S. Banerjee and G. C. Verghese, eds., Nonlinear Phenomena in Power Electronics: Attractors, Bifurcations, Chaos, and Nonlinear Control, IEEE Press, 2001.

- [2] T. Saito, H. Torikai and W. Schwarz, Switched dynamical systems with double periodic inputs: an analysis tool and its application to the buck-boost converter, IEEE Trans. Circuits Syst. I, 47, pp.1038–1046, 2000.

- [3] C. K. Tse and M. di Bernardo, Complex behavior in switching power converters, Proc. IEEE, 90, pp. 768–781, 2002.

- [4] Z. T. Zhusubaliyev and E. Mosekilde, Torus birth bifurcations in a dc/dc Converter, IEEE Trans. Circuits Systs. I, 53, 8, pp. 1839–1850, 2006.

- [5] S. Banerjee and K. Chakrabarty, Nonlinear modeling and bifurcations in the boost converter, IEEE Trans. Power Electron., 13, 2, pp. 252–260, 1998.

- [6] T. Kabe, S. Parui, H. Torikai, S. Banerjee and T. Saito, Analysis of Current Mode Controlled DC-DC Converters through Piecewise Linear Models, IEICE Trans. Fundamentals, E90-A, 2, pp. 448–456, 2007.

- [7] C. Chang, M. K. Knights, Interleaving technique in distributed power conversion systems, IEEE Trans. Circuits Systs. I, 42, pp. 245–251, 1995.

- [8] X. Zhou, P. Xu and F. C. Lee, A novel current-sharing control technique for low-voltage high-current voltage regulator module applications, IEEE Trans. Power Electron., 15, 6, pp. 1153–1162, 2000.

- [9] J. H. B. Deane, P. Ashwin, D. C. Hamill and D. J. Jeffries, Calculation of the periodic spectral components in a chaotic DC-DC converter, IEEE Trans. Circuits Systs. I, 46, pp.1313–1319, 1999.

- [10] C. K. Tse, Flip bifurcation and chaos in three-state boost switching regulators, IEEE Trans. Circuits Systs. I, 41, pp. 16–23, 1994.

- [11] D. C. Hamill and D. J. Jeffries, Subharmonics and chaos in a controlled switched-mode power converter, IEEE Trans. Circuits Systs. I, 35, pp. 1059–1061, 1988.

- [12] S. Parui and S. Banerjee, Bifurcations due to transition from continuous conduction mode to discontinuous conduction mode in the boost converter, IEEE Trans. Circuits Systs. I, 50, 11, pp. 1464–1469, 2003.

- [13] D. C. Hamill, J. H. B. Deane and D. J. Jeffries, Modeling of chaotic dc-dc converters by iterated nonlinear mappings, IEEE Trans. Power Electron., 7, pp. 25–36, 1992.

- [14] T. Saito, T. Kabe, Y. Ishikawa, Y. Matsuoka and H. Torikai, Piecewise constant switched dynamical systems in power electronics, Int'l J. of Bifurcation and Chaos, 17, 10, 2007.

- [15] Y. Matsuoka and T. Saito, A Simple Chaotic Spiking Oscillator Having Piecewise Constant Characteristics, IEICE Trans. Fundamentals, E89-A, 9, pp. 2437–2440, 2006

- [16] T.Tsubone and T.Saito, Manifold piecewise constant systems and chaos, IEICE Trans. Fundamentals, E82-A, 8, pp.1619–1626, 1999

- [17] R. Ayyanar, R. Giri and N. Mohan, Active input-voltage and load-current sharing in input-series and output-parallel connected modular dc-dc converters using

- dynamic input-voltage reference scheme, IEEE Trans. Power Electron., 19, pp. 1462–1473, 2004.

- [18] D. K-W. Cheng, Y-S. Lee and Y. Chen, A current-sharing interface circuit with new current-sharing technique, IEEE Trans. Power Electron., 20, 1, pp. 35–43, 2005.

- [19] R. Giral, L. Martinez-Salamero, R. Leyva and J. Maixe, Sliding-mode control of interleaved boost converters, IEEE Trans. Circuits Systs. I, 47, pp. 1330–1339, 2000.

- [20] R. Giral and L. Murtinez-Salamero, Interleaved converters operation based on CMC, IEEE Trans. Power Electron., 14, 4, pp. 643–652, 1999.

- [21] S. K. Mazumder, M. Tahir and S. L. Kamisetty, Wireless PWM control of a parallel DC/DC buck converter, IEEE Trans. Power Electron., 20, 6, pp. 1280–1286, 2005.

- [22] H. H. C. Iu and C. K. Tse, Bifurcation behavior in parallel-connected buck converters, IEEE Trans. Circuits Systs. I, 48, pp. 233–240, 2001.

- [23] T. Saito, S. Tasaki and H. Torikai, Interleaved buck converters based on winner-take-all switching, IEEE Trans. Circuits Syst. I, 52, 8, pp. 1666–1672, 2005.

- [24] J. Abu-Qahouq, H. Mao, and I. Batarseh, Multiphase voltage-mode hysteretic controlled dc-dc converter with novel current sharing, IEEE Trans. Power Electron., 19, 1, pp. 1397–1407, 2004.

- [25] T. Kohonen, Self-organized formation of topologically correct feature maps, Biol. Cybern. 43, pp. 59–69, 1982.

- [26] H. Torikai, T. Saito and W. Schwarz, Synchronization via multiplex pulse-train, IEEE Trans. Circuits Syst. I, 46, pp. 1072–1085, 1999.

- [27] H. Matsuo, W. Lin, F. Kurokawa T. Shigemizu and N. Watanabe, Characteristics of the Multiple-Input DC-DC Converter, IEEE Trans, Ind. Electron., 51, 3, pp. 625–631, 2004.

- [28] K. Kobayashi, H. Matsuo and Y. Sekine, Novel Solar-Cell Power Supply System Using a Multiple-Input DC-DC Converter, IEEE Trans. Ind. Electron., 53, 1, pp. 281–286, 2006.

- [29] K. Jin and X. Ruan, Hybrid full-bridge three-level LLC resonant converter—a novel DC-DC converter suitable for fuel-cell power system, IEEE Trans. Ind. Electron., 53, 5, pp. 1492–1503, 2006.

- [30] L. Solero, A. Lidozzi and J. A. Pomilio, Design of multiple-input power converter for hybrid vehicles, IEEE Trans. Power Electron., 20, 5, pp. 1007–1016, 2005.

- [31] Y. Ishikawa and T. Saito, Bifurcation of multiple-input parallel dc-dc converters with dynamic winner-take-all switching, Proc. IEEE/ISCAS, pp. 789–792, 2007.

- [32] Y. Ishikawa and T. Saito, Synchronization and Chaos in Multiple-Input Parallel DC-DC Converters with WTA Switching, IEICE Trans. Fundamentals, E90-A, 6, pp. 1162–1169, 2007.

- [33] Y. Ishikawa, T. Saito and Y. Matsuoka, Rich dynamics of paralleled dc-dc converters, Proc. NDES, pp. 61–64, 2006.

- [34] Y. Ishikawa and T. Saito, WTA-based Switching Strategy for Paralleled DC-DC Converters, Proc. of NOLTA, pp. 152–155, 2007.

- [35] Y. Ishige, Y. Ishikawa and T. Saito, Bifurcation of simple switched dynamical systems based on power converters, Proc. of NOLTA, pp. 156–159, 2007.

- [36] T.Tsubone and T.Saito, Hyperchaos from a 4-D manifold piecewise linear system, IEEE Trans. Circuit Syst. I, 45, 9, pp. 889–894, 1998.

[37] A. Lasota and M. C. Mackey, Chaos, Fractals, and Noise, second ed., Springer-Verlag, 1994.

# 研究業績

#### (原著論文)

Y. Ishikawa, D. Kimura, Y. Ishige and T. Saito, "Analysis of Simple Switched Dynamical Systems Based on Single/Parallel DC-DC Converters," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences. (submitted)

T. Saito, T. Kabe, <u>Y. Ishikawa</u>, Y. Matsuoka and H. Torikai, "Piecewise constant switched dynamical systems in power electronics," International Journal of Bifurcation and Chaos, 17, 10, pp. 3373-3386, 2007.

Y. Ishikawa and T. Saito, "Synchronization and Chaos in Multiple-Input parallel DC-DC Converters with WTA Switching," IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, vol. E-90-A, no.6, pp. 1162-1169, 2007.

### (国際会議)

Y. Ishikawa and T. Saito, "WTA-based Switching Strategy for Paralleled DC-DC Converters," Proc. of 2007 International Symposium on Nonlinear Theory and its Applications (NOLTA '07, Vancouver, Canada), pp. 152-155, 2007.

Y. Ishige, <u>Y. Ishikawa</u> and T. Saito, "Bifurcation of Simple Switched Dynamical Systems based on Power Converters," Proc. of 2007 International Symposium on Nonlinear Theory and its Applications (NOLTA '07, Vancouver, Canada), pp. 156-159, 2007.

Y. Ishikawa and T. Saito, "Bifurcation of multiple-input parallel dc-dc converters with dynamic winner-take-all switching," Proc. of 2007 IEEE International Symposium on Circuits and Systems (ISCAS '07, New Orleans, USA), pp. 789-792, 2007.

Y. Ishikawa, T. Saito and Y. Matsuoka, "Rich Dynamics of Paralleled DC-DC Converters," Proc. of 2006 Nonlinear Dynamics of Electronic Systems (NDES '06, Dijon, France), pp. 61-64, 2006.

### (国内発表)

木村大祐、石川裕己、斎藤利通 "並列化 Buck コンバータに基づく区分定数モデルの安定性について、"第 21 回 回路とシステム軽井沢ワークショップ. (submitted)

石毛保秀、石川裕己、斎藤利通 "AC-DC コンバータのスイッチング則について," 第 21 回 回路とシステム軽井沢ワークショップ. (submitted)

木村大祐、石川裕己、石毛保秀、斎藤利通 "DC-DC コンバータに基づくスイッチ力学系の解析," 電子情報通信学会技術研究報告, 東京, EE2007-36.

石毛保秀、<u>石川裕己</u>、斎藤利通 "ブーストパワーコンバータの簡略化モデルの解析," 電子情報通信学会技術研究報告, 静岡、NLP2007-58.

木村大祐、<u>石川裕己</u>、石毛保秀、斎藤利通 "DC/DC コンバータのスイッチングルール 多様化へのアプローチ," 電子情報通信学会ソサイエティ大会, 鳥取, 2007年 9月, A-2-9.

石毛保秀、<u>石川裕己</u>、斎藤利通 "AC-DC コンバータの分岐現象について," 電子情報通信学会技術研究報告, 香川, NLP2006-119.

石川裕己、斎藤利通、松岡祐介 "WTA に基づく並列化 DC/DC コンバータの構造安定性について、"電子情報通信学会技術研究報告、東京、NLP2006-11.

石川裕己、松岡祐介、斎藤利通 "並列化 Buck コンバータのリターンマップによる解析," 第 19 回 回路とシステム軽井沢ワークショップ, pp. 325-329, 2006.

石川裕己、松岡祐介、斎藤利通、鳥飼弘幸 "WTA に基づく並列化パワーコンバータの実装について," 電子情報通信学会ソサイエティ大会, 札幌, 2005 年 9 月, A-2-9.

### 謝辞

本修士論文は著者が法政大学大学院工学研究科電気工学専攻に在学中に行ったものである。この研究は同大学工学部情報電気電子工学科 斎藤利通教授の指導下で行ったもので、全ての研究活動を遂行するにあたり同教授から大変御参考になる御指導・御鞭撻を沢山賜りました。ここに心から深謝いたします。また大阪大学大学院基礎工学研究科 鳥飼弘幸准教授には研究を行ったこの2年間にわたり、さまざまな貴重な御助言・御指摘を賜りました。ここに心より深く感謝いたします。

また研究活動中に貴重な御助言・御討論を賜りました武蔵工業大学工学部コンピュータ・メディア工学科教授 宮内新教授、同大学工学部コンピュータ・メディア工学科助手 中野秀洋専任講師には感謝の意を表明いたします。

最後に法政大学工学部情報電気電子工学科 斎藤利通研究室の皆様にはいろいろな有益な御討論・ご助言を戴きました。ここに感謝の意を表します。特に同研究室 石毛保 秀君、木村大祐君には実験の履行の際、ご協力の頂戴に改めて感謝致します。